反激式 DC-DC 轉換器拓撲結構可顯著節省多個輸出電源的成本和空間,這些電源具有高達 100W 的高輸出電壓。反激式拓撲使用變壓器存儲和傳輸能量,由于物理限制,變壓器在開關周期內會導致較大的電壓瞬態尖峰。本文概述了可用于抑制初級側和次級側的這些瞬變的耗散電壓抑制電路(電壓緩沖器)的設計。

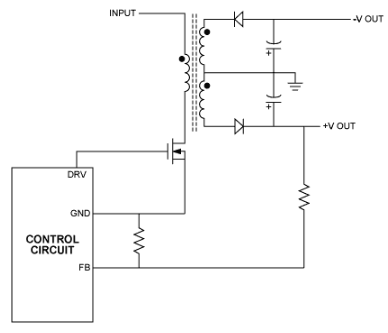

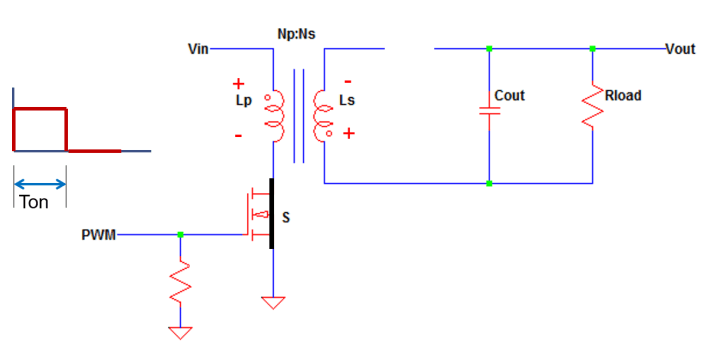

反激式拓撲(圖 1A)可為具有高輸出電壓的多個輸出電源節省大量成本和空間,功率水平高達 100W。這種拓撲使用變壓器,變壓器本質上是一個耦合電感器,在同一磁芯上有多個繞組。反激式拓撲的工作原理是在電源開關導通期間將能量存儲在變壓器中,并在關斷期間將該能量傳輸到輸出。能量存儲在與變壓器鐵芯串聯的非磁性間隙中。實際上,由于繞組之間的物理分離,多個繞組不能都同樣很好地耦合到磁芯。少量能量也存儲在這些繞組內部和之間。該能量在電路中表示為漏感(圖 1B)。

圖 1A.反激式電路的基本拓撲結構。

圖 1B.等效變壓器模型。

反激式拓撲對于多個輸出電源很有吸引力,因為輸出電壓會隨著線路和負載的變化而相互跟蹤,并且向系統添加輸出不需要額外的IC。盡管有其優點,但反激式的缺點是電源開關漏極和次級整流器處的瞬態電壓尖峰較大。這些尖峰是反激式變壓器漏感的函數。緩沖器控制漏感的影響,提高電源的可靠性。

緩沖器可以是被動網絡,也可以是主動網絡。無源緩沖器網絡元件僅限于電阻器、電容器、電感器和二極管。無源緩沖器可以控制電壓或電流,可以是耗散的,也可以是非耗散的。如果緩沖器中的能量在電阻元件中耗散,則將其歸類為耗散緩沖器,但如果能量返回到輸入或向前移動到輸出,則將其歸類為非耗散。本應用筆記概述了所使用的不同類型的無源耗散電壓緩沖器、設計指南及其各種限制。特別是,討論了用于減少開關應力和提高反激式拓撲效率的緩沖器。

第一部分列舉了反激式轉換器初級側需要緩沖器。第二部分解釋了輸出側需要緩沖器。接下來將討論各種類型的耗散電壓緩沖器。

初級漏感和 MOSFET 開關

初級漏感LLP在飛返中不參與一次到二次能量的轉移,因此對效率有負面影響。由于漏感找不到開關導通期間積聚電流的路徑,因此在MOSFET關斷時會導致電壓尖峰,并且還會延遲功率從初級到次級的傳輸。變壓器和開關中的寄生元件決定了該電壓尖峰的大小。在高輸出電壓下,電路寄生效應相對于輸出功率量變大。

初級漏感,LLP,以及變壓器中的初級繞組電容,CP,輸出電容C開放源碼軟件,MOSFET形成寄生LC網絡。峰值電壓由下式給出:

VPEAK = IP (√(LLP/(CP+COSS))) + VIN + VOUT/N

其中IP是 MOSFET 關斷時循環的電流電平,N 是次級匝數與初級匝數的比率,V在為輸入電壓,V外是輸出電壓。

上式中的平方根項表示寄生LC網絡的特性阻抗。請注意,當切換最高電流水平時,會發生最高電壓瞬變。這種電壓過沖可能導致MOSFET中的功率耗散過大,即使它在器件的安全工作限值內,也會降低總效率。此外,由于瞬態電壓尖峰導致 (dv/dt) 引起的 MOSFET 雜散導通,它可能會導致環路不穩定。

次級漏感和整流二極管

變壓器次級漏感可能與反向恢復電流I娛樂的輸出整流二極管在二極管關閉時引起振鈴。變壓器二次漏感LLS和電容CD的整流器確定此諧振頻率。振鈴可能會產生明顯的輻射和傳導噪聲。諧振電路中的損耗通常很小,因此該網絡在尖峰之后會導致許多振鈴周期。因此,振鈴會影響控制器在反激式配置中使用的電流檢測信號。這種振鈴引起的過沖可能會超過二極管額定電壓并損壞二極管。整流器兩端的最大正電壓可以估算為

V峰值,S= I娛樂√(LLS/CD)+ V在× N

諧振電路的阻尼應進行優化,因為過度阻尼也會導致開關時間增加并導致損耗增加。

因此,可以使用緩沖器來箝位電壓尖峰或抑制振鈴,以降低系統中的噪聲,或兩者兼而有之。根據緩沖器執行的功能,它可以大致分為三類:

上升速率控制緩沖器

電壓鉗緩沖器

阻尼緩沖器

根據定義,阻尼緩沖器是耗散的。上升速率控制緩沖器和電壓鉗位緩沖器可以是耗散的,也可以是非耗散的。非耗散型緩沖器一般為諧振型緩沖器。緩沖器也可以分為極化或非極化,具體取決于能量是在開關邊沿還是在兩個開關邊沿移入或移出緩沖器。極化緩沖器不太擅長阻尼,因為它在大部分周期中都不活躍。它通常提供上升速率控制或箝位。根據被控制的參數是電壓還是電流,這些緩沖器可以進一步分類為電壓或電流緩沖器。本應用筆記僅討論耗散型電壓緩沖器。

RCD 電壓緩沖器

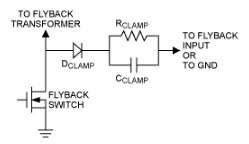

該緩沖器適用于上升速率電壓控制和/或箝位。二極管在配置中的存在使其成為極化緩沖器。該電阻-電容-二極管(RCD)緩沖器的兩種可能配置如圖2所示。圖2A所示的配置只能用作電壓鉗位。圖2B所示的變化適用于上升速率控制或開關漏極電壓的鉗位。

圖 2A.電壓鉗緩沖器。

圖 2B.上升速率電壓緩沖器。

RCD 夾具

在箝位模式下,緩沖器的目的是在MOSFET漏極關斷期間箝位電壓。并聯RC電路可以返回到地或地以外的電壓(即,如果漏極可以高于輸入電壓,則為輸入電壓),因為這將降低電阻中的功耗。MOSFET開關本身必須在關斷期間維持峰值功耗。電容器的值,C鉗和電阻器,R鉗,基于寄生電感中存儲的能量,因為該能量必須在每個周期內放電到RC網絡中。電容器和電阻兩端的電壓設定箝位電壓 V鉗.MOSFET開關漏極處的關斷波形如圖3所示。

圖3.帶箝位的 MOSFET 關斷波形。

這意味著關斷時箝位中的功耗為

PCLAMP = (1/2) × VCLAMP × ICLAMP × Δt × f

其中,f是開關頻率。

然而

Δt = (LLP × IP)/(VCLAMP - VOUT/N).

箝位中的功耗通過電阻。因此

RCLAMP = [2 × VCLAMP × (VCLAMP - VOUT/N)]/( LLP × IP2 × f)

重要的是最小化紋波,V脈動,疊加在 V 上鉗使 MOSFET 漏極電壓接近箝位電壓。電容器的最小值 C鉗,因此為 C鉗= V鉗/ (V脈動×·鉗×f)。

電容器,C鉗,應具有低ESR和低電感,以處理關斷期間的高峰值電流。箝位的RC時間常數應選擇遠大于MOSFET的開關周期。箝位中使用的串聯二極管應能夠處理峰值電流,并且必須是快速導通型。

RC網絡可以用一個可以處理額定電壓和功耗的齊納二極管代替。然而,由于齊納二極管不是快速開關器件,因此可能仍需要與齊納二極管并聯的電容器來處理高頻電流。請注意,此緩沖器不用于具有鉗位感性負載的拓撲,因為它不會減少振鈴。

上升速率控制RCD緩沖器

當RCD緩沖器用于控制MOSFET漏極的電壓上升速率時,電容器必須在每個周期內完全充電和放電,以便能夠控制漏極電壓的上升速率。因此,緩沖器的RC時間常數應遠小于開關周期(考慮占空比對脈沖寬度的影響)。通常,時間常數應約為 1/10千切換周期。當開關關閉時,電感電流通過緩沖二極管轉移,將電容器充電至供電軌。屆時,預計輸出整流器將導通。

當開關導通時,緩沖電容器將通過緩沖電阻和開關放電。

電容值由IP = C (VC/ tr)

其中 VC= 電容器兩端的電壓和 tr= 電壓的上升時間

然后根據所需的時間常數選擇電阻器。RC時間常數遠小于開關頻率,因此,電阻中的功耗與其值無關。功耗由電容值和開關頻率決定。由于只有一個通過電阻的轉換(放電),電阻中的功耗由P = (CVC2f)/2.

簡單的遙控緩沖器

這可能是使用最廣泛的緩沖器,適用于上升速率控制和阻尼。在電感鉗位拓撲中,仍然存在一些雜散電感,RC緩沖器可用于通過控制漏極電壓的上升速率來降低開關中的峰值功耗。然而,RC緩沖器會在每次電壓轉換期間吸收能量,并可能降低效率。此外,RC 緩沖器還會降低 MOSFET 開關的開關速度。在選擇 R 和 C 的值時必須小心,以優化總體性能。RC緩沖器的主要應用是抑制電路中的寄生振鈴,因為反激式轉換器等配置中的電感未箝位。在這些應用中,電阻值必須接近其要阻尼的寄生諧振電路的特性阻抗。選擇要的緩沖電阻

R = √(Lres/Cres)

其中 L分辨率= 引起諧振的寄生電感,C分辨率= 引起諧振的寄生電容。

緩沖器的RC時間常數與開關周期相比應該很小,但與電壓上升時間相比應該很長。緩沖電容必須大于寄生諧振電容,但要足夠小,以盡量減少緩沖電阻中的耗散。緩沖電容通常選擇至少為寄生諧振電容值的3至4倍。根據緩沖器電容,功耗可以估算為

P = C × (VC)2× f

其中C是緩沖電容,VC是緩沖電容兩端的電壓,f是開關頻率。

注意緩沖器中使用的組件中的寄生效應非常重要,因為這些寄生效應可能導致緩沖器無效。緩沖器中使用的二極管應該能夠處理較大的峰值電流,但平均電流相對較小。印刷電路板布局可能需要為這些二極管提供一些散熱器面積。電容器具有串聯電感,應將其最小化,以避免在電路中引入任何不必要的諧振。一些靜電電容器(陶瓷和聚合物薄膜)提供極低的 ESR 和 ESL 值。電容器可以并聯以降低電路電感。使用這種方法時必須小心。大電容的串聯電感能夠與與之并聯的小電容諧振,產生的諧振電路將具有高Q值。

使用的電阻應具有非常低的電感,以避免過度的過沖和振鈴。避免使用繞線電阻器。布局不應引入雜散電感,尤其是在高電流路徑中。反激式轉換器中使用的變壓器應設計為降低漏感并最大限度地減少過沖和振鈴。然而,變壓器的實際設計超出了本應用筆記的范圍,將在別處討論。

電路中的開關通常是最容易受到抑制的設備。開關也位于反激電路的輸入級。在實踐中,最好的程序是從輸入開始,然后在將緩沖器引入電路時進入輸出級。一旦節點被證明需要緩沖器,則應在選擇類型之前確定緩沖器的用途。

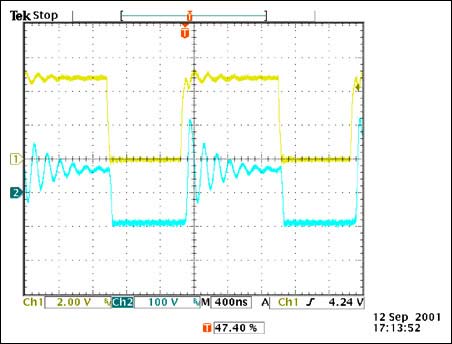

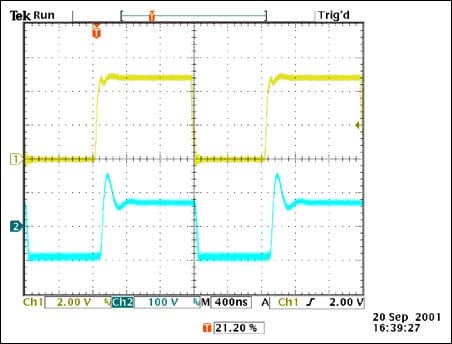

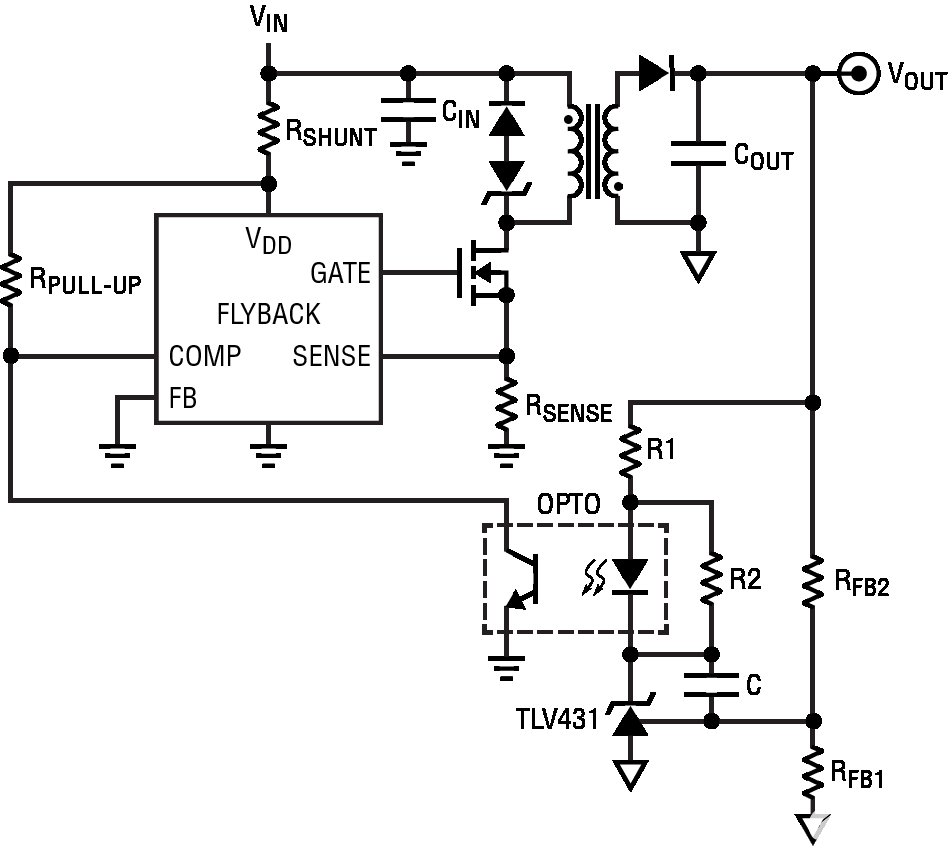

采用MAX1856的反激式拓撲應用電路如圖4所示。這是將兩個緩沖電路用于不同目標的示例。D3、C11 和 R11 形成一個箝位以限制漏極電壓,R5 與 C10 形成一個 RC 緩沖器,以抑制次級整流器 (D2) 處的振鈴。比較圖5A和圖5B中的波形,可以說明RC緩沖器在次級整流器上的影響。

圖4.采用MAX1856的反激式應用電路

圖 5A.D2整流器陰極的電壓,不帶緩沖器。(CH1 = MAX8分機/引腳1856處的電壓波形;CH2=整流器D2的陰極)。

圖 5B.帶緩沖器的D2整流陰極電壓(R5=150Ω;C10=330 pF)。(CH1 = MAX8分機/引腳1856處的電壓波形;CH2=整流器D2的陰極)。

總之,本應用筆記討論了無源電壓緩沖器的使用,特別是反激式轉換器拓撲。適當緩沖的電路更高效、更可靠,并且隨著時間的推移,在溫度和生產公差范圍內表現良好。當需要控制開關電壓瞬變時,了解和使用緩沖電路非常重要。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8694瀏覽量

147085 -

DC-DC

+關注

關注

30文章

1943瀏覽量

81603 -

變壓器

+關注

關注

0文章

1126瀏覽量

4010

發布評論請先 登錄

相關推薦

緩沖電路抑制多輸出DC-DC反激式轉換器電源中的電壓瞬態尖峰

緩沖電路抑制多輸出DC-DC反激式轉換器電源中的電壓瞬態尖峰

評論