DC-DC轉(zhuǎn)換器是電場和磁場的極好來源。其EMI頻譜從開關(guān)頻率開始,通常延伸至100MHz以上。為了盡量減少電容耦合和磁耦合,必須在印刷電路板(PCB)布局中小心。必須評估電路的寄生電容和寄生電感,以便在設(shè)計階段的早期進(jìn)行適當(dāng)?shù)臋?quán)衡。

多年來,集成 DC-DC 電源控制器的反復(fù)推出為我們提供了更高的性能水平。這些IC通過消除電源設(shè)計任務(wù)來減輕系統(tǒng)工程師的負(fù)擔(dān),但這種簡化導(dǎo)致了知識的損失。因此,開關(guān)轉(zhuǎn)換器應(yīng)提醒您小心。以下討論介紹了在為非隔離式DC-DC轉(zhuǎn)換器設(shè)計電路板布局時避免意外的規(guī)則。

優(yōu)化這種布局的第一條規(guī)則是隔離轉(zhuǎn)換器。DC-DC轉(zhuǎn)換器是電場和磁場的極好來源。其EMI頻譜從開關(guān)頻率開始,通常延伸至100MHz以上。為了盡量減少電容耦合和“磁場到環(huán)路”耦合,應(yīng)將轉(zhuǎn)換器放置在遠(yuǎn)離其他電路的位置,尤其是低電平模擬電路。

隔離轉(zhuǎn)換器并不總是那么容易。一些電路板在轉(zhuǎn)換器的一側(cè)接受輸入電壓,在另一側(cè)分配輸出電壓。例如,VME卡或電信卡包括電流高達(dá)20A的非常復(fù)雜的路由。單個連接器引入輸入電壓,并將多個輸出電壓分配到背板。因此,將轉(zhuǎn)換器放置在此連接器附近以減少電阻降的誘惑力很強(qiáng)。然而,該區(qū)域密集的接口驅(qū)動器、背板總線等,存在噪聲耦合的相關(guān)風(fēng)險。在某些情況下可以添加電源連接器,但該解決方案需要額外的電路板面積和成本。

銅走線中的電阻是最受限制的因素。對于給定長度和厚度的跡線,此電阻為

R = ρ × (升/秒)

其中 l 是以米為單位的走線長度,S 是以平方米為單位的走線面積,ρ(銅的電阻率)是 1.7x10-8Ω - m 在 20°C 或 2.1 x 10-8Ω - 70°C 時的米。 例如,0.5cm寬、35μm厚的銅跡線在20°C時的電阻為1mΩ/cm。該值可能看起來可以忽略不計,但如果通過兩個連接器和一個背板將2.5V/10A配電,則會引起注意。

在某些電路板上,走線厚度包括錫鉛層。該層幾乎可以使等效電阻翻倍:

鉛電阻率 = 2.07 x 10-7Ω - 米 20°C

時錫電阻率 = 1.14 x 10-7Ω - 米 在 20°C 時

在精度和走線損耗之間進(jìn)行權(quán)衡,您可以將轉(zhuǎn)換器從連接器移開。您可以通過執(zhí)行遠(yuǎn)程 V 來限制電阻降的影響外在連接器附近測量,但要注意電容耦合!要將大電流限制在定義的區(qū)域,請將所有電源線通過連接器一端的引腳布線。

場效應(yīng)管驅(qū)動器

隨著開關(guān)頻率的增加,開關(guān)時間越來越短:10kHz轉(zhuǎn)換器通常為500ns。在該頻率下,即使是最短的走線也具有很大的阻抗。同樣重要的是要注意,峰值柵極電流可以在極短的時間內(nèi)上升到幾安培。因此,MOSFET驅(qū)動信號的正確路由始于對轉(zhuǎn)換器框圖的分析。

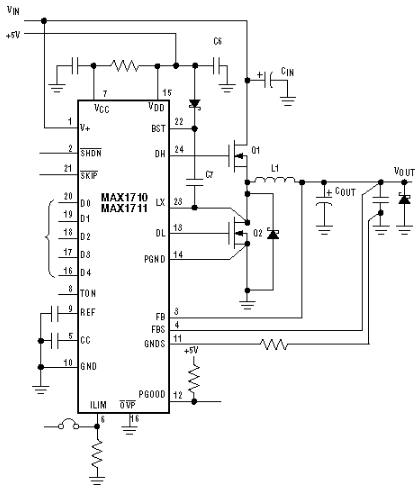

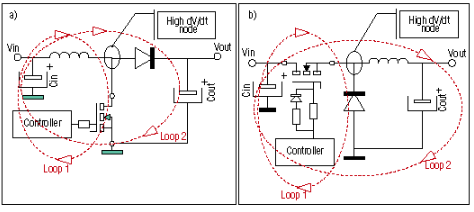

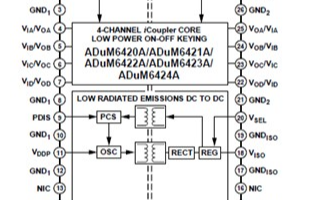

例如,考慮筆記本電腦的同步降壓控制器(圖 1)。MOSFET 由能量從諧振電容器(C6 和 C7)通過驅(qū)動器輸出的幾歐姆傳輸?shù)綎艠O來驅(qū)動。請注意,高端n溝道MOSFET (Q1)的柵極驅(qū)動是浮動的。n溝道驅(qū)動器的工作方式類似于電荷泵!

圖 1a.MAX1710同步降壓控制器的工作原理由應(yīng)用電路(a)和內(nèi)部框圖(b)描述。

圖 1b.MAX1710同步降壓控制器的工作原理由應(yīng)用電路(a)和內(nèi)部框圖(b)描述。

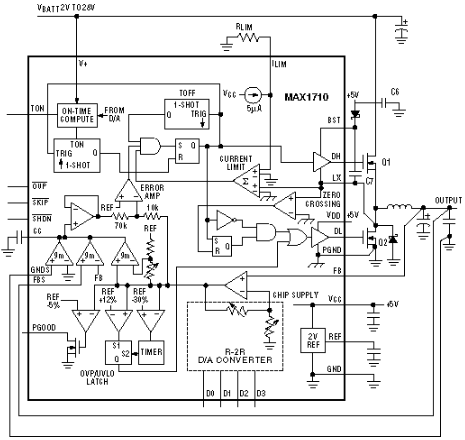

圖2突出顯示了開啟期間的電流路徑。任何串聯(lián)電感都可能導(dǎo)致災(zāi)難。在最好的情況下,尖峰較高,但只會增加開關(guān)損耗。在最壞的情況下,兩個MOSFET可能會因交叉導(dǎo)通(同時導(dǎo)通)而爆炸。因此,最佳布線意味著以下各項之間的走線非常短且很寬:

C6 和 Vdd

C6 和 Q2(S)

C7 和 BST,以及 C7 和 LX

Q1(G)和DH

Q2(G) 和 DL

Q1(S) 和 LX

Q2(S) 和 PGND

請記住,1cm走線的寄生電感約為10nH。

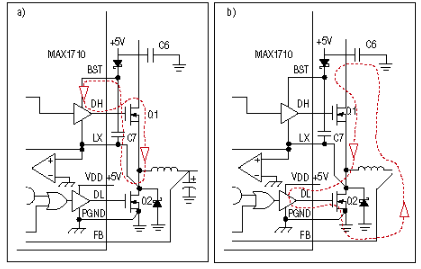

仔細(xì)觀察 C6,您可以看到它提供 Q1 和 Q2,但方式不同。它用作Q1的濾波電容和Q2的儲極電容。因為我們不能同時將C6放置在高端和低邊驅(qū)動器附近,所以我們將其放置在盡可能靠近V日嘎和PGND(峰值電流流動的地方),以及C7附近(幾乎平均電流)。請注意,PGND、DL 和 V日嘎別針是并排的,而不是偶然的!放置Q2和C6以最小化PGND、C6(-)和Q2(S)之間的接地走線長度。將此接地走線連接到 PGND 引腳附近的單個點(diǎn)的接地層。為避免共阻抗耦合,LX應(yīng)連接到Q1,PGND/C6(-)應(yīng)連接到Q2的源極。圖3突出顯示了關(guān)斷期間的電流路徑。

圖2.虛線表示柵極驅(qū)動電路中Q1 (a) 和 Q2 (b) 的大電流。

圖3.虛線表示Q1 (a) 和 Q2 (b) 柵極放電(關(guān)斷)路徑中的大電流。

應(yīng)盡可能限制“通過”的數(shù)量。事實上,當(dāng)di/dt很高時,過孔添加的幾十個納米亨是令人尷尬的。因此,您應(yīng)該將所有電源組件放在組件層上,甚至是 SMD 組件。如果您別無選擇,請將多個過孔并聯(lián)。

我們必須記住,控制器對于手頭的應(yīng)用程序來說通常過大。例如,通常的做法是使用10A控制器來產(chǎn)生3A輸出。由于我們通常出于成本原因選擇最小尺寸的MOSFET,因此片內(nèi)驅(qū)動器仍然尺寸過大,因此能夠?qū)崿F(xiàn)比所需更多的柵極驅(qū)動。

由于前面的討論試圖避免減慢MOS柵極驅(qū)動速度,因此將一個小電阻(10Ω至100Ω)與柵極驅(qū)動串聯(lián)似乎自相矛盾。然而,過大和/或快速驅(qū)動波形會產(chǎn)生更多的開關(guān)噪聲和RF干擾。在另一個極端,慢波形會在MOSFET和二極管(如果有的話)中產(chǎn)生更多的開關(guān)損耗。一個好的折衷方案是通過盡可能減慢波形斜率來降低EMI,同時保持可接受的效率水平。(圖4b柵極驅(qū)動中的元件允許您分別調(diào)整上升和下降時間。幸運(yùn)的是,大型驅(qū)動程序允許最后一點(diǎn)優(yōu)化。

路由功率級

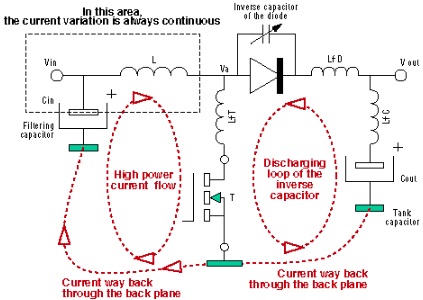

圖4顯示了許多電源轉(zhuǎn)換器共有的兩個大電流環(huán)路。為了響應(yīng)開關(guān)引起的擾動,這些環(huán)路支持高di/dt,并且(在某些節(jié)點(diǎn)上)還支持高dv/dt。識別這些循環(huán)有助于減少其影響。請注意,di/dt 在轉(zhuǎn)換器內(nèi)(在開關(guān)節(jié)點(diǎn)處)很大,但在轉(zhuǎn)換器外部很小。實際上,輸入電容器之前和輸出電容器之后的電流達(dá)到很高的值,但它們幾乎是連續(xù)的。當(dāng)轉(zhuǎn)換器設(shè)計良好時,它們的交流分量為低電平。

圖4.這些簡單的原理圖說明了升壓(a)和降壓(b)開關(guān)轉(zhuǎn)換器的基本工作原理。

首先,盡量減少寄生電感。我們將考慮升壓轉(zhuǎn)換器,但推理可以轉(zhuǎn)換為降壓型。圖5顯示了導(dǎo)致最多問題的寄生電感類型。

圖5.當(dāng)主開關(guān)晶體管(T)關(guān)閉時,二極管電容放電如圖所示。

在不描述開關(guān)周期的 10 個相位的情況下,我們可以考慮當(dāng)電感電流被 MOSFET 短路時,MOSFET 關(guān)斷。二極管的反向電容通過環(huán)路二極快地充電,二極管陽極處的節(jié)點(diǎn)電壓Va(通常在Vout - Vd)接近0V。串行電感器 (LfT + LfD + LfC) 增加了放電時間,從而增加了 MOSFET 中的開關(guān)損耗。這些類型的電感也會產(chǎn)生噪聲。

峰值電流受晶體管的限制,晶體管作為電流源工作(Vds 仍等于幾伏)。對于 2A MOSFET,該電流源可能為 10A!電流電平在很短的時間內(nèi)很大(幾個10ns)。請記住,改變通過電感器的電流會產(chǎn)生與電流變化成比例的電壓:

v = L × [di(t)/dt]

這個過渡階段是一個很好的尖峰發(fā)生器!我們再次通過最小化走線長度并在MOSFET、二極管和Cout周圍使用短而寬的走線來最小化寄生電感。現(xiàn)在,您可以看到如何通過控制柵極驅(qū)動波形中的斜率來降低噪聲。

為了限制阻性壓降和過孔數(shù)量,功率級SMD元件應(yīng)放置在電路板的元件側(cè),電源走線在其元件層上布線。如果可能,電源接地也應(yīng)在同一層布線。這種布置還有另一個好處:接地層的擾動較小。要消除輻射場,請注意最小化功率電流環(huán)路的面積。

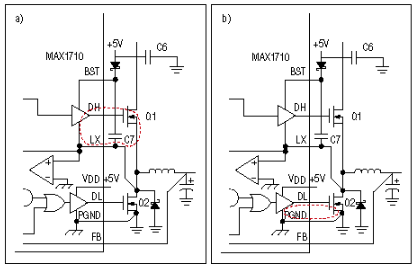

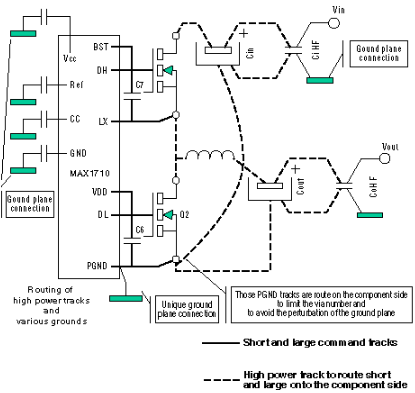

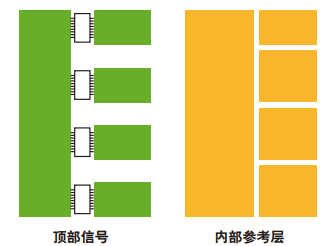

當(dāng)需要在元件層以外的層上布線電源走線時,請從電感或濾波電容器中選擇走線(即,Cout用于降壓轉(zhuǎn)換器,Cin用于升壓轉(zhuǎn)換器)。由于通過此類走線的電流幾乎是連續(xù)的,因此不會產(chǎn)生噪聲,只會產(chǎn)生電阻降。如果在元件層正下方的層上布線,寄生電感將更小。為避免公共阻抗耦合,應(yīng)將PGND、電源電路接地和一般接地層分開(圖6)。

圖6.這些細(xì)節(jié)說明了控制器電路中PGND與柵極控制走線的路由。

電容器和其他組件

密切注意DC-DC轉(zhuǎn)換器電路中電容端子的走線布線非常重要。大值低ESR電容器價格昂貴,不良布線會抵消其性能。另一方面,良好的布線可以將輸出噪聲從150mV降低到50mV!

紋波與電感值、電容ESR、開關(guān)頻率等直接相關(guān),但HF噪聲(尖峰)取決于寄生元件和開關(guān)動作。我們可以預(yù)測從1MHz到10MHz的尖峰頻率,具體取決于開關(guān)頻率。

在不良布線中(圖7a),與走線長度相關(guān)的寄生電感會引起麻煩:L1會導(dǎo)致噪聲增加,L2限制了HF電容CoHF的衰減。解決方法(圖7b)是將輸入走線引入電容焊盤的一側(cè),輸出走線在焊盤的另一側(cè)。

圖7.電容走線布線不當(dāng)會引入不需要的寄生電感。

現(xiàn)在,在放置和布線了最笨重的部件之后,我們將注意力轉(zhuǎn)向電感器。故意但不需要的耦合(圖 8a)允許電源環(huán)路中的電流污染控制器電源 (Vcc)。通過切換Lp1產(chǎn)生的高di/dt會導(dǎo)致Vcc過沖,很容易達(dá)到幾百毫伏。用

v(t) = L × [di(t)/dt]

L = 10nH, ΔI = 1A, Δt = 50ns, ΔV = 0.2V!

如前所述,第一個預(yù)防措施是分離電源走線并小心使用PGND。第二種預(yù)防措施是避免將走線連接到電源環(huán)路(見圖8b)。分配輸入電壓的走線應(yīng)在輸入電容和控制器的Vcc連接之前連接。輸出電壓在連接到HF輸出電容器后分配。

圖8.(b)所示的連接可防止不需要的共阻抗耦合(a)。

最后,一些雜項建議:PGND走線的不良布線會導(dǎo)致共阻抗耦合(PGND端子的一個原因是避免污染控制器的內(nèi)部接地節(jié)點(diǎn))。將高阻抗走線(尤其是調(diào)節(jié)輸出電壓的輸出電阻分壓器)從支持高dV/dt的節(jié)點(diǎn)移開。這種耦合引起的電流會使控制器振蕩。

審核編輯:郭婷

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8724瀏覽量

147414 -

控制器

+關(guān)注

關(guān)注

112文章

16396瀏覽量

178512 -

DC-DC

+關(guān)注

關(guān)注

30文章

1953瀏覽量

81781

發(fā)布評論請先 登錄

相關(guān)推薦

接地—升壓型DC/DC轉(zhuǎn)換器的PCB布局

AC/DC非隔離型降壓轉(zhuǎn)換器的設(shè)計案例概要

正激式和反激式DC-DC轉(zhuǎn)換器介紹

DC-DC轉(zhuǎn)換器的相關(guān)資料分享

DC-DC降壓轉(zhuǎn)換器電路布局與設(shè)計和實踐

基于500mW隔離式設(shè)計中無需單獨(dú)的隔離式 DC-DC 轉(zhuǎn)換器

非隔離DC-DC轉(zhuǎn)換器的功能特點(diǎn)

數(shù)控非隔離式DC/DC降壓轉(zhuǎn)換器參考設(shè)計

DC-DC降壓轉(zhuǎn)換器PCB布局的技巧

快速輸入轉(zhuǎn)換速率應(yīng)用中DC-DC轉(zhuǎn)換器的設(shè)計注意事項

非隔離式DC-DC轉(zhuǎn)換器的布局注意事項

非隔離式DC-DC轉(zhuǎn)換器的布局注意事項

評論