基本定義

一個高速數字信號從IC內部出發 → IC封裝(例如鍵合線和管腳)→ PCB走線 → 到達另一個IC或者連接器/電纜等的過程中,這些物理材料對信號質量和電源質量的影響,稱為信號完整性。

在信號波形上,體現為高速信號的電流或者電壓的變化速度,即:

dI/dt 和dV/dt。

這些參數變化速度越快,信號完整性問題越嚴重。

主要帶來四類問題:

信號失真

信號間串擾

影響電源分配網絡(PDS),例如軌道塌陷、地彈等。

電磁干擾,主要是對外輻射。

信號頻率和上升時間的關系

在常見的高速數字信號中,我們有個經驗值是:某信號的上升時間是它周期的10%。例如

10MHz信號的上升時間是10ns

100MHz信號的上升時間是1ns

1GHz信號的上升時間是100ps

低頻信號也可能有信號完整性問題

通常大多數人按照信號頻率來辨別某信號是否屬于高速信號,是否需要考慮信號完整性問題,例如以100MHz為界限。100MHz以下的信號不考慮信號完整性問題。

但是隨著芯片技術的提升,可以生產更小尺寸的晶體管門溝道。當門的溝道長度越短,空穴和電子需要移動的距離也越短。這意味著門可以在更短時間切換狀態,在波形上表現為上升時間的提升。這將使信號完整性問題更明顯。

而芯片廠商為了成本考慮,在生產中盡量使所有的硅晶圓標準化,這樣隨著芯片尺寸的降低,每個硅晶圓上可以包含更多的芯片。因此有可能一顆低速芯片,它和高速芯片是在同一條產線出產的。這樣這顆低速芯片在工作時,也會有較短的上升時間。

因此依靠信號頻率來決定在設計中是否要考慮信號完整性問題已經不是很可靠的一個方法。建議在設計中,仔細查詢原件spec。在PCBA生產后,進行相關電氣參數測量。

仿真和模型

在PCB出圖之前,通過設計軟件進行信號完整性仿真,可以對信號波形有個初步的印象。仿真結果可以作為PCB設計修正的輸入依據。

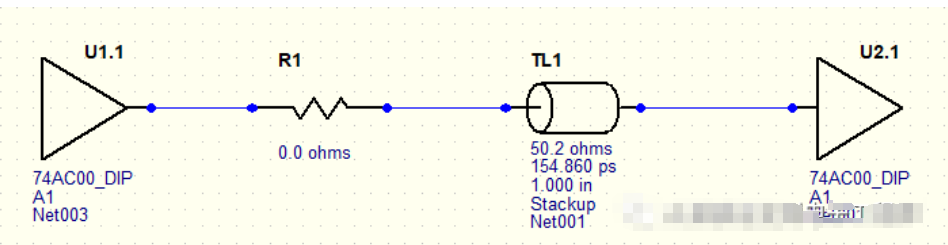

我接觸過得仿真軟件有Mentor的Hyperlynx,Cadence的Allegro,和安捷倫的ADS。最容易上手的是Hyperlynx。下圖是使用Hyperlynx進行的一個基本電路仿真結果。

進行掃描仿真,將R1設定為從0歐姆到50歐姆,每增加10歐姆仿真一次。可以看到R1=50歐姆時(紅色波形)效果最好。這是最簡單的源端串聯阻抗匹配。

<波形仿真結果>

<眼圖仿真結果>

高速信號完整性仿真使用的模型稱為IBIS模型(輸入輸出緩沖接口規范)。它是對芯片輸入或輸出端口的電壓-電流曲線、電壓-時間的定義。因為不牽扯到芯片內部的設計和工藝,因此和Spice模型(Simulation program with integrated circuit emphasis)相比,更容易獲得。大的芯片廠商,例如TI、ST、鎂光等官網都可以下載到對應的IBIS模型。在開始使用IBIS模型之前,要先檢查模型的正確性。曾經遇到過某DSP廠商提供的IBIS模型中,把DDR3 CLK+和CLK-的定義搞反的情況。除了芯片,其他的無源器件(例如電阻、接插件、走線等),很多都沒有專門的電路模型。需要用電阻、電容、電感等來組建無源器件模型。例如下圖R1的等效電氣模型由R2+C1+L1組成。

構成信號完整性的基本元件

分析信號完整性問題,由四類元件構成。

電阻

電容

電感

互連線

-

電阻

+關注

關注

87文章

5606瀏覽量

174290 -

pcb

+關注

關注

4351文章

23405瀏覽量

406556 -

IC

+關注

關注

36文章

6093瀏覽量

178315 -

連接器

+關注

關注

99文章

15209瀏覽量

139235 -

信號完整性

+關注

關注

68文章

1432瀏覽量

96418

發布評論請先 登錄

評論