在本文中,我想談談我們CEVA和Intrinsix如何就OEM和半導體進行協作,以找到進行交鑰匙ASIC設計或無線子系統設計的可靠路徑。

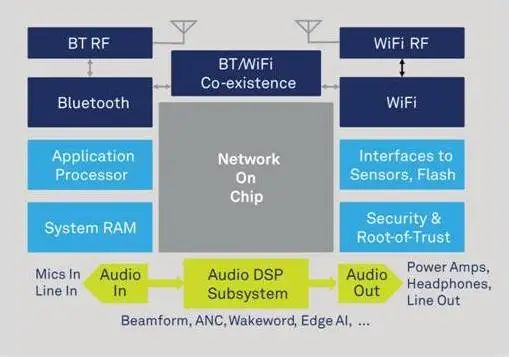

舉例來說,想象一下您可能想要為無線智能揚聲器或智能家庭娛樂系統構建的SoC類型。該系統的核心是音頻管線,支持控制命令語音處理,并可通過Wi-Fi和藍牙連接技術實現無線連接,其中BT連接可用于遠程控制或音頻流式傳輸。我們還提供用于藍牙和WiFi的片上射頻。總體結構圖如下所示:

ASIC設計共創階段I – 規劃

規劃從詳細討論產品需求開始。智能揚聲器通常會配備多個麥克風,支持自動回聲消除和音頻波束成型,以放大整個房間的語音命令。無線耳塞可能只需一個或兩個麥克風,并且依靠骨傳導來接收語音命令,而非波束成型。

對于藍牙,您想僅使用BLE還是想通過雙模式來支持較舊的設備或更豐富的音頻?對于Wi-Fi,向后兼容性可解決大多數問題,但您可能需要考慮藍牙和Wi-Fi之間的干擾(2.4GHz)。我們有解決這一問題的共存解決方案。集成射頻收發機也需要仔細規劃。

對于IP選擇,CEVA是無線、音頻、人工智能和運動感應嵌入式解決方案的市場領導者,可解決此應用的IP 需求。

對于其他功能和參數目標,我們會討論設計和IP替代方案以及相關取舍。討論將涵蓋應用控制、外部接口(如果有的話)以及安全啟動、配置和無線更新的安全性(CEVA還提供嵌入式安全信任根解決方案)。在此階段,我們應該設定功率、性能和服務質量(帶寬和延遲)目標。如果您有自有IP或計劃使用商業IP,則我們需要討論IP與總體目標的匹配程度。所有重要預期都應在這一階段敲定。然后,我們將構建、審核并商定最終架構結構圖和需求列表。

我們的方法高度重視驗證,以確保我們能夠準確地按您的預期提供解決方案,并且方案能夠在第一批硅片樣品上正常運行。因此,我們將與您密切合作,以制定、審核和簽署全面的需求規范。其中應包括用例和操作模式,以及驅動這些用例和模式的軟件,還有預期的異常行為。需求必須涵蓋參數行為和功能。

一旦架構和需求得到充分定義,我們將構建詳細的項目時間表和成本分析,并納入人力、IP、工具和其他因素。我們將通過一系列完整文檔向您展示這些內容,從驗證計劃和設計規范,到DFT以及ASIC設計的實施計劃。我們還將討論軟件注意事項。

CEVA為其許多IP提供廣泛的軟件解決方案,例如無線協議堆棧、音頻堆棧和用于AI產品的CNN/DNN堆棧。這些內容將在規劃討論中介紹,并在報告中予以詳細說明,以幫助您了解如何將現有軟件集成到目標硬件中。

無線子系統的規劃過程與SoC計劃的規劃過程基本相似,除了這里的客戶端還必須在子系統上提供SoC約束(例如可用時鐘、重置、電源控制平面圖約束等)。

共創 – 規劃階段以外

共創項目的其余部分遵循標準ASIC設計或子系統設計流程,裝配、驗證和實施之間具有顯著的并行性。射頻和混合信號集成需要專業技能。

在整個過程中,我們會更新進展并邀請您討論當前設計情況。在RTL開發過程中,客戶將為我們提供測試軟件,以證明關鍵用例的需求已得到滿足。如果他們運行FPGA仿真以進行自己的軟件開發,他們將在仿真就緒的RTL衰減可用時使用這些RTL衰減。對于ASIC設計,我們定期向客戶提供最新進展,從物理設計前時序收斂到物理設計后時序收斂及完全簽核。

我們過往的表現是我們的品質保證

CEVA和Intrinsix將驗證和嚴密的項目計劃放在我們所有工作的第一位,這些構成我們對您的承諾。35年來,我們一直按時、按規格地向領先的系統和半導體公司交付設計和子系統。我們合作的大部分客戶來自國防、醫療及其他領域,他們對流程和產品可靠性的要求非常高。我們與這些客戶共同開發的流程和專業知識已經融入到我們“第一次就把事情做好”的文化理念中,正如您在我們的驗證和項目管理規范中所看到的那樣。

我們設計的ASIC范圍廣泛,從智能揚聲器到無線環繞音響,從智能電源工具到智能手術儀器,從醫療植入體到可穿戴和智能健康設備,從物聯網微控制器到生物指紋傳感器。其中許多應用目前都在批量生產中。

我們基于DSP的IP解決方案包括移動、物聯網和基礎設施中的5G基帶處理平臺、任何攝像頭設備的高級成像和計算機視覺平臺、多個物聯網市場的音頻/語音/聲音和超低功耗始終開啟/傳感應用平臺。

我們提供傳感器技術,并為耳穿戴設備、可穿戴設備、AR/VR、PC、機器人、遠程控制和物聯網等市場提供廣泛的傳感器融合軟件和慣性測量裝置(IMU)解決方案。對于無線物聯網,我們的藍牙(低功耗和雙模)、Wi-Fi 4/5/6 (802.11n/ac/ax)、超寬帶(UWB)、NB-IoT和GNSS平臺是業內廣泛授權的連接平臺。

我們在IP和ASIC設計交付方面的綜合專業知識為您保駕護航,CEVA和Intrinsix無疑是您下一款突破性產品的正確選擇。

聯系CEVA,了解我們如何幫助您進行共創規劃。

識別右側二維碼

立即了解

CEVA更多信息

?

?

本文作者:Mark Beal, Chief Technical Officer at Intrinsix, subsidiary of CEVA

-

dsp

+關注

關注

553文章

8011瀏覽量

349122 -

藍牙

+關注

關注

114文章

5830瀏覽量

170471 -

CEVA

+關注

關注

1文章

178瀏覽量

75957

原文標題:共創計劃確保可靠ASIC設計

文章出處:【微信號:CEVA-IP,微信公眾號:CEVA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog 與 ASIC 設計的關系 Verilog 代碼優化技巧

ASIC集成電路在人工智能中的應用

ASIC集成電路如何提高系統效率

ASIC集成電路與FPGA的區別

負載箱在確保可靠電力分配中的作用

共創AI+時代——2024中國移動全球合作伙伴大會

如何確保設備在高溫環境下的可靠性和安全性

AC/DC電源模塊可靠性是確保設備長時間穩定運行的關鍵因素

污水處理廠水質檢測儀如何確保穩定可靠的運行?

專用集成電路asic是不是芯片

SiFive 加入甲辰計劃,共創 RISC-V 生態繁榮

中國首個長城汽車產品共創理念發布 打造共創生態新潮流

如何確保IGBT的產品可靠性

共創計劃確保可靠ASIC設計

共創計劃確保可靠ASIC設計

評論