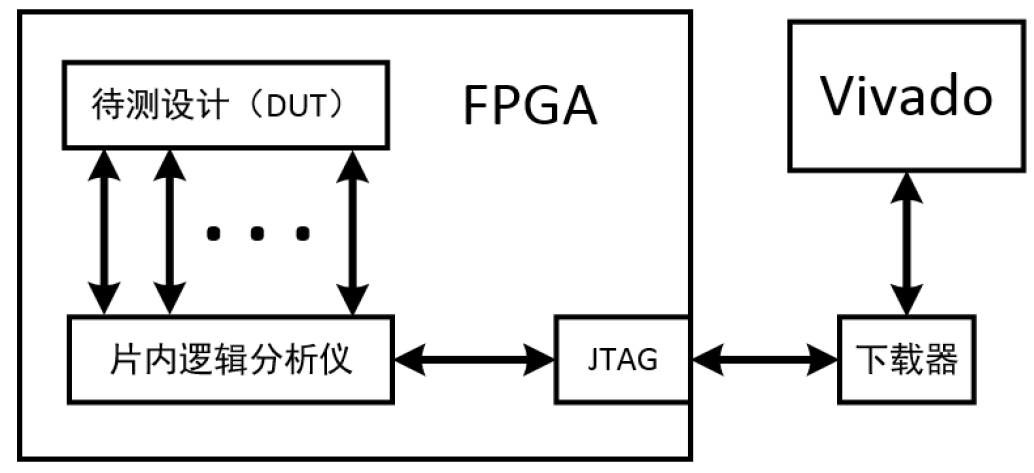

傳統的邏輯分析儀在使用時,我們需要將所要觀察的信號連接到FPGA的IO管腳上,然后觀察信號。當信號比較多時,我們操作起來會比較繁瑣。在線邏輯分析儀就比較好的解決了這個問題,我們可以將這些功能加到FPGA設計當中。

其中待測設計就是我們整個的邏輯設計模塊,在線邏輯分析儀也同樣是在FPGA設計中。通過一個或多個探針來采集希望觀察的信號。然后通過JTAG接口,將捕獲到的數據通過下載器回傳給我們的用戶界面,以便我們進行觀察。

在邏輯分析儀使用的過程中,我們一般常用的調用方法有兩種:

1、IP核

2、mark debug標記信號

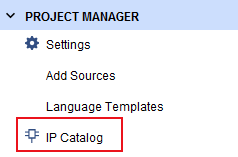

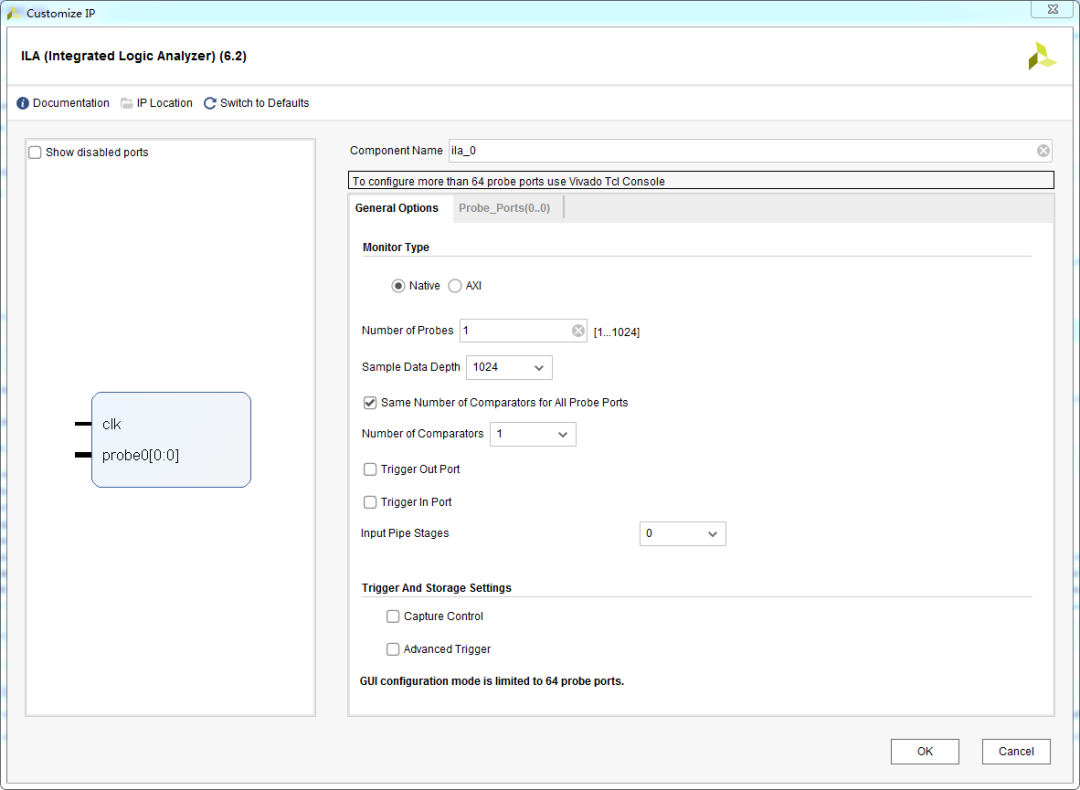

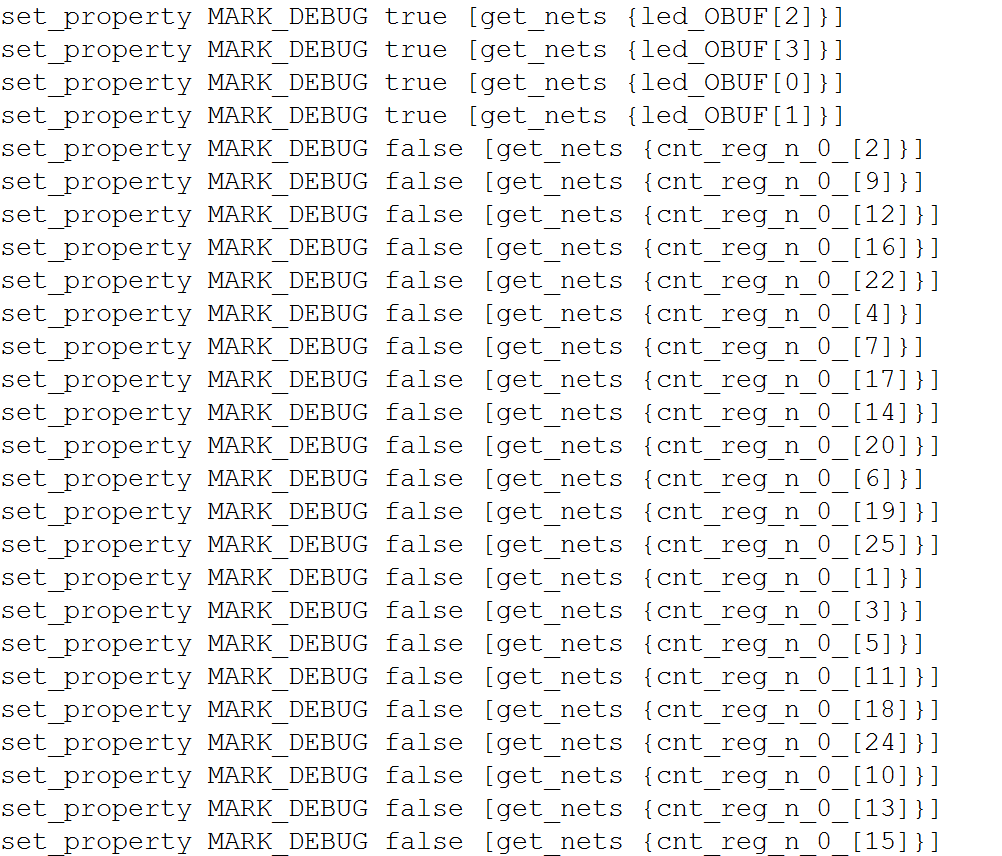

接下來我們先說一下第一種方法。這種方法需要我們打開IP核管理器,在程序設計中例化ILA。首先我們打開IP核管理器,搜索ILA,雙擊打開。

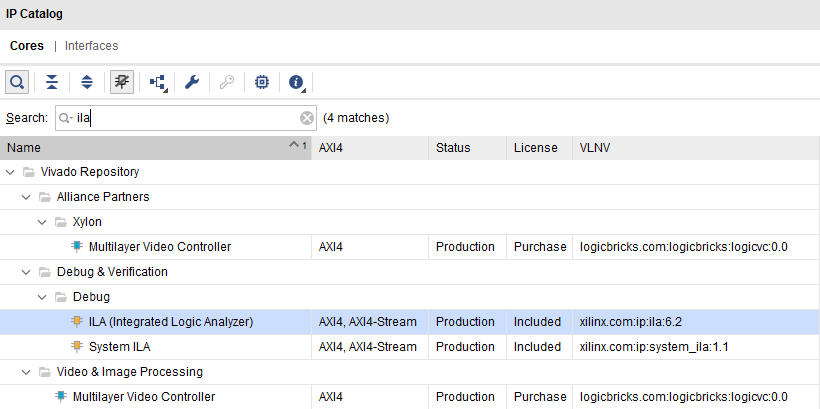

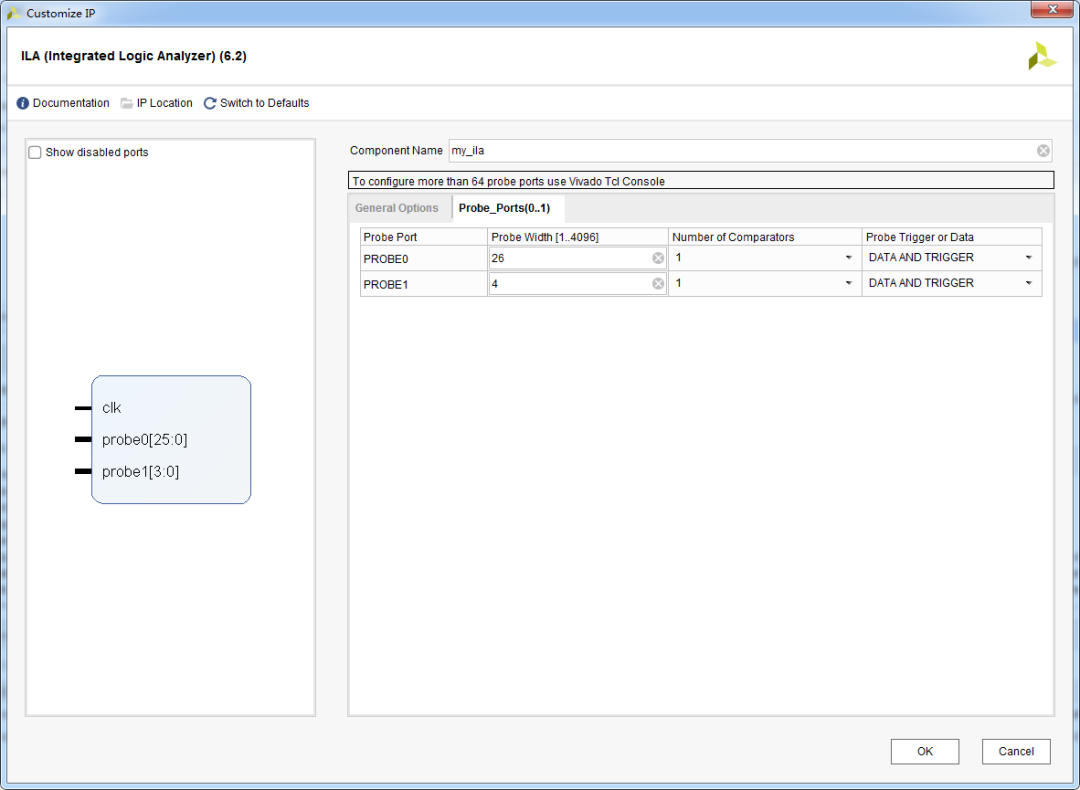

在此配置界面,我們配置幾項內容。首先是Component Name,我們可以給我們的邏輯分析儀起一個名字,比如我在此改為my_ila。

在number of probes選項選擇我們需要觀察的信號個數,我們以流水燈為例,我們可以觀察一下代碼設計當中的計數器cnt以及輸出led。所以我們在此項設置為2。Sample data depth為采樣深度,采樣深度影響到了我們可以觀察的信號長度,大家可以根據自己的需要進行設置,在此我選擇深度為1024。

然后在Probe ports里面設置被觀察信號的位寬。計數器為26位,led輸出為4位,那么我們將位寬設置好,點擊OK生成IP核。

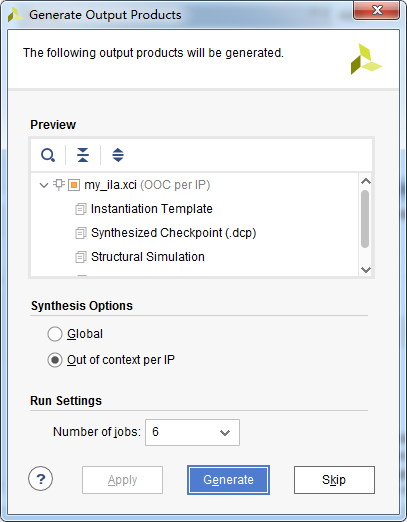

在這里,我們簡要介紹一下Vivado的OOC(Out-of-Context)綜合的概念。對于頂層設計,Vivado使用自頂向下的全局(Global)綜合方式,將頂層之下的所有邏輯模塊都進行綜合,但是設置為OOC方式的模塊除外,它們獨立于頂層設計而單獨綜合。

通常,在整個設計周期中,頂層設計會被多次修改并綜合。但有些子模塊在創建完畢之后不會因為頂層設計的修改而被修改,如IP,它們被設置為OOC綜合方式,OOC模塊只會在綜合頂層之前被綜合一次。這樣,在頂層的設計迭代過程中,OOC模塊就不必跟隨頂層模塊,而進行一次次的會產生相同結果的多余的綜合了。所以,OOC流程減少了設計周期時間,并消除了設計迭代,使大家可以保存和重用綜合結果。

Out-of-Context(OOC) 綜合是一種自底向上的設計流程,默認情況下,Vivado設計套件使用OOC的設計流程來綜合OOC模塊。OOC模塊可以是來自IP catalog的IP、來自Vivado IP Integrator的block design或者頂層模塊下手動設置為OOC方式的任何子模塊。

來自IP catalog的IP就默認使用OOC綜合的方式,例如上圖中的“Synthesis Options”選項就設置為了“Out of Context Per IP”。這些IP會在頂層的全局綜合之前,單獨地進行OOC綜合并生成輸出產品(Generate Output Products),包括綜合后的網表等各種文件。在對頂層進行綜合時,OOC模塊會被視為黑盒子,并且不會參與到頂層的綜合中來。在綜合之后的實現過程中,OOC模塊的黑盒子才會被打開,這時其網表才是可見的并參與到全局設計的布局布線中來。

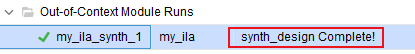

OOC綜合完畢之后如下圖所示:

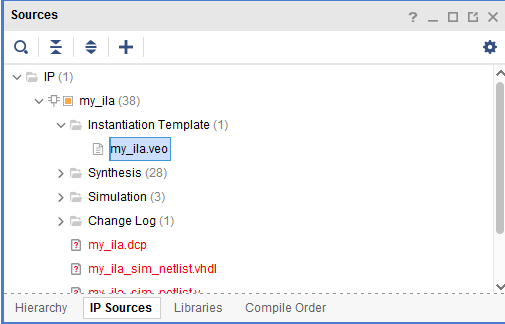

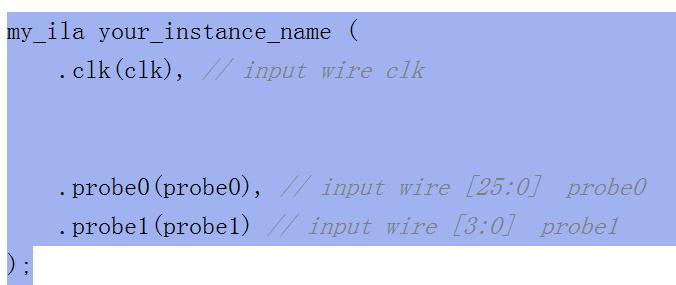

IP核調用完成之后,我們在IP sources窗口中打開IP核的instantiation template。my_ila.veo文件為例化的頭文件,我們雙擊打開,將下圖內容復制粘貼到頂層文件當中即可。

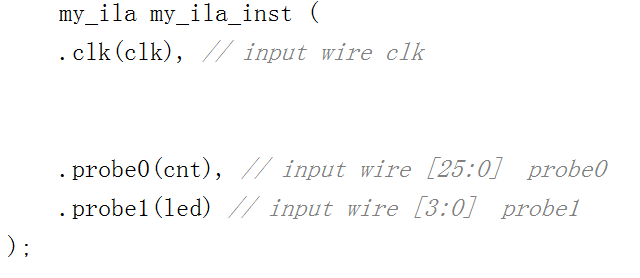

復制好之后,我們將信號做一下連線,改一下例化名。那么我們的邏輯分析儀調用就完成了。

調用完成之后,我們將文件保存,然后生成下板文件進行下板。

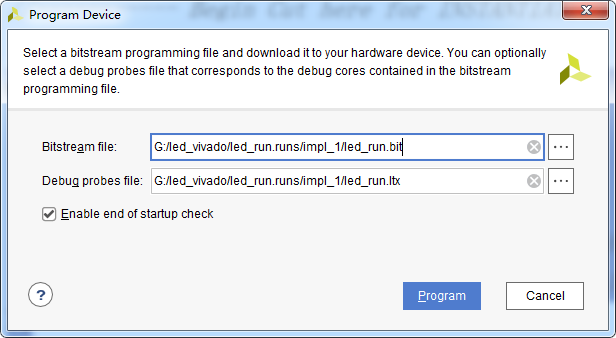

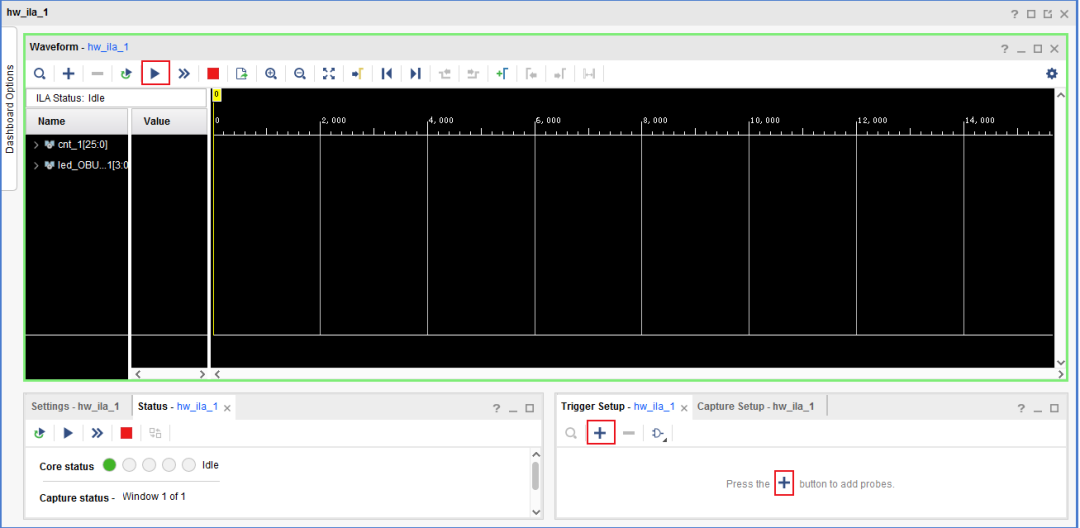

下板時,界面中出現兩個文件。第一個文件為bit流文件。第二個為邏輯分析儀文件。直接點擊program。下載完成之后會出現如下界面。

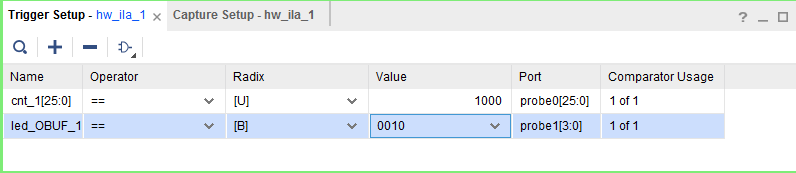

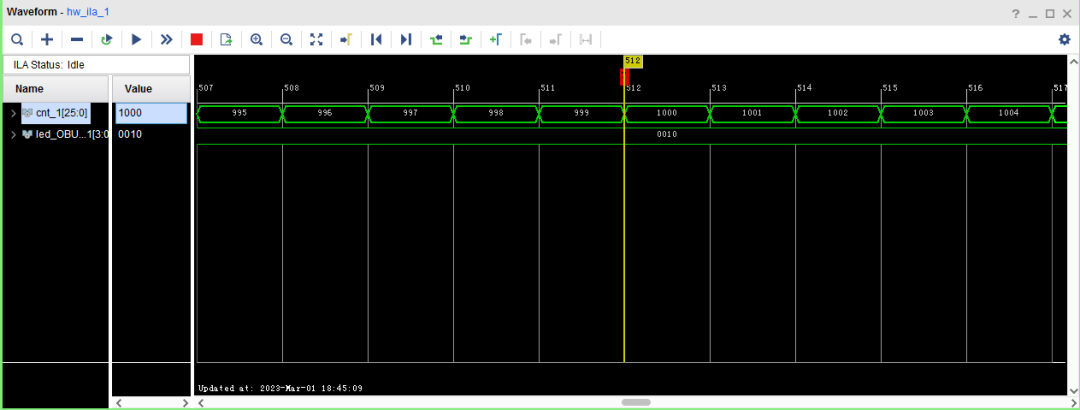

在開始觀察波形之前,我們需要先在右下角小窗口里面設置觸發信號。這個我們可以理解為我們想要觀察的波形的位置。比如我們可以觀察一下led為第二個燈亮,且計數器數到1000的位置,那么我們的設置如下圖:

設置好之后,我們點擊波形界面的三角形符號,進行觸發,那么就可以觀察到我們的波形了。

第二種方法:

“網表插入調試探針流程”需要在綜合后的網表中,將要進行調試觀察的各個信號,標記“Mark_Debug”屬性,然后通過“Setup Debug”向導來設置ILA IP核的參數,最后工具會根據參數來自動創建ILA IP核。我們點擊“Flow Navigator”窗口中的“Open Synthesized Design”按鈕,如下圖所示:

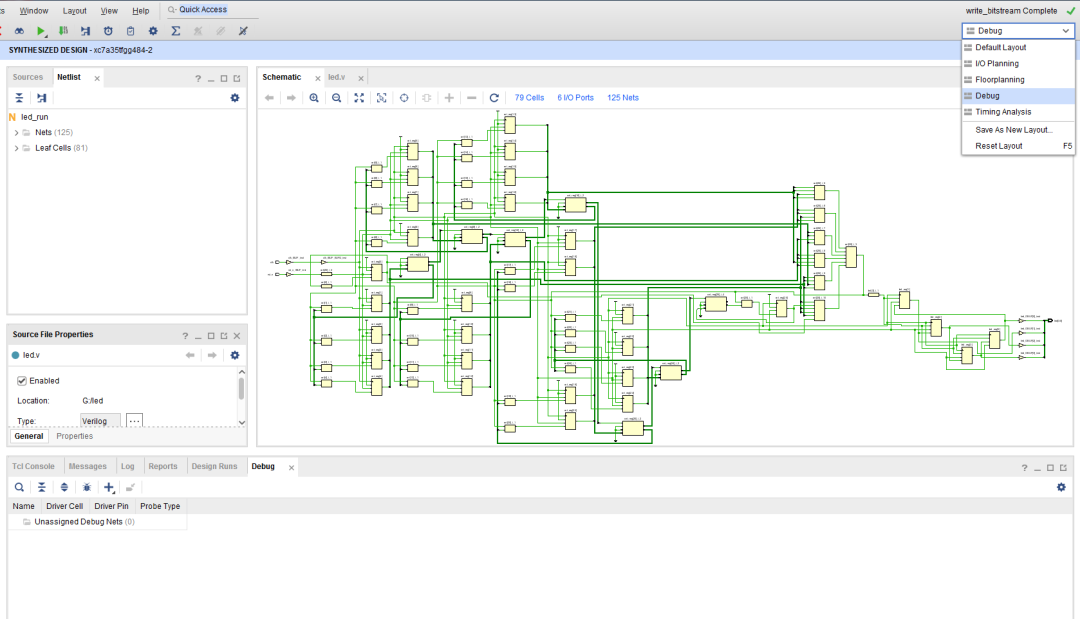

在綜合后設計的窗口布局選擇器中,我們選擇“Debug”窗口布局,如下圖所示:

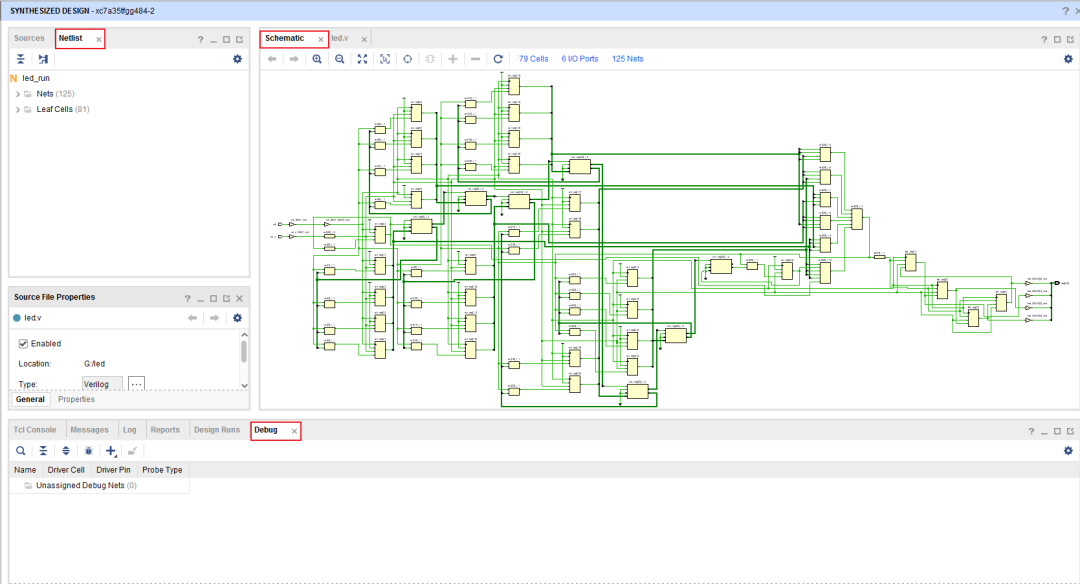

此時,Vivado打開了“Netlist”子窗口、“Schematic”子窗口以及“Debug”子窗口。其中,“Netlist”子窗口和“Schematic”子窗口都用于標記要進行觀察的信號,“Debug”子窗口用于顯示并設置ILA IP核的各個參數。如下圖所示:

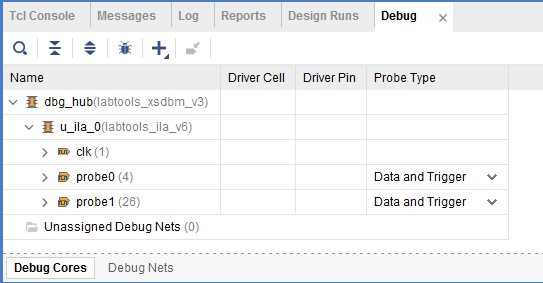

在“Debug”子窗口中,又包含兩個選項卡“Debug Cores”和“Debug Nets”。這兩個選項卡都用于顯示所有的已標記為“Mark_Debug”的信號。不同之處在于,“Debug Cores”選項卡是一個更加以ILA IP核為中心的視圖,所有已標記為“Mark_Debug”的信號并且已經被分配到ILA探針的信號都會被顯示在各個ILA IP核的視圖樹下,已標記為“Mark_Debug”的信號但是還沒有被分配到ILA探針的信號被顯示在“Unassigned Debug Nets”下,當然也可以在其中查看和設置ILA IP核的各種屬性和參數。

“Debug Nets”選項卡僅顯示已標記為“Mark_Debug”的信號,但不顯示ILA IP核,所有已標記為“Mark_Debug”的信號并且已經被分配到ILA探針的信號都會被顯示在“Assigned Debug Nets”下,已標記為“Mark_Debug”的信號但是還沒有被分配到ILA探針的信號被顯示在“Unassigned Debug Nets”下。

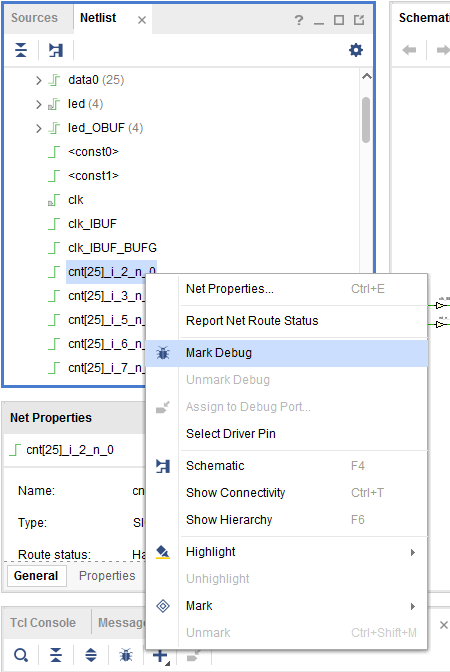

我們首先標記要進行觀察的信號,以led信號為例,在“Netlist”子窗口中的“Nets”目錄下,找到“led_OBUF”網絡,右擊該網絡(此時右邊的“Schematic”子窗口也會自動地高亮選擇此網絡,因為“Netlist”子窗口中的對象和“Schematic”子窗口中的對象,兩者之間是交叉選擇的),在彈出的菜單中心選擇“Mark Debug”命令,如下圖所示:

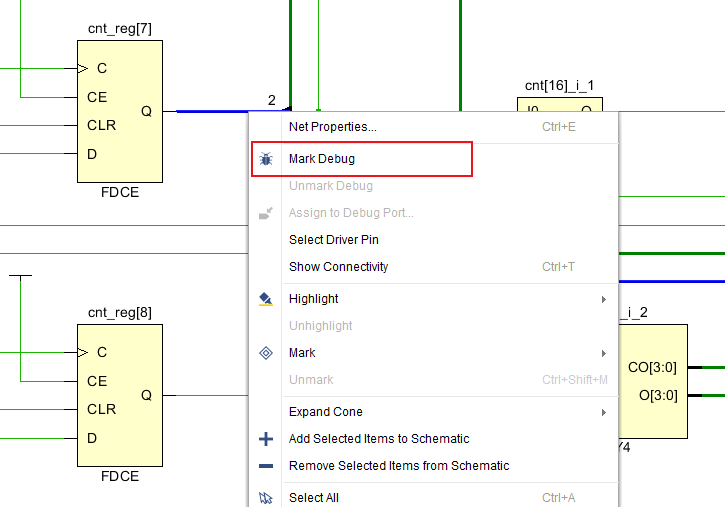

也可以在“Schematic”子窗口中選擇網絡,然后右鍵選擇“Mark Debug”命令,如下圖所示:

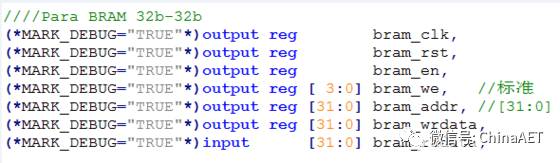

另外,也可以在HDL源代碼中為想要觀察的reg或wire信號添加“Mark Debug”屬性,例如:(* mark_debug = “true” *)reg [25:0] cnt ; 其中“(* mark_debug = “true” *)”必須緊挨在變量聲明的前面。

這樣,在綜合完之后打開綜合后的設計,counter信號就自動被標記了“Mark Debug”屬性。此時在“Debug”子窗口的“Debug Nets”選項卡的“Unassigned Debug Nets”目錄下就會出現我們剛剛標記的“led_OBUF”網絡。

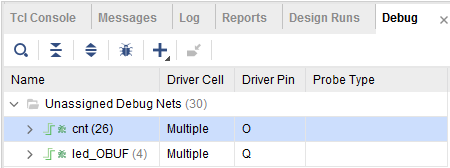

此時“Debug”子窗口的“Debug Nets”選項卡的“Unassigned Debug Nets”目錄下就有了“led_OBUF”和“cnt”兩個信號,如下圖所示:

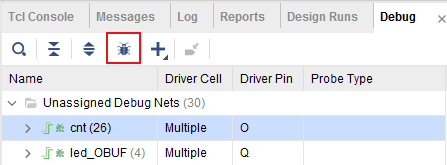

之后我們點擊“Debug”子窗口中的“Setup Debug”按鈕,如下圖所示:

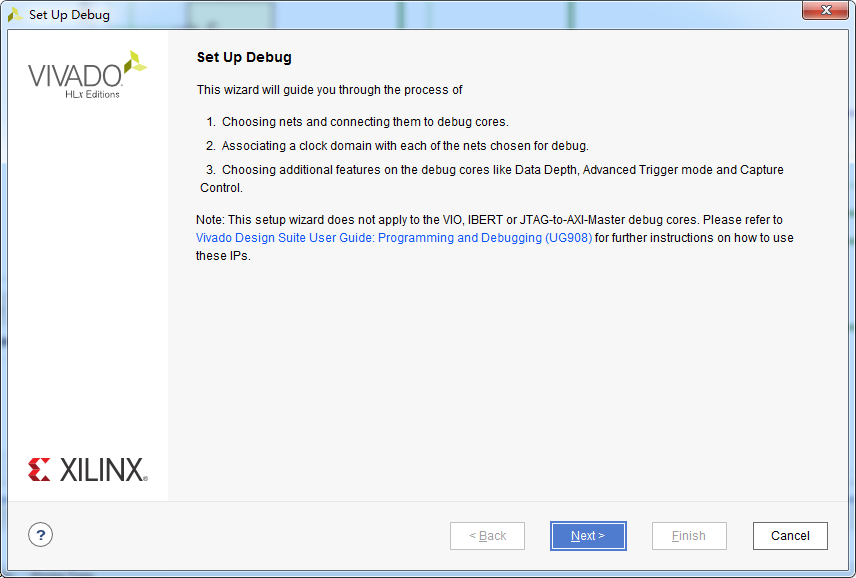

彈出“Setup Debug”向導,我們直接點擊next,如下圖所示:

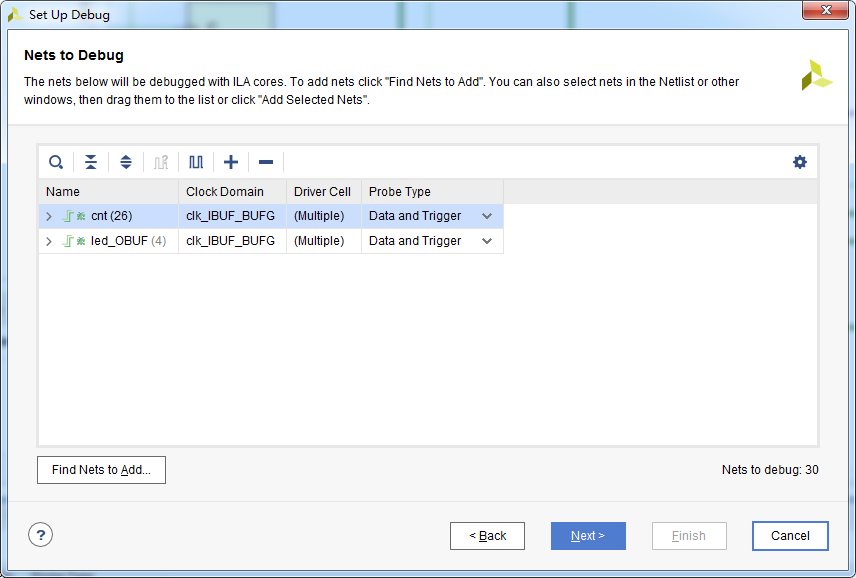

接下來的頁面是選擇用于采樣待測信號的時鐘域,Vivado會自動識別出各個待測信號所屬的時鐘域并將其自動設定為其采樣時鐘,例如,我們剛剛添加的這“led_OBUF”和“cnt”兩個信號就屬于“sys_clk_IBUF”時鐘域,并且Vivado也已經自動將“sys_clk_IBUF”時鐘設置為了這兩個信號的采樣時鐘,如下圖所示:

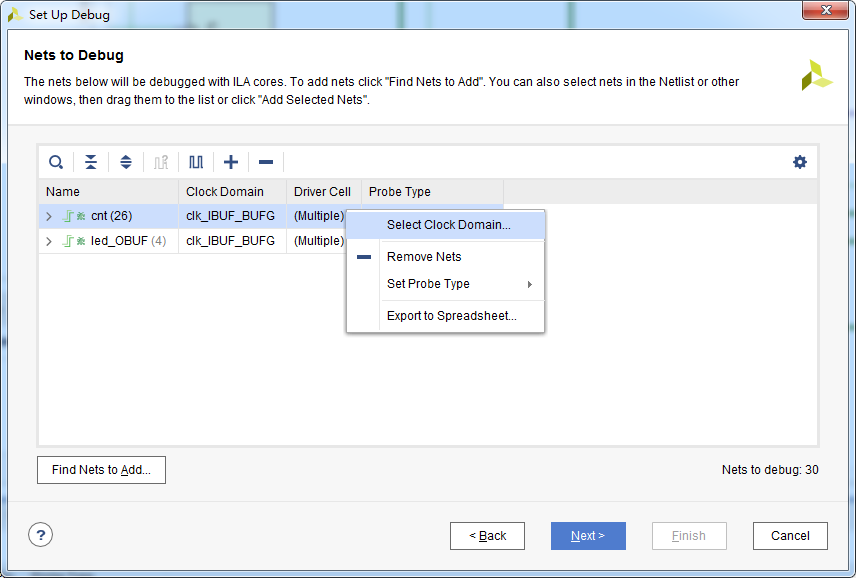

當然,用戶也可以手動指定各個用于采樣待測信號的時鐘域,右擊待測信號,選擇“Select Clock Domain”,彈出“Select Clock Domain”窗口,如下面兩個圖所示:

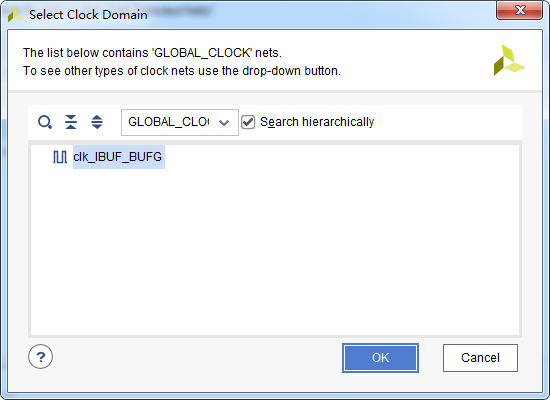

在“Select Clock Domain”窗口中就可以選擇用于采樣待測信號的時鐘了。“Setup Debug”向導會為每個采樣時鐘生成一個單獨的ILA IP核,由于本例程中只有一個時鐘,所以這里最后只會生成一個ILA IP核。

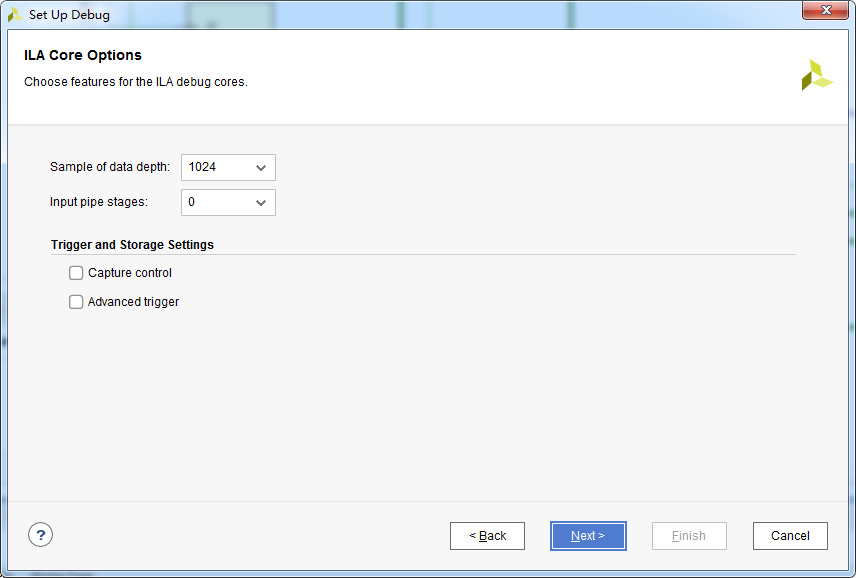

設置完采樣時鐘后,我們點擊next,接下來的頁面用于設置ILA IP核的全局設置,如下圖所示:

其中“Sample of data depth”用于設置采樣深度,“Input pipe stages”用于設置待測信號和其采樣時鐘之間的同步級數。如果在上一個設置時鐘域頁面中,存在與其采樣時鐘之間是異步的待測信號,則為了避免亞穩態,此數值最好不要低于2。

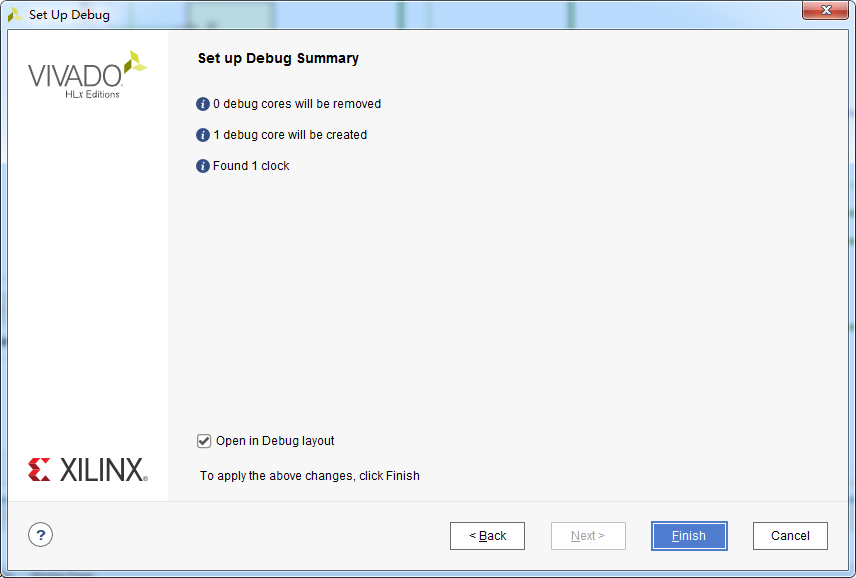

由于本例中的兩個待測信號的其采樣時鐘是同步的,所以可以設置為0。我們點擊next,就進入了最后的概覽頁面,確認無誤后直接點擊finish即可,如下圖所示:

在“Debug”子窗口中的“Debug Cores”選項卡中,可以看到Vivado已經添加了ILA IP核,并且“Unassigned Debug Nets”目錄下已經沒有未被分配的信號了,如下圖所示:

網表中被標記為Mark Debug的信號也變為了虛線,以表示其完成了ILA IP核的分配,如下圖所示:

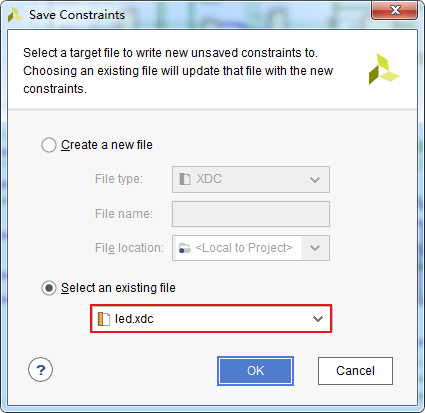

前面我們提到過,在“網表插入調試探針流程”中,用戶設置的調試信息會以Tcl XDC調試命令的形式保存到XDC約束文件中,在實現階段,Vivado會讀取這些XDC調試命令,并在布局布線時加入這些ILA IP核。

此時,我們所做出的所有的更改和設置,都還只是停留在電腦內存中,我們需要將其保存在硬盤的XDC約束文件中,點擊工具欄中的保存按鈕,如下圖所示:

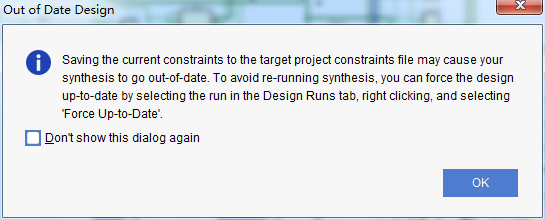

在出現的對話框中直接點擊OK,如下圖所示:

彈出的“Save Constraints”窗口中,用于詢問用戶將約束保存在哪個XDC約束文件中,本例的工程中只有一個XDC約束文件,如下圖所示,我們直接點擊OK即可:

此時,我們打開led_twinkle.xdc,就會看到在用戶約束的下面,Vivado自動寫入了用于debug的約束,如下圖所示:

在實現階段,Vivado會讀取這些約束,并按照這些命令的參數來自動地在布局布線時加入ILA IP核。至此,我們就成功地使用“網表插入調試探針流程”將ILA IP核添加到了設計中。接下來就可以將實現設計并生成比特流,最后將比特流下載到FPGA中,以對信號進行在線觀察,這一部分內容在上面第一種方法里面已經介紹過了,在此不再重復介紹。

審核編輯:劉清

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602997 -

計數器

+關注

關注

32文章

2256瀏覽量

94477 -

邏輯分析儀

+關注

關注

3文章

214瀏覽量

23165 -

邏輯分析

+關注

關注

0文章

14瀏覽量

7980 -

Vivado

+關注

關注

19文章

812瀏覽量

66471

原文標題:Vivado邏輯分析儀使用教程

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Vivado邏輯分析儀使用教程簡析

Vivado邏輯分析儀使用教程簡析

評論