Xilinx Zynq系列是帶有ARM Cortex-A系列CPU核的FPGA,前幾年流落到二手市場上的“礦板”就以Zynq 7010為核心,可以說是最廉價的Zynq實驗平臺了。淘個這樣的板子,再另外找個Xilinx的JTAG就可以玩FPGA和ARM Linux. 因為玩的人多,網上有資料,還有別人做過的擴展板可以參考。本壇大佬們早就玩過了。我三年前就買了一塊,但一直是閑置狀態,直到現在才想來搞搞。

這塊EBAZ4025板子接上12V電源就可以工作了,有RJ45網口,板子上有焊盤可以自己焊上TF卡座、UART接口、JTAG口,就相當于一個完整的ARM Linux板子(板載DDR3 SDRAM 256MB,NAND Flash 128MB),還有若干FPGA I/O引出來到雙列排針座,方便自己分配用途。

EBAZ4025通電以后上面的Linux就啟動了,通過UART連接可以看到uboot和Linux輸出的信息。我是要把它作為FPGA開發來用的,所以先直接焊上JTAG排針連接調試器,電腦軟件可以識別到JTAG 掃描鏈上有兩個設備,一個是FPGA,一個是ARM CPU。

Zynq的內部分為兩個系統,一個叫PS,就是ARM CPU以及外設,包括DDR內存控制器、DMA等等這些ARM運行依賴的部件;另一個系統叫PL,就相當于傳統的FPGA. 這兩部分之間有很多種方式可以通信,就可以比結合FPGA和ARM的各自優點來處理復雜的任務了。

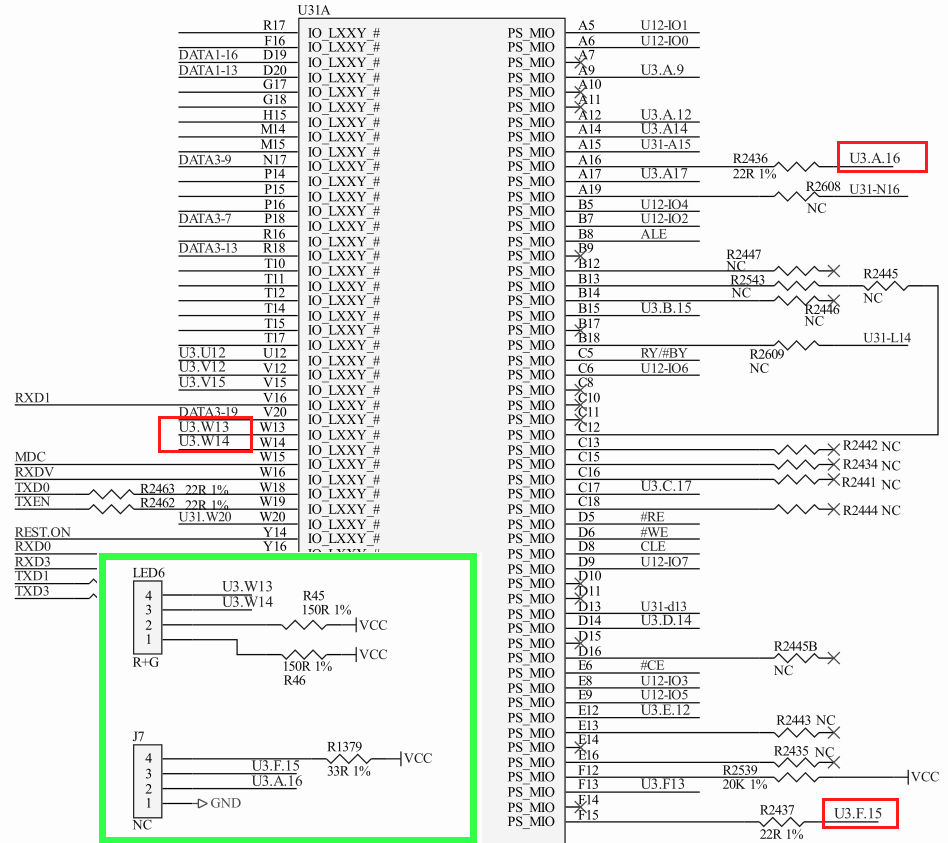

Zynq 7000系列的IO引腳也分為PS和PL各自管理的的,PS部分引腳有固定的用途,和開發FPGA時寫引腳約束不同。根據礦板的電路圖了解到,兩個LED是連接到PL部分的,而UART直接接的是PS的MIO。

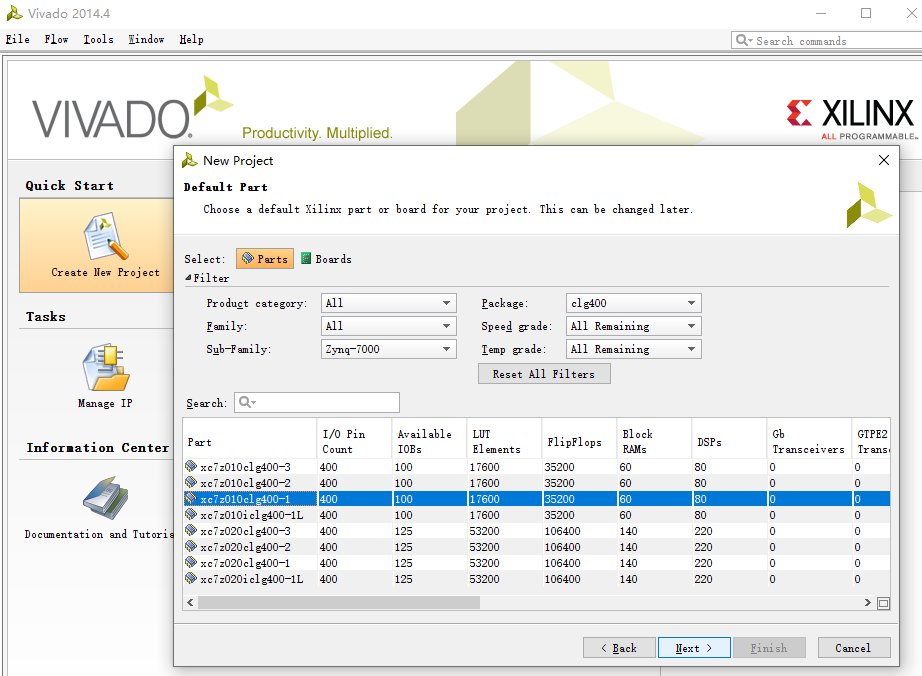

學習Zynq的開發可以參考網上的教程。這玩意門檻稍微高一點,先得下載Vivado安裝,為了開發ARM的程序還要安裝SDK,都是很龐大的軟件。如果熟悉了的話Vivado操作起來也很快,但頭幾次么……

先創建一個工程,選擇器件型號,這和其它FPGA開發思路是一樣的。

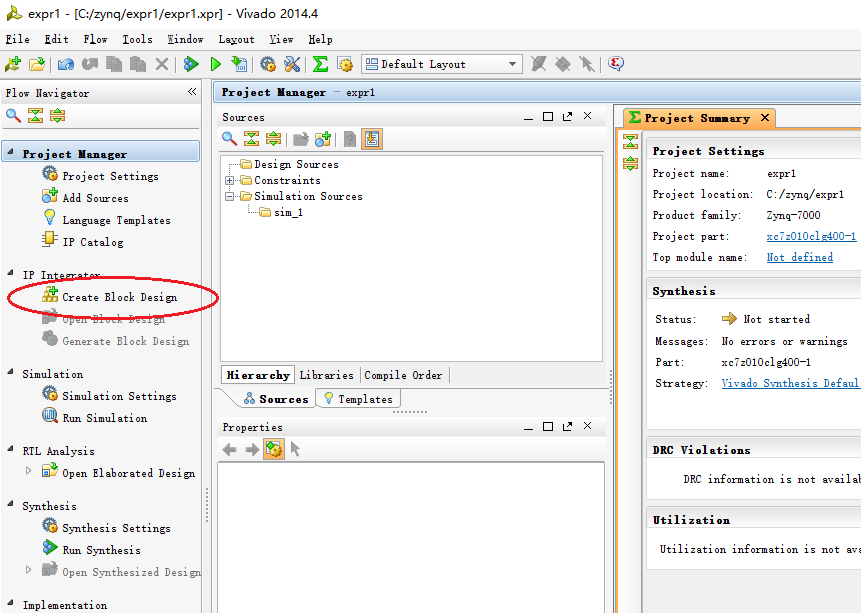

按照教程,然后是Create Block Design

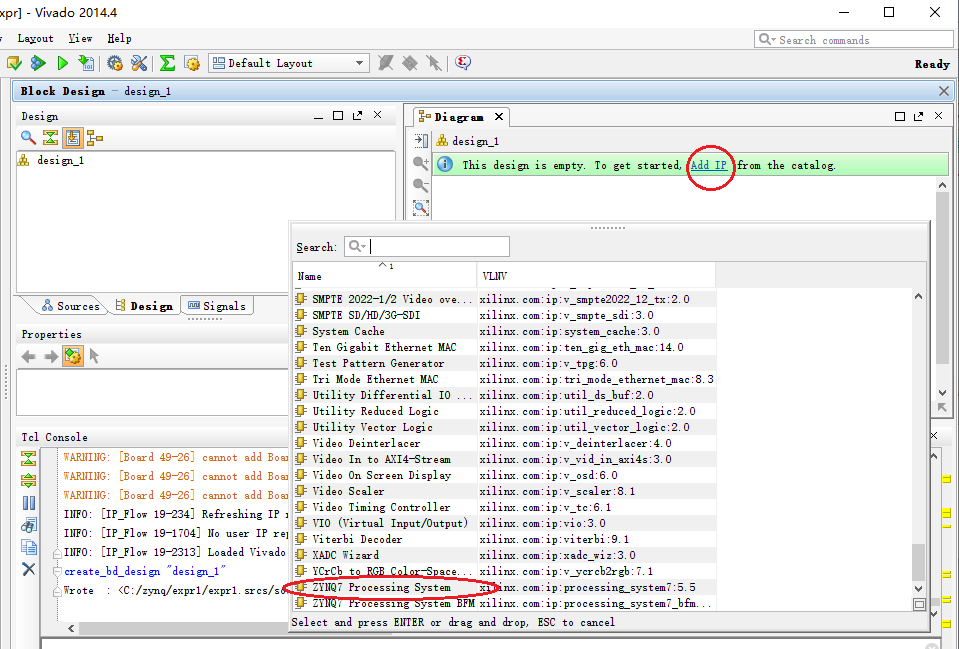

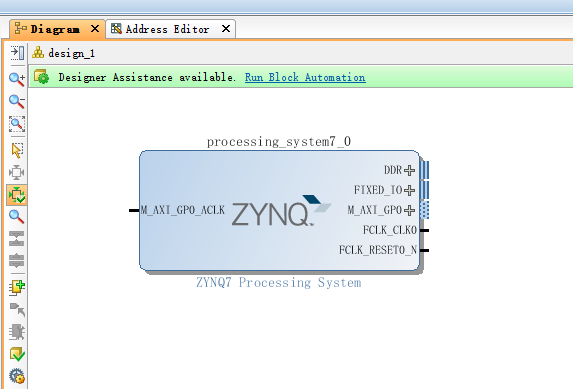

添加IP——ZYNQ7 Processing System. 這種圖形化的block design方式我最初學FPGA的時候就用,直觀容易理解。

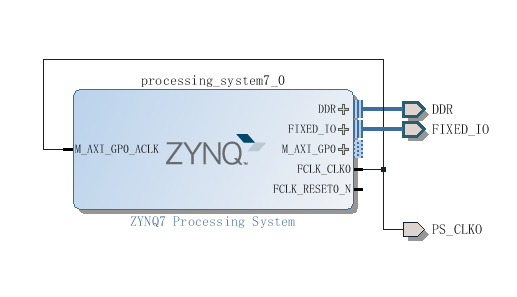

加上這個IP之后框圖上就出現了一個模塊,代表PS部分。

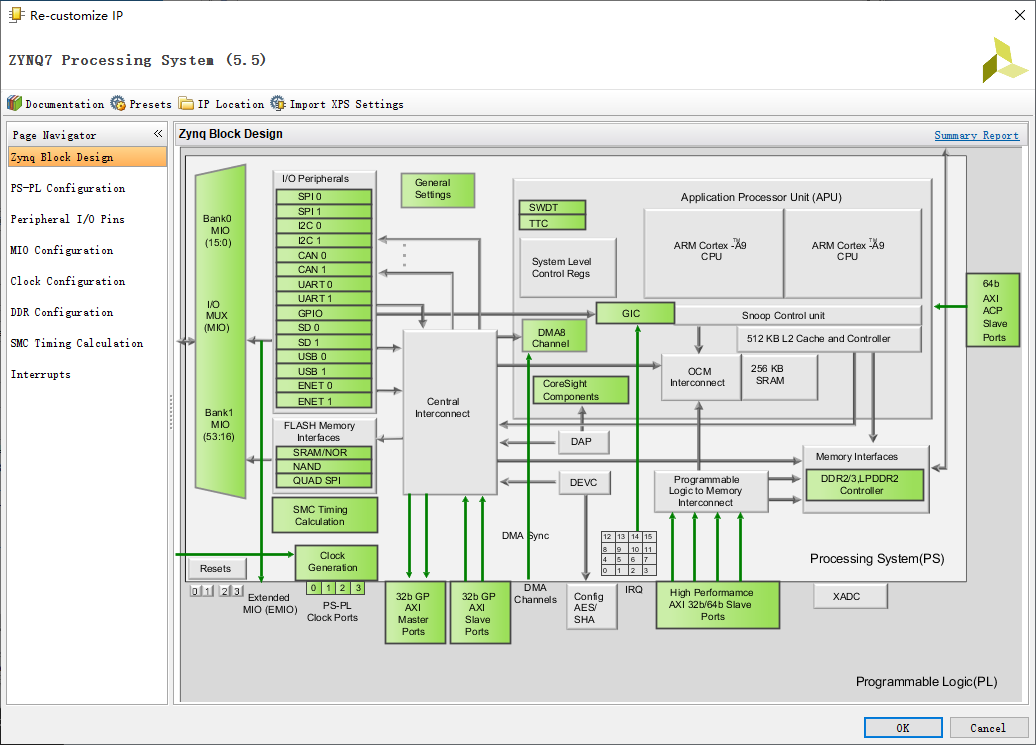

在圖上雙擊這個ZYNQ Processing System模塊,就打開配置窗口,進行時鐘、IO、內存等設置了。這些需要根據礦板上的資源和連接關系來定。

首先這里有個PS部分的結構圖,可以了解有那些片上外設可以供CPU用的。第一個實驗為了讓程序能打印輸出,需要用UART。

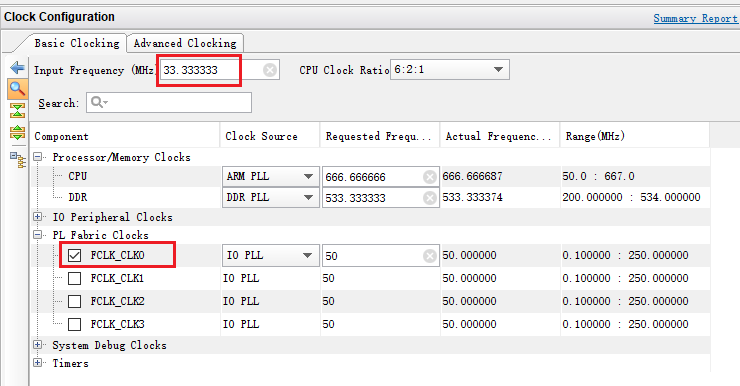

看看時鐘配置,默認的輸入時鐘33.333MHz 和礦板一致,就不用調整了。CPU和DDR的時鐘頻率用默認的不會有問題。PS部分給PL部分提供的時鐘是實驗需要的,默認輸出一個50MHz。

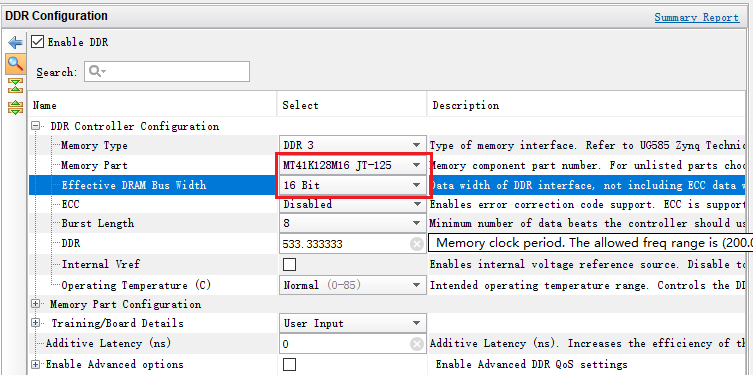

DDR的配置,需要根據實際板子上的芯片調整一下,128M x16-bit. 我不確定SDK編寫的程序是要在DDR內存中運行還是PS的片上RAM中運行,所以DDR還是要配置的。

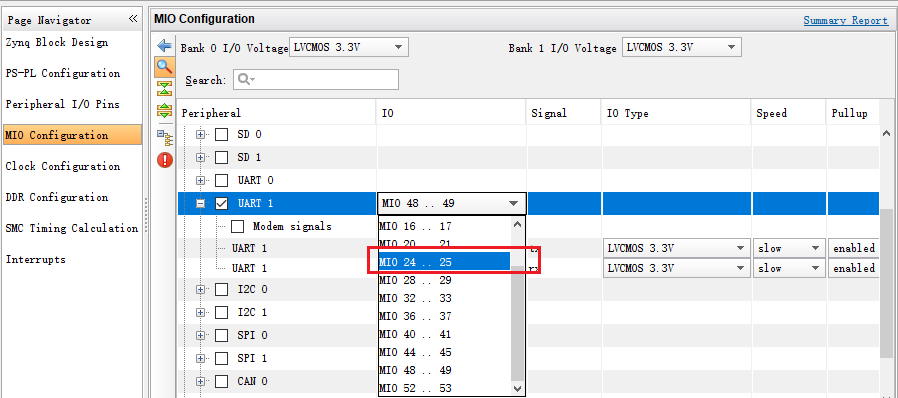

MIO的配置,是為了要給UART分配引腳。根據電路圖,UART是連接在A16和F15這兩個腳的,查Xilinx手冊得知是PS_MIO24和PS_MIO25,就在MIO Configuration中配置使用UART1(因為UART0沒有MIO 24,25的映射)。

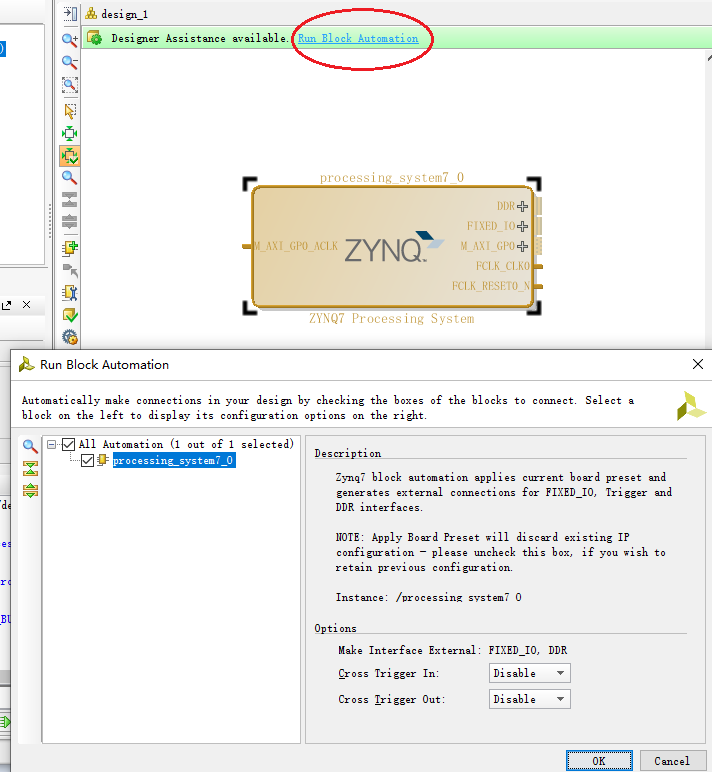

配置好之后Run Block Automation,自動生成必要的接口。

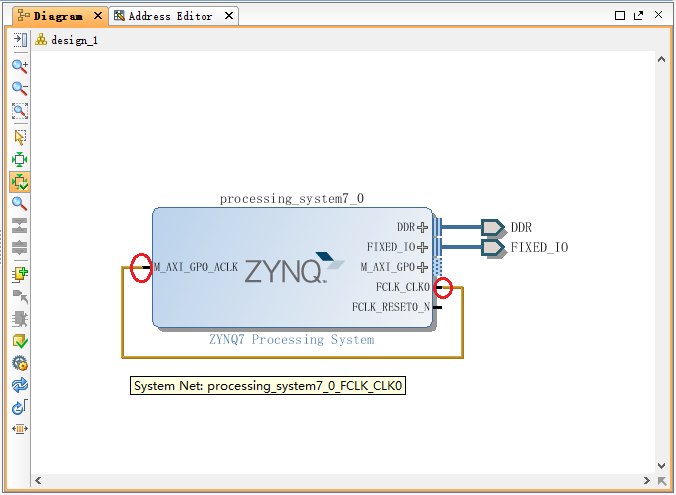

教程上說配置好之后要連一根線,把FCLK_CLK0和M_AXI_GP0_ACLK連起來。前者是Zynq PS輸出的時鐘(內部PLL從晶振給的時鐘生成,可以給PL用),后者我理解是AXI總線的時鐘。這里并不使用總線,我覺得不連也沒關系。

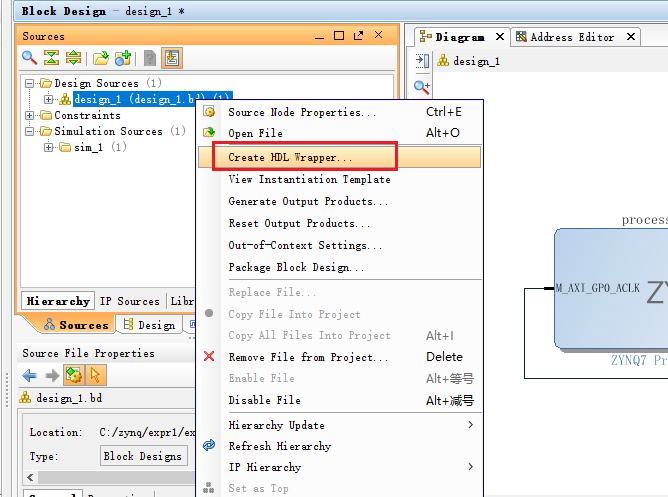

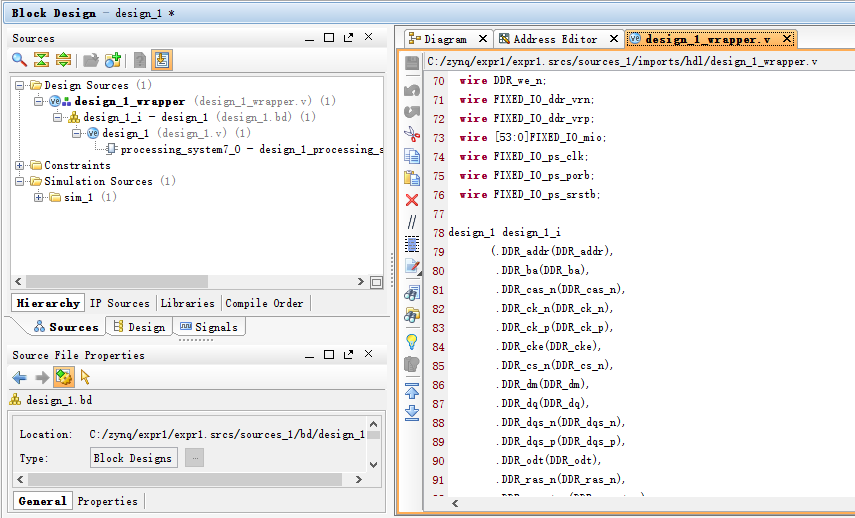

接下來,按照教程說的是要Create HDL Wrapper,注意對話框中選擇允許用戶修改,不然自己編輯的會被覆蓋掉。

做這一步的目的是把PS外面再包上一層,這樣就方便加入自己編寫的邏輯了。下面我要編寫一點邏輯來點LED,就直接加到 system_wrapper.v 里面去。

注意Create HDL Wrapper之后,系統的層次結構變化了,頂層名稱從design_1變成了design_1_wrapper。

由于礦板的PL是沒有帶晶振的(有空焊盤沒裝),要看FPGA跑起來的效果需要外接時鐘信號到排針上面。實際在已經創建的PS模塊上,FCLK_CLK0就是一個時鐘信號,現在我要把它給PL用,還需要創建一個port把它引出來,不然頂層看不到。

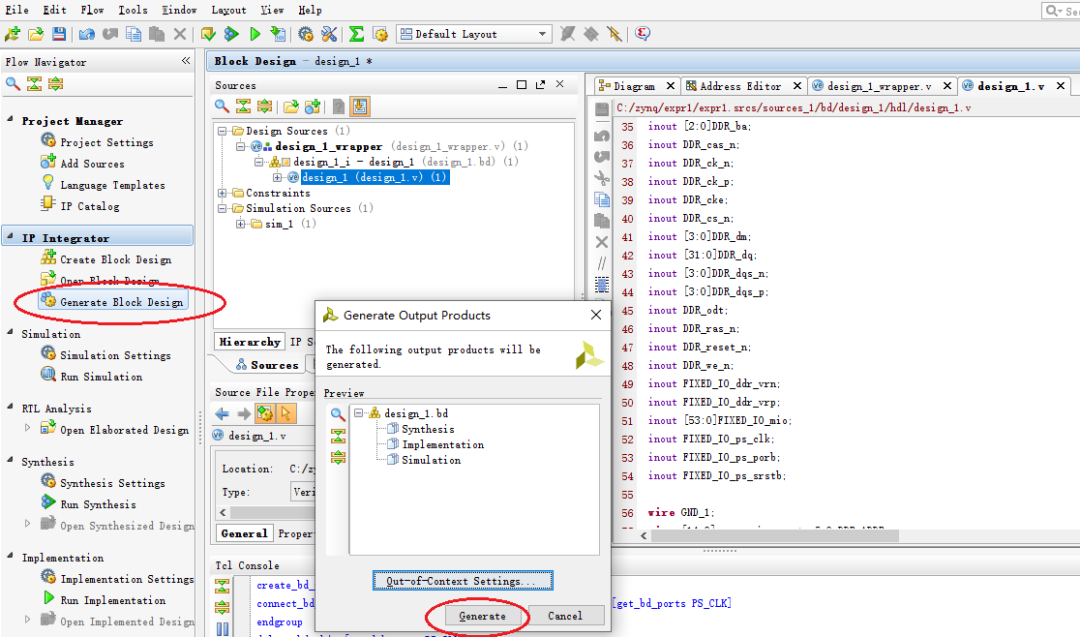

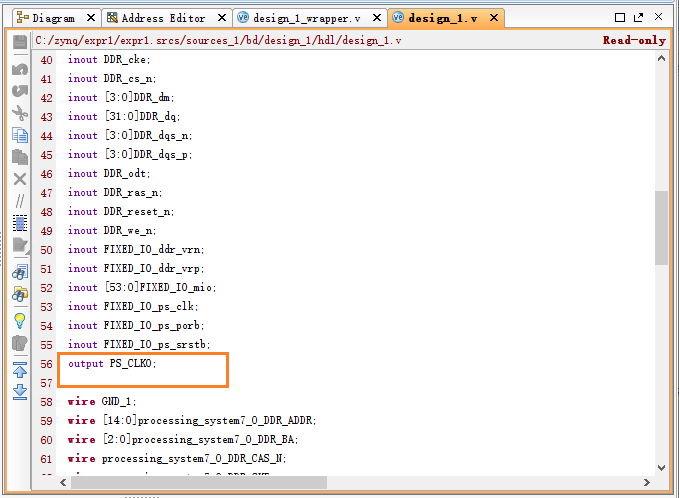

在圖上創建輸出port, 命名叫PS_CLK0, 連接到時鐘信號上。保存之后,design_1.v文件(自動生成的)并沒有體現新的輸出端口。于是我嘗試一下“Generate Block Design”操作,看看是否更新。

結果這樣是能重新產生design_1.v的:

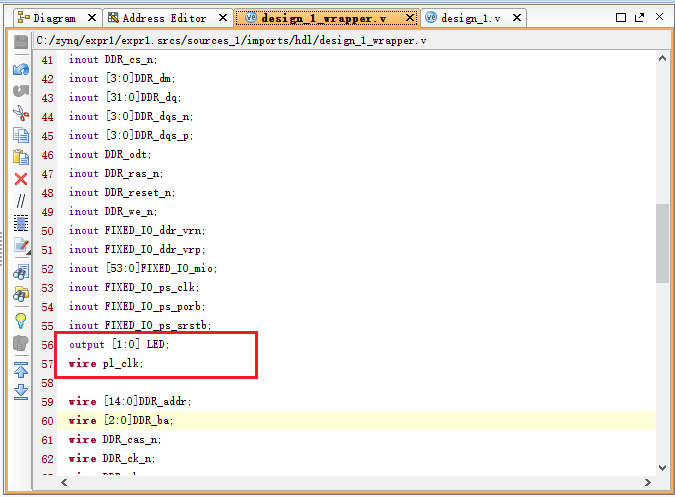

然后我就在頂層的design_1_wrapper.v里面加自己的東西了:先加上兩個輸出口給礦板上的紅綠LED。

再寫一個計數器,利用PS引出的時鐘計數,讓LED能閃起來。

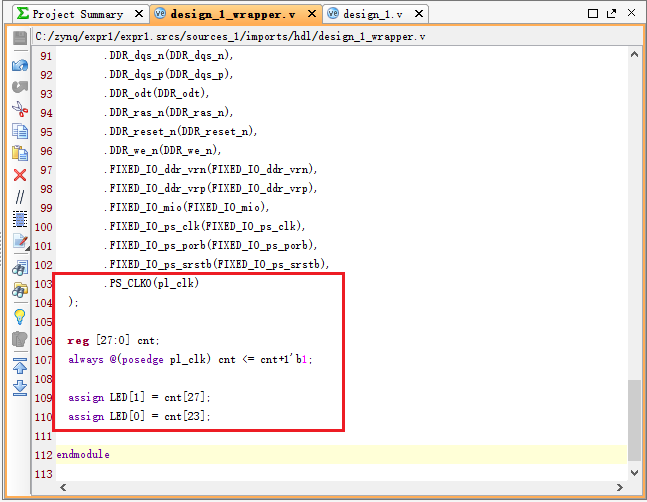

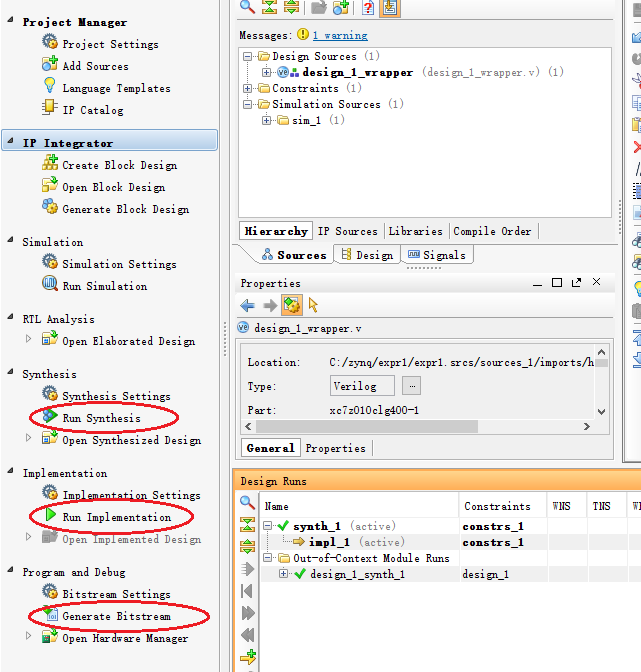

這樣第一個實驗工程的邏輯就設計完了,可以進行FPGA綜合、實現和生成二進制碼的流程了。

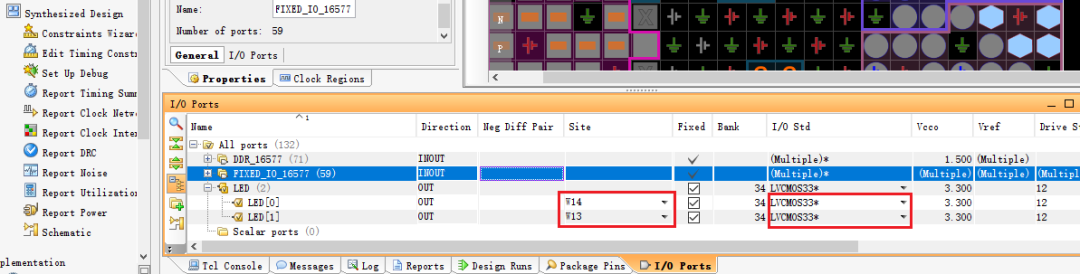

這里還缺少一件事情:礦板上的 LED6 (W13, W14引腳)是連接在FPGA IO上的,不是PS MIO,因此是像普通FPGA那樣分配引腳的方式。而DDR、MIO則是固定引腳,不需要自己選。假如LED是接在MIO上,那么我們就要用軟件去選擇GPIO訪問來點亮了,不屬于FPGA邏輯部分。

在綜合之后,可以查看design,然后手工分配LED使用的引腳。也可以直接寫一個約束文件(.xdc)把引腳約束用Tcl命令寫上去。

在最后Generate bitstream 生成bit文件之前看一下報告,確認引腳的分配是生效了的。

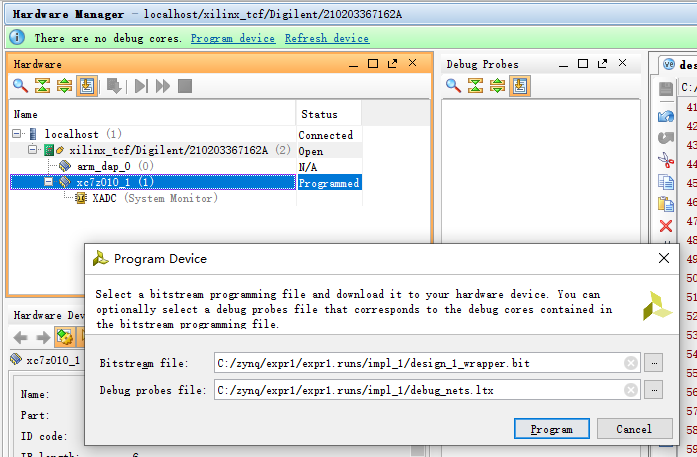

最后得到了.bit文件,就可以連接好JTAG之后,打開Hardware Manager, 將生成的design_1_wrapper.bit下載到FPGA中了。這個操作和Xilinx Spartan/Artix系列是相似的。

若此時看到了LED閃爍,說明PL部分的邏輯是工作的了。

此外,下載bit文件之后,從UART終端看到的Linux打印信息還在活動,說明PL部分的重配置沒有影響PS的運行。關于PL和PS的關系我的了解還不夠多。

如果單純把Zynq當成FPGA來用,不使用PS部分,也是可以的。注意,這樣也就不能用PS提供的時鐘了,需要從PL的引腳輸入時鐘信號。開發工具用Vivado和ISE都可以,我另外進行過嘗試。

審核編輯:劉清

-

ARM技術

+關注

關注

0文章

22瀏覽量

7416 -

UART接口

+關注

關注

0文章

124瀏覽量

15442 -

FPGA開發板

+關注

關注

10文章

124瀏覽量

31671 -

JTAG口

+關注

關注

0文章

6瀏覽量

1829

原文標題:多少“礦板”吃灰中:Zynq學習筆記——“礦板”小試FPGA開發流程

文章出處:【微信號:電子工程世界,微信公眾號:電子工程世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Xilinx Zynq-7010(兼容 7020)嵌入式開發板-Z-turn Board產品介紹

用于 Xilinx FPGA Zynq 7 的電源解決方案

面向Xilinx Zynq FPGA應用的PMP9335參考設計

基于Xilinx Zynq SoC的“小傻瓜(Snickerdoodle)”開發套件

用于 Xilinx FPGA Zynq 7 的電源解決方案

FPGA開發流程詳細解析

使用Xilinx SDK進行Zynq裸金屬應用程序開發

基于Xilinx Zynq SoC的“小傻瓜(Snickerdoodle)”開發套件

面向Xilinx Zynq FPGA應用的多路降壓20W電源參考設計

xilinx ZYNQ7000系列基本開發流程之PS端

Xilinx Zynq小試FPGA開發流程

Xilinx Zynq小試FPGA開發流程

評論