異構設計、定制和日益增加的復雜性帶來了很多硬件錯誤。

將芯片分解為專門的處理器、存儲器和架構對于持續改進性能和功率變得必不可少,但它也會導致硬件中異常且通常不可預測的錯誤,這些錯誤極難發現。

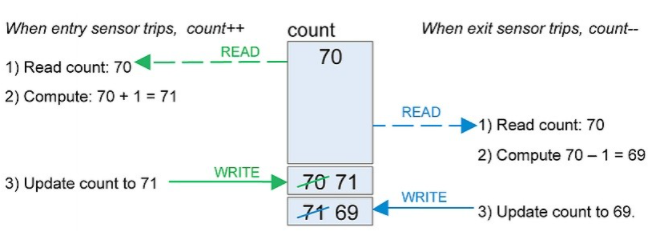

這些誤差的來源可能包括任何事情,從特定序列中的定時錯誤到封裝中芯片之間的鍵合間隙。隨著不同芯片或小芯片中的電路以不同的速度老化,以及隨著各種類型的壓力將潛在缺陷變成真正的缺陷,它們會隨著時間而改變。因此,計算有時可能會產生錯誤的結果——但并非每次都如此。如果互聯網搜索結果錯誤或流媒體視頻出現輕微故障,這不會引起注意,但當涉及金融交易、汽車安全或軍用無人機制導系統時,它的重要性就完全不同了。

這些類型的問題并不是全新的。有關該主題的技術論文在 2000 年代初期開始出現,討論了芯片中的意外行為和偶發故障。然而,他們現在已經達到了一個臨界點,問題已經足夠嚴重,數量也足夠多,值得關注。但出于多種原因,如何處理它們并不總是很清楚。他們之中:

有更多的組件密集地封裝在芯片上和封裝中,其中一些具有更薄的金屬層和電介質,以及更多的互連。這使得很難預測工藝變化、潛在和實際缺陷,甚至量子效應會在何處引起問題,或者以什么順序引起問題。

先進節點芯片正被用于比過去利用率更高的系統中,特別是在數據中心和人工智能應用中。這會增加這些設備上的機械和電氣應力,從而影響信號質量和時序。除此之外,其中一些系統被設計為更長的生命周期,需要定期的軟件更新,這可能會導致一些硬件組件隨著時間的推移表現不同。

設計變得更加異構和更加定制化,增加了特定設備獨有的可能交互的數量。此外,這些設備越來越多地使用在不同工藝節點開發的組件,有時由不同的代工廠制造,并非所有這些組件都具有相同的特征。

所有這些都增加了復雜性,使得所有極端情況變得更加困難、耗時和昂貴。

Synopsys研究員 Rob Aitken 說:“我們現在觀察到的這些問題是因為我們擁有了更大的芯片和更好的儀器,還是因為這是一種新的東西,存在疑問。”“無論哪種情況,這是可以在制造時識別的東西,還是識別它的行為會影響經濟收益?我最近和 IBM 的某個人參加了一個座談會,他說這就是大型機如此昂貴的原因。它們旨在尋找每一個可能的問題。”

懸而未決的問題是,這是否會成為對安全關鍵和任務關鍵硬件的要求。如果是這樣,解決它的最佳方法是什么。如果一切都必須完美,那將對產量和成本產生影響。但是,如果可以通過在系統中設計彈性來解決其中的一些問題,它可能有助于控制成本。

完美與彈性

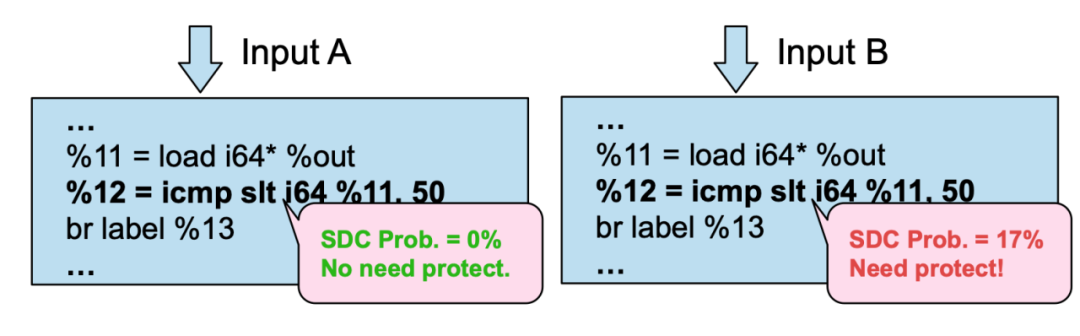

愛荷華大學、百度安全和阿貢國家實驗室聯手創建了 MinpSID(多輸入硬化選擇性指令復制),它識別“跨多個輸入的難以捉摸的錯誤傳播”。在一份新發布的技術論文中,研究人員聲稱已經找到了一種提高可靠性并識別導致這些錯誤的“孵化指令”的方法。

圖 1:孵化說明示例。來源:阿貢國家實驗室/愛荷華大學

這是這個謎題的一部分。但到目前為止,還沒有單一的可重復解決方案,而且未來是否會出現也不明顯。事實上,解決方案可能是特定于設計的,有時甚至是違反直覺的。

Movellus的電源架構師 Barry Pangrle 說:“我們看到一個案例,人們在構建電路時,在某些情況下,你可以對不同的計算組合進行統計分析,但有時會出現此錯誤。”“他們所做的是壓低電壓。他們知道它不會一直都符合時機,而且它會得出的結果基本上是誤報。他們將其用作篩選器以找到好的結果,并采用較小的集合并在真正強大的系統上運行它。現在的問題是一切都變得越來越復雜。隨著電路變老,它們往往會變慢。所以現在,從健康的角度來看,我們需要研究老化的技術,監控事物,有延遲循環和類似的東西,看看它是否隨著時間的推移而漂移。”

防止這些偶發錯誤需要首先了解它們的來源。但隨著定制芯片或小芯片的集合以及獨特架構的加速推出,這是一項非常重要的工作,可能會推高總體開發成本。雖然其中一些問題可以事后用軟件解決,但如果硬件本身是可編程的,它會更有效。這為設計增加了一定程度的彈性,以適應任何問題,而不會因修復軟件問題而影響功率/性能。

Flex Logix的 CEO Geoff Tate 說:“第一件事就是檢測出什么時候會出問題,然后再出問題。”“第二件事是為此做點什么。如果出現問題,你需要進行補償——就像人腦一樣。大腦中的神經元一直在死亡,但我們的通路可以再生。人們可能會對他們的大腦造成非常嚴重的損害,但大腦的其他部分可以隨著時間的推移重新編程以彌補它。現有的芯片不能那樣工作。唯一可以彌補它的是處理器或 FPGA,它可以通過編程來做不同事情的東西。”

弄清楚何時以及為什么會出現錯誤是值得花時間的,但在某些情況下,這可能意味著很多時間。Google 和 Meta 檢測到的靜默數據錯誤花了一年多的時間來追溯根本原因。并且通常在開發出整個芯片或封裝或在現場使用時才會出現問題。

Imperas Software首席執行官 Simon Davidmann 表示:“構建這些東西并將其整合到設備中的所有物理機制都存在挑戰。”“作為一個行業,你還面臨著如何在運行時驗證整個事物的挑戰。我們剛剛開始與一些公司在 SoC 級別進行合作,然后它會進入系統級別。但這是一個涉及系統系統的漫長而緩慢的過程。”

任何可以預先做的事情來找出潛在的問題都是有益的,這可能涉及物理和虛擬因素。

“熱分析發揮了作用,”是德科技副總裁兼總經理 Niels Faché 說。“如果電路板和 IC 中有熱點,隨著時間的推移,它會對設備的性能產生影響并導致其故障。我們看到越來越多的人重視熱分析,并且我們在其中添加了熱建模,因為這會改變電氣性能。機械分析可能也是如此。你可能會在電路板上發生變形,從而改變電氣參數。”

熱量對芯片或系統的行為方式構成嚴峻挑戰。“你必須密切關注熱梯度,”Ansys 半導體部門產品營銷總監 Marc Swinnen說。“這給出了不同的擴張。即使堆疊的頂部和底部之間只有 25° 的差異,考慮到這些設備的極薄,我們談論的是每厘米 10,000° 或該范圍內的某個值。對于這么短的距離,這是一個巨大的溫度梯度,這會導致相當大的壓力。”

制造和封裝缺陷

并非所有錯誤都是由于設計造成的。它們可能由設計到制造流程中任何一點的任何因素組合引起。事實上,它們可能表現為被認為是良性的潛在缺陷,例如納米級缺陷,或者它可能是在檢查和測試中被忽視的缺陷。并且其中一些缺陷可能要等到設備開始老化后才會顯現出來。

Cadence數字與簽核集團產品管理副總裁 Kam Kittrell 表示:“尤其是現在的 5nm,老化正在影響時序,所以你已經有了這些如何老化的模型”.“但是你怎么知道它在外面放了五年之前會如何老化呢?這意味著你必須仔細檢查這樣的事情。此外,如果你發現一個特殊的案例失敗了——可能是軟失敗,比如偶爾翻轉一下——這不是制造缺陷,但你可以在制造測試中做一些事情。你可以返回并使用已知的壞芯片重新進行制造測試,然后將測試分散到每個單元以查看鏈中是否存在薄弱環節。這有很多好處。云計算與汽車一起推動了這一點,因為現在汽車領域的復雜性已經超出了圖表。你的儀表盤上到處都有超級計算機在運行,當他們的汽車不能工作時,人們會很不安。”

更糟糕的是,隨著芯片或小芯片被引入并堆疊在先進的封裝中并被大量使用,或者由于這些設備中的任何一個以它們最初設計目的以外的方式使用,潛在的缺陷可能會變成真正的缺陷。并非所有這些都可以修復,但可以在它們成為問題之前識別出來。

“潛在缺陷更多地與熱機械方面有關,”proteanTecs業務發展高級總監 Nir Sever 說. “微凸塊可能有裂縫或空隙。車道可以有橋梁短褲。TSV 可能有裂紋、部分填充或側壁分層。由于模具不完美,會發生許多物理缺陷。但即使它們是完美的,當你開始組裝過程時,也有很多潛在的故障點。在典型的 HBM 中,大約有 10,000 條不同的通道。如果其中一個有缺陷,除非修復,否則該 SiP 將無法工作。所以你已經放下了所有這些微凸塊,你必須將它們組裝起來,使它們全部接觸。如果其中只有一個有缺陷,芯片變形,或者材料移動了一點并且沒有完全對齊,你將獲得影響信號質量的電阻行為。”

挑戰在于找出可能發生的地點和時間,以及如何準確識別問題。

“所以首先你必須能夠測試,因為產量不是 100%,”Sever 說。“很有可能至少有一條車道在組裝后會出現缺陷。其次,因為它正在老化,你需要在產品的整個生命周期中,在現場和任務模式下持續監控接口。如果它從一開始就處于邊緣狀態,因為存在未產生測試失敗的潛在缺陷,隨著時間的推移它會退化。

最終,時序余量或眼圖將開始閉合,你將在總線上遇到錯誤。這是一場災難,因為與在具有糾錯機制的 SERDES 中不同,在典型的 D2D 中你沒有。協議中不一定內置糾錯功能。你假設誤碼率幾乎為零,就像常規 I/O 一樣。這將導致數據錯誤,表現為靜默數據損壞,沒有人真正知道它們來自哪里。但事實是,數據開始在芯片內部某處損壞,你必須有辦法從內部進行測量,可視化數據,理解它,然后能夠追蹤根本原因并修復它。”

提高彈性

這就是彈性發揮作用的地方,而內存行業在這方面一直遙遙領先。例如,眾所周知,NAND 閃存會隨著時間的推移而退化。在它不再工作之前,你只能向閃存寫入這么多內容。

Flex Logix 的 Tate 說:“有一些磨損均衡算法可以在其中多放 30% 的位,這樣它們就可以在 10 年以上可靠地工作。”“但他們必須在它們變壞之前找到這些位,然后換上仍然好的位。對于彈性邏輯設計,你將需要嵌入式 FPGA 之類的東西,其中你有一些可用的未編程計算能力,可以承擔系統其余部分出現故障的任何內容。所有芯片都有錯誤。有一些錯誤會殺死芯片,因此它無法正常工作。有bug導致性能不好,所以無法發貨。還有各種你可以解決的錯誤。在我們的芯片中,我們有一個無法解決的錯誤,除了我們在處理器總線上有 4,000 個嵌入式 FPGA 查找表之外。我們能夠在該查找表上編寫一些 RTL 代碼,以彌補芯片其余部分中的錯誤。然后我們可以運送芯片,而客戶并不知道我們以這種方式修補了它。”

大多數彈性解決方案都依賴于某種程度的冗余。這可以包括可編程性,這減少了對全新電路的需求,它可以包括軟件,它效率低下但重新編程容易且相對便宜。在所有情況下,都會有一些開銷。關鍵是在選擇在功率、性能和面積/成本方面進行權衡時,將其保持在最低水平。因此,如果面積/成本至關重要,則添加在線監控可以代替添加的電路。如果功率至關重要,那么冗余可能會以可重新編程邏輯的形式出現。如果性能是最關鍵的因素,則可以添加額外的電路并根據出現問題的位置動態打開和關閉。

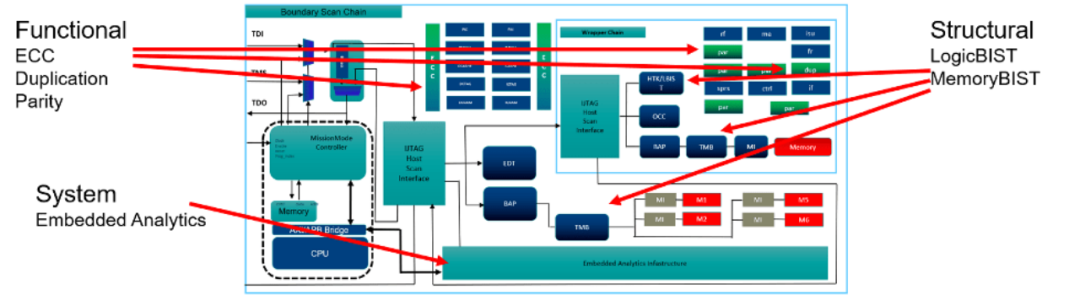

“這最終是一個經濟學問題,”Siemens Digital Industries Software的 Tessent Embedded Analytics 產品經理 Richard Oxland 說. “無聲數據錯誤給我們造成的損失是否超過了擁有冗余計算的硅片成本?這是一個大多數半導體公司無法回答的問題,因為這是一個系統級問題。它需要更好地了解靜默數據錯誤的經濟影響。如果你想想 Meta、谷歌或 AWS,那很快就會變成非常高度專有的信息。如果這些要求變得有意義,這些人將開始降低這些要求。我們可能并不總是知道這一點,因為他們正在設計自己的芯片。所以在你的系統中,你可以在那里有一些冗余。或者在 NoC 中,你可以做一些聰明的事情,比如路由來避免問題。”

不過,這增加了另一層復雜性,因為復雜設計中不只有一個 NoC。可以有很多,需要在整個系統的上下文中查看它們。“然后你必須開始處理 NoC 之間的時序,因為它們沒有完全同步,”Arteris IP解決方案和業務開發副總裁 Frank Schirrmeister 說。“你必須處理外設連接的時序,以及各種時鐘域交叉。”

Schirrmeister 說,在這幅圖景中增加彈性是一項挑戰,但使用分而治之的策略比試圖立即解決整個問題更容易使各個部分具有彈性。“你不想同時處理一堆信號。因此,如果你正在查看安全說明,例如,你可以添加檢查器以確保其正常運行。”

彈性在汽車領域引起了廣泛關注,該領域的芯片被用于對安全至關重要的應用,并且法規要求進行某種形式的故障轉移。“汽車行業一直對其半導體的可靠性充滿熱情,”Oxland 說。“一些大型供應商在這個領域活躍了一段時間,比如 NXP 等——非常擅長這類事情。該應用程序的復雜性可能略低,因為我們談論的是 ECU。但總的來說,它們的部署數量巨大——盡管它們在運行方式方面更具確定性。由于大規模運行非常高度并行化的工作負載的復雜性,我們現在看到了靜默數據錯誤的問題,所以它更像是一個新問題。

極端的權衡

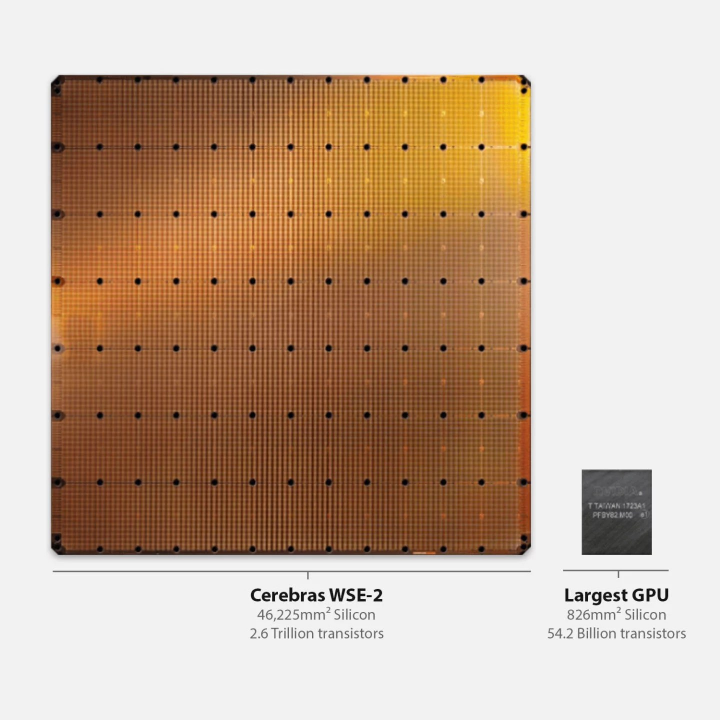

當 Cerebras 開發其晶圓級芯片時,它認識到沒有任何東西可以 100% 地產出,并且芯片的某些部分——從整個晶圓上切下的 800 平方毫米的正方形——會以不同于其他部分的方式老化,并且潛在的缺陷會變成真正的缺陷。

“從歷史上看,DRAM 實現非常高產量的方式是擁有冗余的位單元行和列,”Cerebras 的首席執行官安德魯費爾德曼說。“我們有 850,000 個相同的可編程元件,這是一個核心加內存加一個小路由器。它用電線連接到下一個。每個可編程元素都與其四個鄰居中的每一個相關聯,并通過冗余鏈接與其鄰居的鄰居相關聯,從而使其能夠與其鄰居對話。我們所做的是構建一個測試芯片,并與臺積電合作處理他們的良率數據。如果代工廠在控制范圍內工作,你應該擁有的是隨機分布的缺陷。這樣一來,冗余應該可以讓你找出缺陷。所以當我們說我們有 850,000 個核心時,我們實際上有 870,000 個左右的核心,因為我們將保留大約 1.5%。”

圖 3:晶圓級芯片內置約 1.5% 的冗余度。

費爾德曼說,其他關鍵部分是在映射之前燒入,并將芯片暴露在超出規范的溫度下。“從那里開始,自檢會檢查每個核心以及每個核心之間的每條電線的行為,”他說。“如果失敗,它會激活繞過路由協議并重新進行自檢。所以有一個硬件自檢在啟動時運行,然后定期運行。”

雖然這對大多數應用程序來說仍然不切實際,但它確實證明了一點。通過足夠的努力和創新,這些問題中的大部分都可以得到解決。挑戰在于確定應用程序可接受的權衡,然后真正理解這些權衡實際上需要什么。在當今的硬件和系統設計中,并非所有這些都是顯而易見的。

結論

所有這些都指向一個更廣泛的問題,即管理由于更密集的電路、更多的定制和功能、新材料和不同的使用模式而導致的復雜性增加的能力。結果,未知數呈爆炸式增長。并非所有這些都可以被完全理解或調試,但對于許多應用程序來說,這是可以接受的。但對于任務關鍵型和安全關鍵型應用程序,故障規劃至關重要。

不可能在緊迫的市場窗口內抓住一切,但只要有足夠的時間和努力,似乎可以制造出能夠應對大多數問題的芯片。毫無疑問,需要在更多芯片中構建彈性。解決方案這是一個如何以可接受的價位獲得足夠彈性的問題。芯片行業才剛剛開始認真看待這個問題。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19264瀏覽量

229666 -

FPGA

+關注

關注

1629文章

21729瀏覽量

603025 -

存儲器

+關注

關注

38文章

7484瀏覽量

163768 -

SID

+關注

關注

0文章

14瀏覽量

3026

原文標題:怎樣查找芯片設計中的偶發錯誤?

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種可在線更新的PET實時查找表電路的設計與實現

一種使用無源RFID替代EEPROM代碼芯片來存儲血糖試紙的方法介紹

嵌入式C語言程序軟件中的缺陷怎么查找?

一種利用調試軟件Valgrind進行嵌入式應用程序錯誤查找的技術

介紹一種嵌入式系統仿真方法

一種系統芯片的功能測試方法

抗突發錯誤的短碼長隨機LDPC碼設計

一種錯誤簽名混合篩選算法

干貨 | 電機控制器出現的一種偶發故障排查與分析

介紹一種查找芯片設計中偶發錯誤的方法

介紹一種查找芯片設計中偶發錯誤的方法

評論