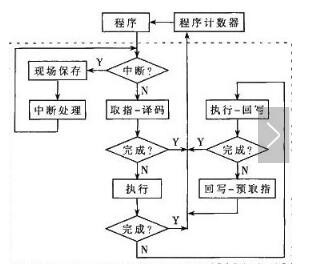

雙擊QQ.exe從磁盤加載到內(nèi)存里面,內(nèi)存里面就會(huì)有了一個(gè)進(jìn)程,進(jìn)程產(chǎn)生的時(shí)候會(huì)產(chǎn)生一個(gè)主線程,就是main方法所在的線程,cpu會(huì)找到main開始的地方,把它的指令讀取過來放到程序計(jì)數(shù)器,把數(shù)據(jù)放到寄存器,然后ALU開始做計(jì)算,一步一步來執(zhí)行整個(gè)程序,這就是普通程序執(zhí)行的過程。

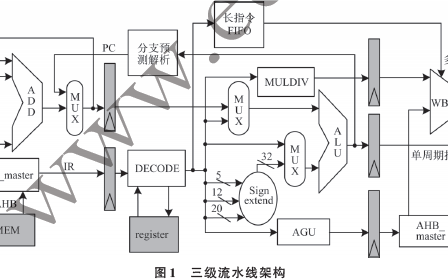

cpu速度要比內(nèi)存的速度快100倍,中間有各種各樣的緩存,最常見的是三級(jí)緩存,由于它的速度非常快,在執(zhí)行指令的時(shí)候也會(huì)有一些優(yōu)化,比如現(xiàn)在有2條指令,一個(gè)是mov指令即從內(nèi)存中讀取一個(gè)數(shù)據(jù)到某一個(gè)寄存器中,第二個(gè)指令是把寄存器中的指令數(shù)值加1,如果嚴(yán)格按照前后寫的效率執(zhí)行,會(huì)發(fā)現(xiàn)它的效率比較低;第一條指令從內(nèi)存中讀數(shù)據(jù)出來,cpu等待99個(gè)時(shí)間周期,如果讀完第一個(gè)指令之后,才可以執(zhí)行第二個(gè)指令的話,cpu將會(huì)有99個(gè)空檔期,所以現(xiàn)在的cpu設(shè)計(jì)是流水線式的設(shè)計(jì)(采用流水線式后,并沒有加速單條指令的執(zhí)行,每條指令的操作步驟一個(gè)也不能少,只是多條指令的不同操作步驟同時(shí)執(zhí)行,因而從總體上看加快了指令流速度,縮短了程序執(zhí)行時(shí)間),發(fā)送一條指令在等待內(nèi)存數(shù)據(jù)返回的過程當(dāng)中,會(huì)把后面這條指令執(zhí)行了即后面的指令跑到前面先執(zhí)行了,簡(jiǎn)單稱為cpu的亂序執(zhí)行,主要是為了提高效率,在等待費(fèi)時(shí)的指令執(zhí)行的時(shí)候,優(yōu)先執(zhí)行后面的指令。

證明cpu亂序執(zhí)行是存在的

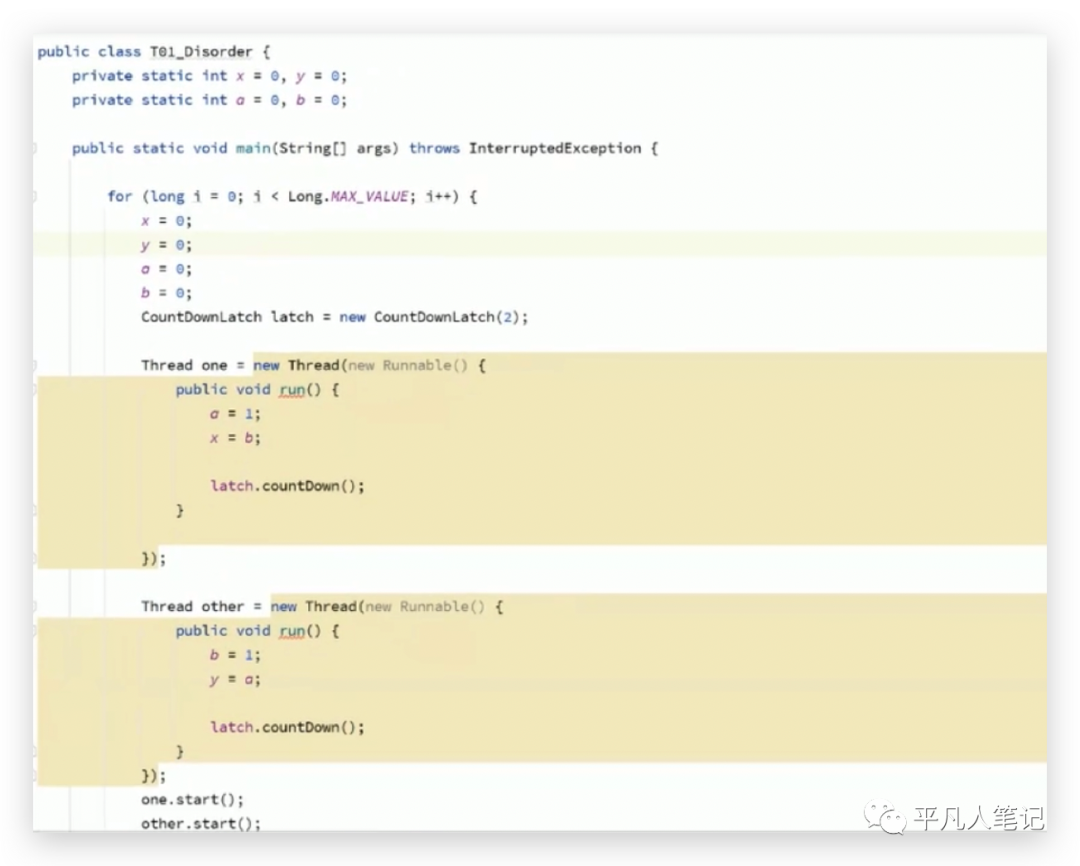

這里有個(gè)死循環(huán),每一次循環(huán)都會(huì)把這4個(gè)值(x、y、a、b)設(shè)置為0,每一次循環(huán)都會(huì)起2個(gè)線程,第一個(gè)線程會(huì)執(zhí)行a=1、x=b,第二個(gè)線程會(huì)執(zhí)行b=1、y=a;假設(shè)所有的語句都是按照順序執(zhí)行的,從多線程微觀的角度進(jìn)行時(shí)間順序上的排列組合,你會(huì)發(fā)現(xiàn)會(huì)有各種各樣的組合場(chǎng)景:

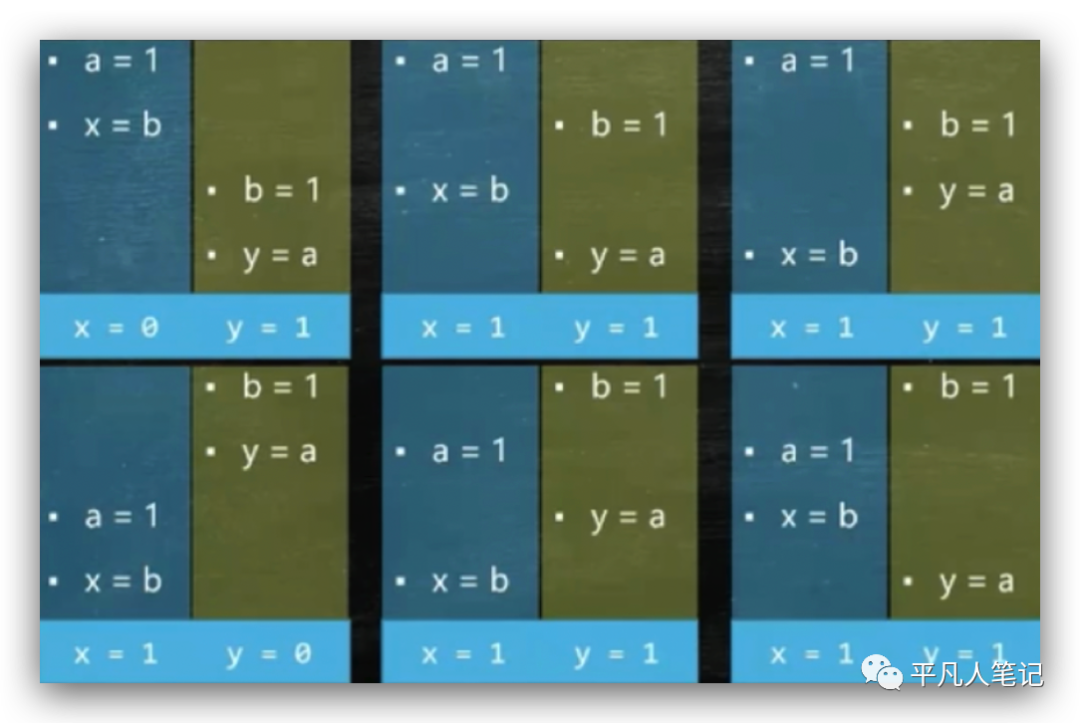

比如第一種組合,

第一種組合先執(zhí)行a=1、x=b,后執(zhí)行b=1、y=a,得到的結(jié)果是x=0、y=1。

這6種排列組合的結(jié)果無論如何都不可能得到x=0、y=0的情況即只要按照順序執(zhí)行,絕對(duì)不會(huì)出現(xiàn)x=0、y=0。

這是數(shù)學(xué)上的排列組合,但cpu執(zhí)行指令的時(shí)候未必是按照順序執(zhí)行的。

出現(xiàn)x=0、y=0的情況比較少見,為什么這么難出現(xiàn)?什么樣的組合下才會(huì)出現(xiàn)?

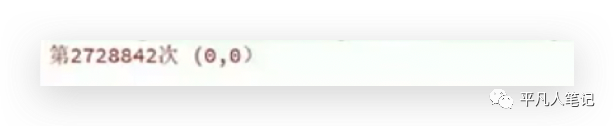

跑了270多萬次才出現(xiàn)了一次x=0、y=0的情況,

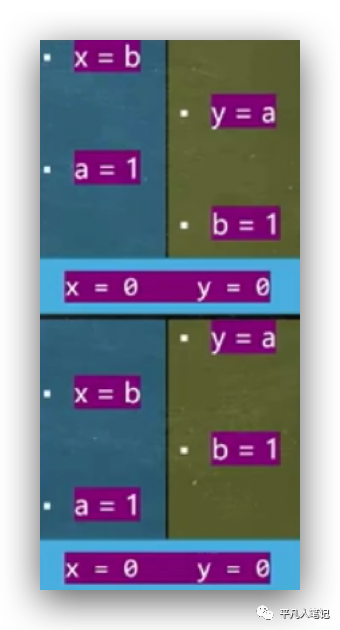

這兩種是亂序執(zhí)行的排列組合,比如第一個(gè)場(chǎng)景是線程1先執(zhí)行x=b、線程2執(zhí)行y=a,切換到線程1執(zhí)行a=1,切換到線程2執(zhí)行b=1,結(jié)果是x=0、y=0。

只有這2種場(chǎng)景,2個(gè)線程的這2個(gè)指令都得顛倒順序才會(huì)出現(xiàn),這種很難出現(xiàn),不管怎樣,得出一個(gè)結(jié)論:cpu內(nèi)部是亂序執(zhí)行的。

單線程的情況下,2個(gè)指令亂了順序執(zhí)行沒有關(guān)系,反正最終的結(jié)果是一樣的,但是在多線程的情況下,非常有可能出現(xiàn)你不想看到的情形,比如x=0、y=0的情況,比如在預(yù)知中沒有這種情況,但是多線程的情況下,會(huì)出現(xiàn),所以一定會(huì)影響整個(gè)多線程程序的運(yùn)行,單線程的程序不會(huì)影響。

有了as-if-serial(看上去像序列化的)指令就可以隨便變換順序,只要維持最終一致性即可;單線程的重排序只需要保證最終的一致性,比如a=b、y=1,隨便重排序,只要能保證單線程的最終一致性。

審核編輯:劉清

-

寄存器

+關(guān)注

關(guān)注

31文章

5343瀏覽量

120430 -

cpu

+關(guān)注

關(guān)注

68文章

10870瀏覽量

211880 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2256瀏覽量

94607 -

ALU

+關(guān)注

關(guān)注

0文章

33瀏覽量

13104

原文標(biāo)題:證明CPU指令是亂序執(zhí)行的

文章出處:【微信號(hào):IC學(xué)習(xí),微信公眾號(hào):IC學(xué)習(xí)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

單片機(jī)執(zhí)行指令過程詳解

CPU指令的條件執(zhí)行分享!

CPU周期與微指令周期的關(guān)系

什么是CPU分枝/亂序執(zhí)行?

CPU操作指令詳解

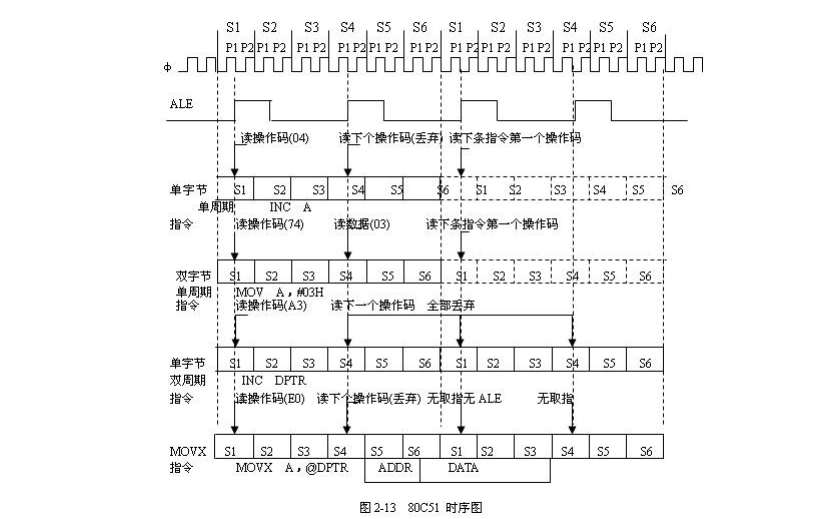

80C51單片機(jī)指令的取指和執(zhí)行時(shí)序詳細(xì)說明

嵌入式RISC-V亂序執(zhí)行處理器的設(shè)計(jì)方案

超標(biāo)量處理器的指令亂序提交機(jī)制綜述

單片機(jī)是怎么執(zhí)行指令的?

CPU指令的執(zhí)行過程 CPU指令流水線

證明CPU指令是亂序執(zhí)行的

當(dāng)我們?cè)谡務(wù)?b class='flag-5'>cpu指令亂序的時(shí)候,究竟在談?wù)撌裁矗?/a>

編譯器的亂序策略

如何證明CPU指令是亂序執(zhí)行的呢?

如何證明CPU指令是亂序執(zhí)行的呢?

評(píng)論