System Verilog(SV)語言的Class本身就帶有“打包”的基因。眾所周知,SV語言的很多特性是派生自C++語言的。C++的class就把變量、參數(shù)以及相關(guān)的處理操作都打包在一起了。SV的class也天然具備了這個(gè)品性。關(guān)于這點(diǎn)本文不過多贅述,只談?wù)勁c驗(yàn)證者編碼時(shí)可真真切切直觀感受到的那些“打包”的操作痕跡。

Chapter1. config_file(cfg)

驗(yàn)證者在驗(yàn)證平臺(tái)中定義的參數(shù)和變量,既可調(diào)整仿真的行為,也可約束配置的范圍,是對(duì)驗(yàn)證平臺(tái)的必要的裝點(diǎn)和修飾。若把驗(yàn)證平臺(tái)比作一個(gè)姑娘,那么參數(shù)和變量就像是姑娘身上的發(fā)卡、耳環(huán)、項(xiàng)鏈和手表。

通常驗(yàn)證者會(huì)創(chuàng)建一個(gè)config_file(cfg),在其中定義參數(shù)和變量。對(duì)于一些rand變量,也會(huì)在該文件中定義相關(guān)的constraints。同時(shí),也會(huì)在該cfg文件中對(duì)全部的變量參數(shù)進(jìn)行注冊(cè)(register)。

關(guān)于這種做法,有同學(xué)難免要問:在驗(yàn)證平臺(tái)組件中,直接定義要用的參數(shù)或變量,不香么?隨時(shí)要用,隨手定義。

閔老師覺得,這個(gè)世界上絕對(duì)的事情非常稀少,尤其是在成年人的世界,非黑即白,從來鮮有。這也是他多年成長(zhǎng)的領(lǐng)悟之一。

具體來說,與在組件中直接定義參數(shù)和變量相比,統(tǒng)一定義,即用cfg文件“打包”全部的參數(shù)和變量,有三點(diǎn)好處:兩小一大。

小的好處1:rand變量可統(tǒng)一隨機(jī),即通過執(zhí)行cfg.randomize()實(shí)現(xiàn)全部cfg內(nèi)的rand變量都根據(jù)定義的constraint進(jìn)行隨機(jī)。一步操作,生成全部變量的隨機(jī)值。

小的好處2:可統(tǒng)一將全部隨機(jī)參數(shù)和變量,在cfg中進(jìn)行注冊(cè)。

大的好處:集中管理全部的參數(shù)和變量。舉例說明:

其一,參數(shù)變量都在cfg中,review代碼比較方便,提升了代碼規(guī)范性和可讀性。

其二,涉及到參數(shù)和變量的訪問可都通過訪問cfg實(shí)現(xiàn),操作方便。

其三,可通過傳遞cfg句柄的方法實(shí)現(xiàn)全部的參數(shù)和變量的“打包”傳輸。

其四,統(tǒng)一隨機(jī)全部rand變量。

其五,可通過繼承擴(kuò)展(extend)cfg文件,或直接實(shí)例化cfg所在驗(yàn)證平臺(tái),實(shí)現(xiàn)對(duì)cfg的重用,進(jìn)而實(shí)現(xiàn)對(duì)該驗(yàn)證平臺(tái)的參數(shù)和變量的重用,也提升了驗(yàn)證平臺(tái)的重用性。

姑娘通常會(huì)找一個(gè)包統(tǒng)一放置她們的發(fā)卡、耳環(huán)、項(xiàng)鏈和手表,驗(yàn)證者也應(yīng)該寫一個(gè)cfg文件統(tǒng)一“打包”變量和參數(shù)。

Chapter2. interface.clock_block

interface文件本身就把一個(gè)接口的全部信號(hào)打包在一起了。而clock_block可認(rèn)為是二次打包。即針對(duì)同一接口的信號(hào),進(jìn)行了統(tǒng)一的時(shí)鐘同步處理和setupTime_holdTime的行為模擬。

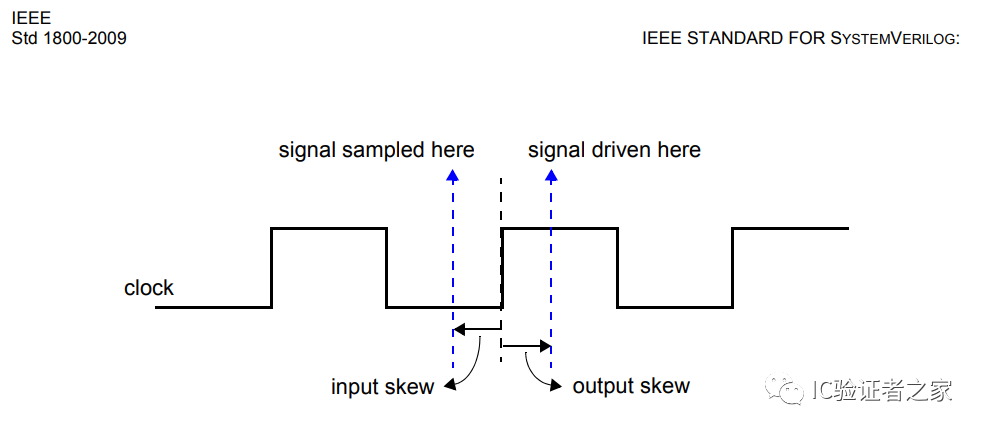

圖3input skew & output skew

在上圖中,input skew可等價(jià)于setup time,Output skew可等價(jià)于hold time。在仿真中,clock block的信號(hào)的采樣時(shí)刻應(yīng)該是clock有效邊沿之前input skew時(shí)間的時(shí)刻。新的數(shù)據(jù)驅(qū)動(dòng)到接口的時(shí)刻是clock有效邊沿之后經(jīng)過output skew時(shí)間的時(shí)刻。

在clock block中定義的信號(hào)是有方向性的,這個(gè)方向是相對(duì)于TestBench或DUT而定的。參照系不同,方向也就不同。為了解決這個(gè)問題,SV又定義了modport。驗(yàn)證者在interface中可通過modport把不同參照系的clock block分別進(jìn)行實(shí)例化,以便分開使用。該操作也可看做是對(duì)clock block的“打包”。如此這般,經(jīng)過對(duì)接口信號(hào)的三次“打包”,可整體統(tǒng)一處理接口信號(hào)的驅(qū)動(dòng)和采樣,也提升了代碼的規(guī)范性和清晰度。

Chapter 3. checker_scoreboard

Scoreboard,也叫計(jì)分板,是針對(duì)一種特定的事務(wù)進(jìn)行統(tǒng)計(jì)的裝置。例如在基于令牌(Token)的Cache Coherence協(xié)議中,就通過scoreboard統(tǒng)計(jì)Token的數(shù)目。

圖4 scoreboard

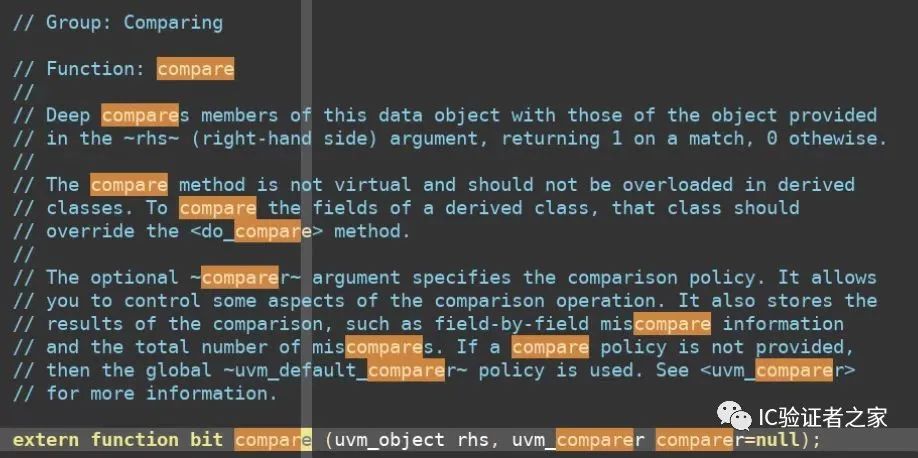

在驗(yàn)證者看來,scoreboard是針對(duì)一種特定的報(bào)文(transaction)進(jìn)行自動(dòng)化的比對(duì)和結(jié)果統(tǒng)計(jì)的組件。報(bào)文是擴(kuò)展自u(píng)vm_sequence_item,報(bào)文的比對(duì)函數(shù)compare()也在uvm_sequence_item的父類uvm_object中被定義好了。因此,一個(gè)scoreboard可實(shí)現(xiàn)一種特定報(bào)文的檢查。

圖5 UVM中的compare函數(shù)

當(dāng)需要檢查多種報(bào)文該怎樣做?直接在環(huán)境頂層文件env中實(shí)例化多個(gè)scoreboard嗎?

從“打包”的角度看,直接定義多個(gè)scoreboard不好。會(huì)顯得代碼組件分布的有些散亂,就像把各色的盤子零散的放到了廚房的各個(gè)角落。還是建議把各個(gè)scoreboard也“打包”一下。創(chuàng)建一個(gè)專門的組件中,姑且給他命名為checker。再將各個(gè)scoreboard實(shí)例化到checker中。最后只需要再在env中實(shí)例化一個(gè)checker組件。

這樣一來,checker組件作為專門負(fù)責(zé)檢查報(bào)文的組件,在驗(yàn)證平臺(tái)中占據(jù)了重要的一席之地,不僅所有的scoreboard也都?xì)w他管理,而且環(huán)境中定義的一些動(dòng)態(tài)比對(duì)操作,檢查RTL信號(hào)的操作,也可“打包”放置到checker中。就像櫥柜收納了所有的盤子碗碟后廚房變得整潔了,checker組件使得驗(yàn)證平臺(tái)變得規(guī)整了很多。

Chapter 4. agent_drv/mon/seqr/transaction

有一天,幾個(gè)驗(yàn)證同學(xué)在教室里聊天,有個(gè)同學(xué)提了一個(gè)問題:“transaction是報(bào)文,sequence管理報(bào)文,sequencer發(fā)送報(bào)文,driver將事務(wù)級(jí)的報(bào)文按時(shí)序驅(qū)動(dòng)到接口,monitor把接口的時(shí)序采樣成事務(wù)級(jí)的報(bào)文。他們似乎已把接口的行為模型要干的活兒都干完了,為啥UVM還要搞一個(gè)agent?這個(gè)家伙在接口數(shù)據(jù)流的行為模擬中,除了把sequencer和driver連接起來,也沒有啥具體的或者實(shí)質(zhì)性的工作,為啥UVM還把整個(gè)接口行為模擬相關(guān)的多個(gè)組件組合起來稱為agent。”

“憑啥?怎么看怎么像是一個(gè)尸位素餐卻身居高位的閑人。”提問的同學(xué)越說越生氣。

“其實(shí)這里有“打包”的思想的影子呢。”閔老師走進(jìn)教室,輕輕拍了拍那同學(xué)的肩膀,讓他坐下。“如果沒有agent,各個(gè)接口行為模型的各個(gè)組件散落開來,那么驗(yàn)證平臺(tái)會(huì)多么散亂呀,尤其是當(dāng)DUT有多個(gè)接口,需要開發(fā)多個(gè)接口的行為模型時(shí)。驗(yàn)證者要怎么安置這些driver,monitor,sequencer呢,直接把它們都實(shí)例化到env中去嗎,那豈不是亂了套了。咱們是高三16班,試想下如果沒有分班,整個(gè)年級(jí)的學(xué)生都做在一起,那可怎么上課。”

“哦,我明白了,就是把a(bǔ)gent當(dāng)成一個(gè)空空的口袋,把接口行為模型的那些代碼都裝進(jìn)去,打個(gè)包,方便存取。”同學(xué)恍然大悟,“我媽也買了一個(gè)大衣柜,專門用來放她的成堆的衣服、鞋包。”

Chapter5. virtual_sequencer/virtual_sequence

曾經(jīng)有位驗(yàn)證者說過,UVM定義的virtual sequencer有點(diǎn)“雞肋”。雞肋者,食之無味,棄之可惜也。用uvm_do_on發(fā)送sequence時(shí),可以直接使用各個(gè)agent.sequencer。定義的virtual sequencer也只是在其中把各個(gè)agent的sequencer聲明一下,然后需要把各個(gè)agent.sequencer的句柄指向該virtual sequencer中聲明的各個(gè)sequencer。實(shí)質(zhì)上,還是用的各agent.sequencer。

既然這樣,何必多此一舉呢?

揣測(cè)UVM定義virtual sequencer的初衷,應(yīng)該也是“打包”的思想。通過virtual sequencer把各個(gè)agent.sequencer“打包”在一起,或在test case中直接使用,或傳輸?shù)絭irtual sequence中使用都方便很多,代碼也會(huì)整潔很多。

剛提到了virtual sequence。當(dāng)構(gòu)造一個(gè)復(fù)雜的場(chǎng)景時(shí),需要多個(gè)sequence進(jìn)行配合。把多個(gè)sequence“打包”在一起,形成一個(gè)big-sequence。這便是virtual sequence。從此角度看,這也是“打包”思想的體現(xiàn)。

至此,我們的示例也講完了。

從上述五個(gè)章節(jié)可知,“打包”思想實(shí)質(zhì)就是八個(gè)字:分類整理,集中存放。“打包”思想在UVM中比比皆是。UVM發(fā)明者當(dāng)初是怎么想到的呢?或許這本是一種來自生活的普遍的常識(shí),也或許這種思想在其他語言的程序代碼開發(fā)中早已普遍的存在,又或許是別的原因。但有一點(diǎn)是可以確定的:程序員編碼的世界和人們生活的世界,其實(shí)存在很多的共通之處。這些共通之處,就像樹梢的果子,果香四溢,閃閃發(fā)光。靜靜的等著程序猿們?nèi)グl(fā)現(xiàn),去摘取。

審核編輯:劉清

-

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1297瀏覽量

104098 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110163 -

C++語言

+關(guān)注

關(guān)注

0文章

147瀏覽量

7009 -

DUT

+關(guān)注

關(guān)注

0文章

189瀏覽量

12425

原文標(biāo)題:淺談IC驗(yàn)證中的打包思想

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

新能源電池產(chǎn)業(yè)鏈及投資機(jī)會(huì)簡(jiǎn)析-磷酸亞鐵鋰

數(shù)字IC簡(jiǎn)析

嵌入式系統(tǒng)硬件抽象層的設(shè)計(jì)思想簡(jiǎn)析

淺談IC設(shè)計(jì)驗(yàn)證中的打包思想

電動(dòng)汽車用鋰離子電池技術(shù)的國(guó)內(nèi)外進(jìn)展簡(jiǎn)析

PCB線路板電鍍銅工藝簡(jiǎn)析

EPON技術(shù)簡(jiǎn)析

筆記本屏幕亮度與反應(yīng)速度簡(jiǎn)析

簡(jiǎn)析BGA封裝技術(shù)與質(zhì)量控制

鼠標(biāo)HID例程(中)簡(jiǎn)析

簡(jiǎn)析光耦電路中為何有串聯(lián)與并聯(lián)電阻資料下載

巖土工程監(jiān)測(cè)中振弦采集儀的布設(shè)方案及實(shí)施步驟簡(jiǎn)析

IC驗(yàn)證中的打包思想簡(jiǎn)析

IC驗(yàn)證中的打包思想簡(jiǎn)析

評(píng)論