跨時鐘域(Clock Domain Crossing,CDC)作為數(shù)字芯片設計中的經(jīng)典問題,也歷來是各面試官常問的問題。今天我們來分析一下跨時鐘域的相關問題,希望對你有所啟發(fā)。

一、什么是時鐘域?

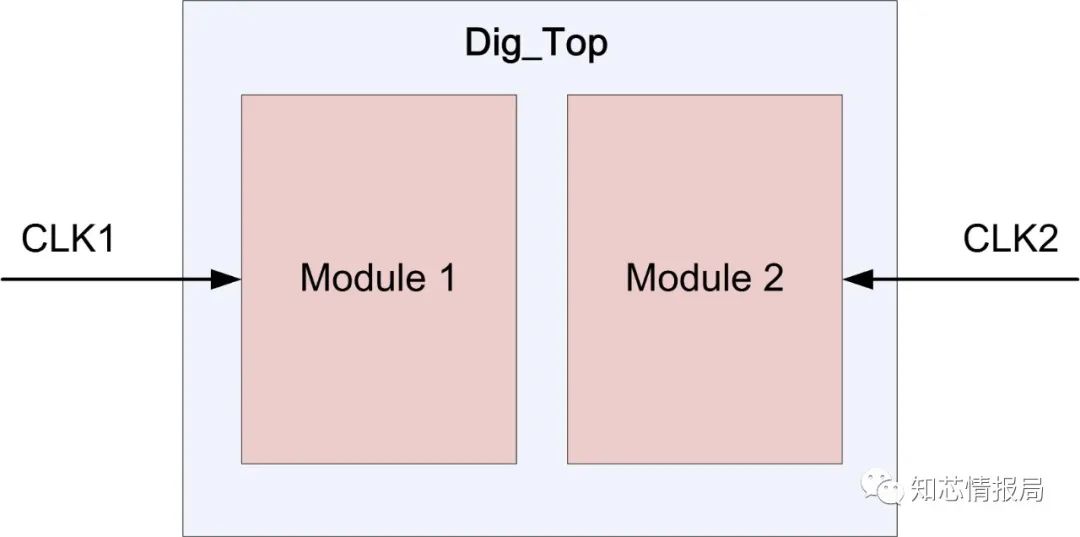

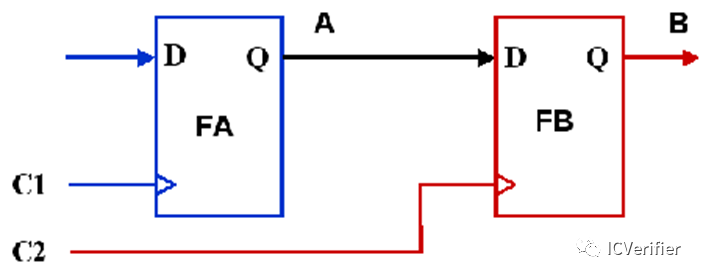

在一些較為簡單的數(shù)字電路中,只有一個時鐘,即所有的觸發(fā)器都使用同一個時鐘,那么我們說這個電路中只有一個時鐘域。對于功能較為復雜的芯片,如下圖所示,電路中往往存在多個時鐘,不同的模塊使用不同的時鐘,那么我們說這個設計中有多個時鐘域。當信號在不同時鐘域之間傳輸時,就被稱為跨時鐘域。

二、什么是亞穩(wěn)態(tài)?

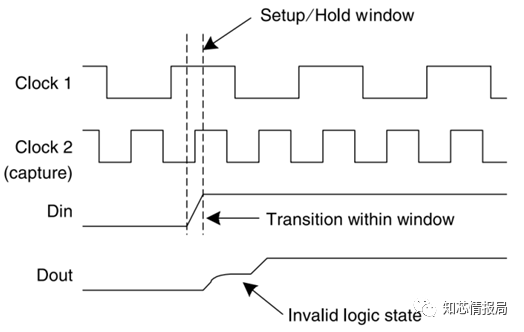

當數(shù)字信號跨時鐘域傳輸時,就會產(chǎn)生亞穩(wěn)態(tài)問題。亞穩(wěn)態(tài)是指觸發(fā)器無法在某個規(guī)定時間段內(nèi)達到一個可確認的狀態(tài)。每一個觸發(fā)器都有其規(guī)定的建立(setup)和保持(hold)時間參數(shù), 在這個時間窗口內(nèi), 輸入信號在時鐘的上升沿是不允許發(fā)生改變的。如果觸發(fā)器的數(shù)據(jù)輸入端口上數(shù)據(jù)在這個時間窗口內(nèi)發(fā)生變化(或者數(shù)據(jù)更新),那么就會產(chǎn)生時序違規(guī),觸發(fā)器的輸出將徘徊在不可預知的電平狀態(tài),即亞穩(wěn)態(tài)。

如下圖所示,在CLK2的上升沿到來的時候,觸發(fā)器Din的數(shù)據(jù)在發(fā)生變化,那么Dout的數(shù)據(jù)將會徘徊在一個中間電平狀態(tài)(這個中間電平可能正確值,也可能是錯誤值)。也就是說,電路處于中間態(tài)的時間變長,使得電路“反應”遲鈍,這就是“亞穩(wěn)態(tài)”。亞穩(wěn)態(tài)信號的穩(wěn)定時間通常比一個時鐘周期要短的多。

一般情況下不會超過一個或者兩個周期,取決于觸發(fā)器的性能。如果亞穩(wěn)態(tài)超過一個或者兩個周期,那么就會被下一個觸發(fā)器采樣到,這樣就會造成亞穩(wěn)態(tài)的傳播。但是需要強調(diào)的是,如果產(chǎn)生亞穩(wěn)態(tài),亞穩(wěn)態(tài)恢復穩(wěn)定后的電平不一定是正確的電平,如果穩(wěn)定后的電平是錯誤的,那么就很有可能引起后面的邏輯的錯誤。

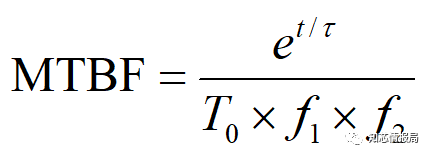

再深入一點,觸發(fā)器進入亞穩(wěn)態(tài)的時間可以用參數(shù) MTBF(mean time between failures)來描述, MTBF即觸發(fā)器采樣失敗的時間間隔,其公式描述如下:

其中:

t:在不引起synchronizer failure的前提下,亞穩(wěn)態(tài)持續(xù)的最長時間

τ和T0:觸發(fā)器工藝相關的參數(shù)

F1:輸入的異步信號頻率

F2:起同步作用的的觸發(fā)器時鐘頻率

通常,MTBF越大說明系統(tǒng)采樣失敗的可能越小。從上面公式可以很明顯的看出,對于高速數(shù)字電路,MTBF發(fā)生的概率更大。此外,對于不同的系統(tǒng)和應用場景,MTBF的要求也不同。比如對于一些消費級的產(chǎn)品,比如手機,智能手表等,MTBF的要求要遠遠低于軍工級和航天級別的產(chǎn)品,比如衛(wèi)星,導彈等。

三、怎么降低亞穩(wěn)態(tài)?

首先,亞穩(wěn)態(tài)是不可避免的,是器件的固有屬性。通過適當?shù)姆椒ǎ梢詫喎€(wěn)態(tài)帶來的消極影響將至最低。一般來講,主要有下面幾種方案:

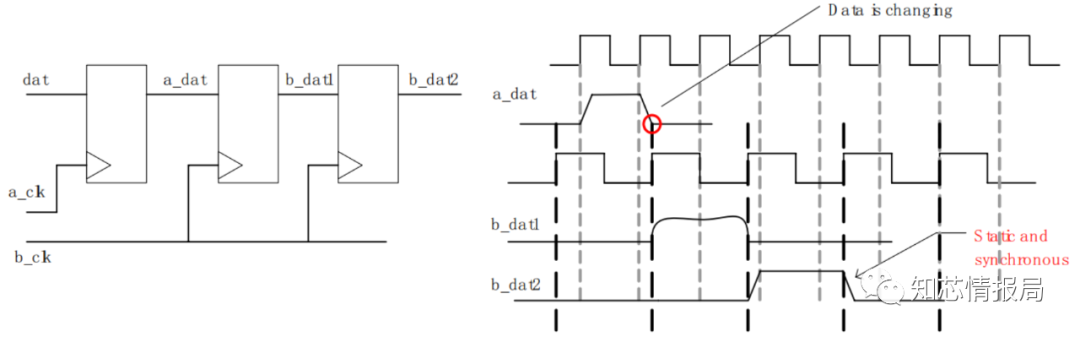

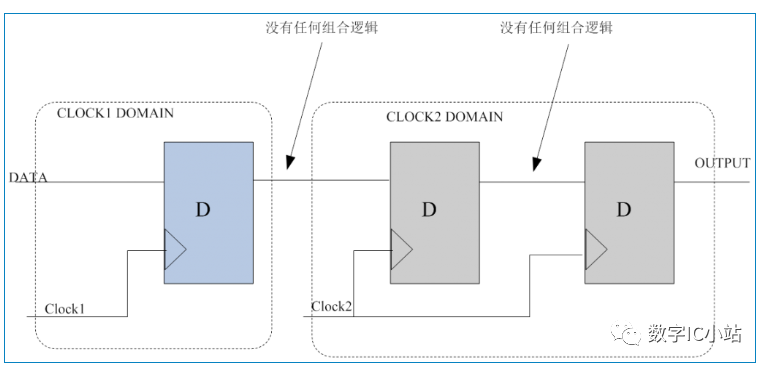

使用兩級寄存器同步

也就是俗稱的“打兩拍”。兩級寄存是一級寄存的平方,兩級并不能完全消除亞穩(wěn)態(tài)危害,但是大大降低了亞穩(wěn)態(tài)的發(fā)生概率。a_dat是時鐘域a_clk的數(shù)據(jù),需要傳輸?shù)綍r鐘域b_clk。假設在b_clk的上升沿正好采到a_dat的跳變沿(從0變1的上升沿,實際上的數(shù)據(jù)跳變不可能是瞬時的,所以有短暫的跳變時間),那么此時a_dat為一個不確定的電平狀態(tài)。所以b_dat1的值也不能確定.但至少可以保證,在b_clk的下一個上升沿,b_dat1基本上已經(jīng)穩(wěn)定,可以滿足下一級觸發(fā)器的setup/hold要求,出現(xiàn)亞穩(wěn)態(tài)的概率得到了很大的改善。

如果再加上第三級寄存器,由于第二級寄存器對于亞穩(wěn)態(tài)的處理已經(jīng)起到了很大的改善作用,第三級寄存器在很大程度上可以說只是對于第二級寄存器的延拍,所以意義是不大的。

異步雙口RAM

在處理多bit數(shù)據(jù)的跨時鐘域時,采用較多的是異步雙口RAM。假設我們現(xiàn)在有一個信號采集平臺,ADC芯片提供源同步時鐘20MHz,ADC芯片輸出的數(shù)據(jù)在20MHz的時鐘上升沿變化,而FPGA內(nèi)部需要使用100MHz的時鐘來處理ADC采集到的數(shù)據(jù)(多bit)。

在這種類似的場景中,我們便可以使用異步雙口RAM來做跨時鐘域處理。先利用ADC芯片提供的20MHz時鐘將ADC輸出的數(shù)據(jù)寫入異步雙口RAM,然后使用100MHz的時鐘從RAM中讀出。在能使用異步雙口RAM來處理跨時鐘域的場景中,也可以使用異步FIFO來達到同樣的目的。

格雷碼

在上面的第二種方案中,master要等RAM中有ADC的數(shù)據(jù)之后才去讀RAM。這就需要100MHz的時鐘對RAM的寫地址進行判斷,當寫地址大于某個值之后再去讀取RAM。程序員們使用直接用100MHz的時鐘于RAM的寫地址進行打兩拍的方式,但RAM的寫地址屬于多bit,如果單純只是打兩拍,那不一定能確保寫地址數(shù)據(jù)的每一個bit在100MHz的時鐘域變化都是同步的,肯定有一個先后順序。如果在低速的環(huán)境中不一定會出錯,在高速的環(huán)境下就不一定能保證了。所以更為妥當?shù)囊环N處理方法就是使用格雷碼轉(zhuǎn)換。

首先什么是格雷碼?在一組數(shù)的編碼中,若任意兩個相鄰的代碼只有一位二進制數(shù)不同,則稱這種編碼為格雷碼(Gray Code),另外由于最大數(shù)與最小數(shù)之間也僅一位數(shù)不同,即“首尾相連”,因此又稱循環(huán)碼或反射碼。在數(shù)字系統(tǒng)中,常要求代碼按一定順序變化。例如,按自然數(shù)遞增計數(shù),若采用8421碼,則數(shù)0111變到1000時四位均要變化,而在實際電路中,4位的變化不可能絕對同時發(fā)生,則計數(shù)中可能出現(xiàn)短暫的其它代碼(1100、1111等)。在特定情況下可能導致電路狀態(tài)錯誤或輸入錯誤。

使用格雷碼可以避免這種錯誤。格雷碼有多種編碼形式。格雷碼(Gray Code)又稱Grey Code、葛萊碼、格萊碼、戈萊碼、循環(huán)碼、反射二進制碼、最小差錯碼等。如下圖所示,若不作特別說明,格雷碼就是指典型格雷碼,它可從自然二進制碼轉(zhuǎn)換而來。二進制格雷碼的生成方法有很多,具體可自行搜索。

| 十進制數(shù)字 | 自然二進制碼 | 典型格雷碼 | 十進制余三格雷碼 | 十進制空六格雷碼 | 步進碼 |

| 0 | 0000 | 0000 | 0010 | 0000 | 00000 |

| 1 | 0001 | 0001 | 0110 | 0001 | 00001 |

| 2 | 0010 | 0011 | 0111 | 0011 | 00011 |

對于格雷碼,相鄰的兩個數(shù)間只有一個bit是不一樣的,如果先將RAM的寫地址轉(zhuǎn)為格雷碼,然后再將寫地址的格雷碼進行打兩拍,之后再在RAM的讀時鐘域?qū)⒏窭状a恢復成10進制。這種處理就相當于對單bit數(shù)據(jù)的跨時鐘域處理了。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5355瀏覽量

120513 -

MTBF

+關注

關注

1文章

30瀏覽量

13583 -

數(shù)字電路

+關注

關注

193文章

1606瀏覽量

80656 -

CDC

+關注

關注

0文章

57瀏覽量

17821 -

觸發(fā)器

+關注

關注

14文章

2000瀏覽量

61185

原文標題:干貨 | 跨時鐘域(CDC)之全面解析

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

多位寬數(shù)據(jù)通過握手方式跨時鐘域

處理跨時鐘域(CDC)信號同步的最常見方法

關于FPGA中跨時鐘域的問題分析

單位寬信號如何跨時鐘域

跨時鐘域電路設計:單位寬信號如何跨時鐘域

如何處理跨時鐘域這些基礎問題

跨時鐘域CDC之全面解析

跨時鐘域CDC之全面解析

評論