一、什么是數字后仿?

這是相對于數字前仿來說的。從概念上來說,數字驗證包含兩方面的內容,數字前仿和數字后仿。前者中timing被默認為理想情況,主要用來驗證數字電路的功能,后者主要用來驗證timing相關。數字后仿做為數字電路設計中重要的一環,用來檢查時序是否滿足,有沒有時序違例的情況發生。數字后仿需要的文件有門級網表和sdf文件。工程師需要將sdf文件進行反標,從而使得仿真工具改變數字電路的默認timing。

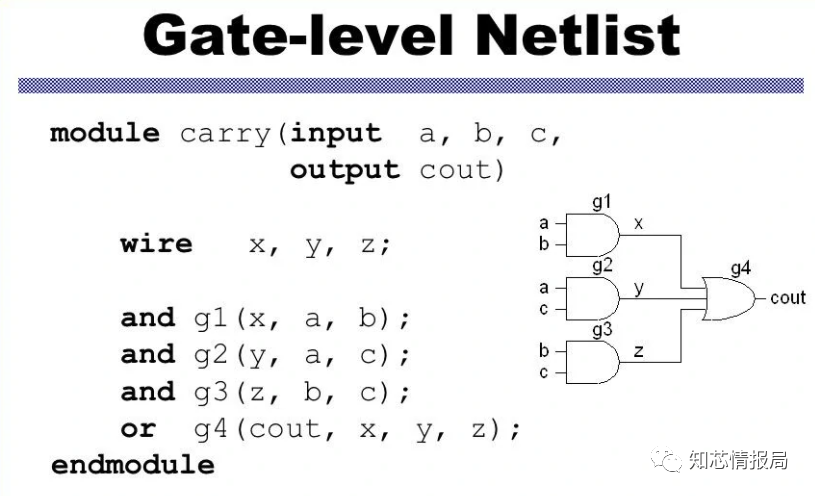

二、什么是門級網表?

數字前端設計的RTL代碼 中的寄存器和組合邏輯,其物理實現還是對應到具體門電路。由于基本的寄存器或組合邏輯,對應的電路結構已經很穩定,電學特性也很明確,故而在綜合級別較高的 EDA 工具中,一般不需要再親自去描述它們的實現方法,而是調用現成的庫信息。EDA 工具會根據 RTL 描述自動編譯出門級的電路描述,這就是門級網表。門級網表分為pr前網表和pr后網表。

PR前網表:又稱為綜合(一般為Design Compiler)后網表,采用的是工藝庫中default的timing,且只有cell的timing信息。此時由于內部的setup和hold沒有修好,會出現不少violation的情形。

PR后網表:相比于pr前網表,pr后網表加上了buf,decap,filler和antenna等器件,timing信息也與pr前網表一致。

三、什么是sdf文件?

SDF文件(standard delay format),直譯過來就是標準延時格式。它描述設計中的timing信息,指明了模塊管腳與管腳之間的delay,時鐘到數據的delay,內部連接delay等。后端布局布線之后由“QRC”出spef,通過PT生成sdf,所以sdf中timing信息都是布局布線之后客觀存在的timing。總而言之,SDF文件是把布局布線過程中的器件延時和線延時信息記錄下來,從而在進行路徑時序分析時可以將整條路徑的時序計算出來,再根據時序約束條件判斷是否滿足時序要求。

設計過程中如果時序不滿足時需要多次迭代的。每次布局布線后都會通過QRC抽取連線寄生參數,配合timing library得到當前的SDF時序反標信息,從而幫助設計人員對時序違背的路徑進行修改。一般來講,在時序收斂前用SDF分析幫助修改設計,時序滿足后,利用SDF進行動態仿真double check下時序滿足情況。

四、如何反標sdf文件?

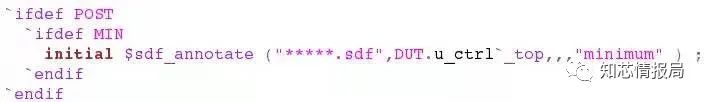

較為常見的方法是在bench中調用系統函數$sdf_annotate來完成。還有其他的方法,比如作為elaboration的選項指定等。$sdf_annotate的標準格式如下:

$sdf_annotate(“sdf_file”[,module_instance][,“sdf_configfile”][,“sdf_logfile”][,“mtm_spec”][,“scale_factors”][,“scale_type”]);

其中:

“sdf_file”:指定SDF文件的路徑。

“module_instance”:指定反標設計的范圍(scope)

“sdf_configfile”:指定SDF配置文件

“sdf_logfile”:指定VCS保存error 和warnings消息的SDF日志文件。也可以使用+sdfverbose runtime option來打印所有反標消息

“mtm_spec”:指定延遲類型"MINIMUM(min)", "TYPICAL(typ)“或者"MAXIMUM(max)”。

“scale_factors”:分別指定minmax的縮放因子,默認是"1.01.0"

“scale_type”:指定縮放之前延遲值的來源。

如下圖舉例:

在反標SDF后,specify塊中定義的延遲不再有用,取代的將是SDF文件中的延遲。So,如何在芯片數字后仿中反標sdf,你了解了嗎?

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5437瀏覽量

124731 -

EDA工具

+關注

關注

4文章

273瀏覽量

32915 -

RTL

+關注

關注

1文章

390瀏覽量

61199 -

數字電路

+關注

關注

193文章

1641瀏覽量

81983 -

門級電路

+關注

關注

0文章

15瀏覽量

2064

原文標題:科普 | 淺談芯片數字后仿的那些事

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

數字后端設計工程師主要干什么?

為什么使用XceliummAIn18進行數字后仿會發生故障?

數字后端設計流程

數字后端關于Litho Grid基本概念介紹詳解

介紹數字后端概念--Shape Blockage

數字后端基本概念介紹

淺談數字后端工程師的工作

基于數字后處理算法的并行交替采樣ADC系統

數字后端基本概念介紹—FinFET Grid

基于超表面天線陣列的射頻前端與數字后端聯合抗干擾方案

評論