2.3接收端均衡器( Rx Equalizer)

2.3.1 線形均衡器(Linear Equalizer)

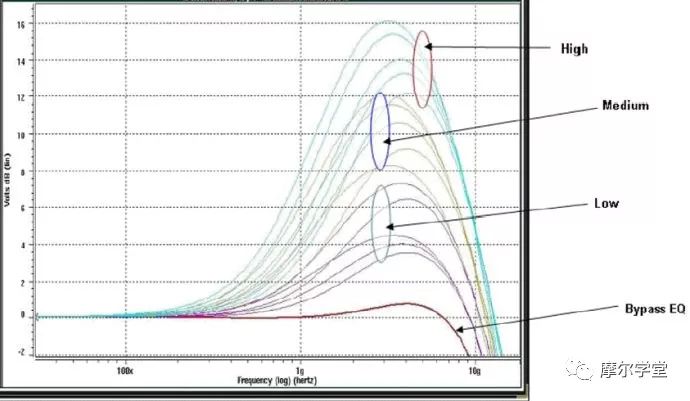

接收端均衡器的目標和發送均衡器是一致的。對于低速(<5Gbps)SerDes,通常采用連續時間域,線性均衡器實現如尖峰放大器(peaking amplifier), 均衡器對高頻分量的增益大于對低頻分量的增益。圖2.8為一個線性均衡器的頻域特性。通常工廠會對均衡特性封裝為數種級別,可以動態設置,以適應不同的信道特性,如High/Med/Low等。

Figure 2.8 Frequency Response of A peaking Amplifier based Rx Equalizer

2.3.2 DFE均衡器(Decision Feedback Equalizer)

對于高速(>5Gbps)SerDes,由于信號的抖動(如ISI相關的確定性抖動)可能會超過或接近一個符號間隔(UI, Unit Interval), 單單使用線性均衡器不再適用。線性均衡器對噪聲和信號一起放大,并沒有改善SNR或者說BER。對于高速SerDes,采用一種稱作DFE (Decision Feedback Equalizer)的非線性均衡器。DFE通過跟蹤過去多個UI的數據(history bits)來預測當前bit的采樣門限。DFE只對信號放大,不對噪聲放大,可以有效改善SNR。

圖2.9演示了一個典型的5階DFE。接收的串行數據由比較器(slicer)來判決0或者1,然后數據流由一個濾波器來預測碼間干擾(ISI),再從輸入的原始信號中減掉碼間干擾(ISI),從而的到一個干凈的信號。為了讓DFE均衡器的電路工作在電路線形范圍內,串行信號先經過VGA自動控制進入DFE的信號幅度。

為了理解DFE的工作原理,先來看一個10Gbps背板的脈沖響應,這個背板模型是matlab給出的一個基于實測的模型,具有典型特性。

圖2.10中,一橫格代表一個UI的時間。可以看出,一個UI( 0.1nS = 1/10GHz )的脈沖信號,通過背板后,泄漏到前后多個相鄰的UI里面,從而對其他UI的數據產生干擾。采樣點后面的干擾叫做post-cursor干擾,采樣點前面的叫做pre-cursor干擾。DFE的第一個系數 h1(此例中0.175)矯正第一個post-cursor, 第二個系數 h2(此例中0.075)矯正第二個post-cursor。DFE的階數越多,能夠校正的post-cursor也越多。

用上述的背板傳輸一個11011的碼流,由于post-cursor和pre-cursor的泄漏,如果沒有均衡,將會導致’0’不能識別,見圖2.11。假定有一個2階的DFE, 那么‘0’bit處的幅度應該減去第一個’1’bit的h2, 第二個’1’bit的h1, 得到0.35-0.075-0.175 =0.1, 足夠被識別為0。

可見,DFE計算歷史bits的post-cursor干擾,在當前bit中把干擾減去,從而得到干凈的信號。由于DFE只能能夠校正post-cursor ISI, 所以DFE前面一般會帶有LE。

只要DFE的系數接近信道(channel)的脈沖相應,就可以到的比較理想的結果。但是信道是一個時變的媒介,比如溫度電壓工藝的慢變化等因素會改變信道channel的特性。因此DFE的系數需要自適應算法,自動撲獲和跟隨信道的變化。

DFE系數自適應算法非常學術,每個廠商的算法都是保密的,不對外公布。對于NRZ碼,典型的算法準則是基于sign-error驅動的算法。Sign-error是均衡后信號的幅度和期望值的誤差,算法以sign-error均方差最小為優化目標,逐次優化h1/h2/h3…。

因為sign-error和采樣位置是耦合在一起相互影響,因此也可以sign-error和眼圖寬度兩個準則為目標進行DFE系數的預測。也因此,采用DFE結構的SerDes通常都會帶有內嵌眼圖測試電路,如圖2.9所示。

眼圖測試電路通過垂直方向上平移信號的幅度,水平方向上平移采樣位置,計算每一個平移位置上的誤碼率BER,從而得到每一個偏移位置與誤碼率關系的”眼圖”,見圖2.12。

Figure 2.12 SerDes Embedded Eye-Diagram Test Function

2.4時鐘數據恢復(CDR)

CDR的目標是找到最佳的采樣時刻,這需要數據有豐富的跳變。CDR有一個指標叫做 最長連0或連1長度 容忍(Max Run Length或者Consecutive Identical Digits)能力。如果數據長時間沒有跳變,CDR就無法得到精確的訓練,CDR采樣時刻就會漂移,可能采到比真實數據更多的1或者0。而且當數據重新恢復跳變的時,有可能出現錯誤的采樣。比如有的CDR采用PLL實現,如果數據長時間停止跳變,PLL的輸出頻率就會漂移。實際上,SerDes上傳輸的數據要么利用加擾,要么利用編碼的方法來保證Max Run Length在一定的范圍內。

l 8B/10B編碼的方法可以保證Max Run Length不超過5個UI。

l 64B/66B編碼的方法可以保證Max Run Length不超過66個UI

l SONET/SDH加擾得方法可以保證Max Run Length不超過80個UI(BER<10^-12)

在點到點的連接中,大部分SerDes協議采用連續模式(continuous-mode),線路上數據流是持續而沒有中斷的。在點到多點的連接中,往往采用突發模式(burst-mode)如PON。很顯然Burst-Mode對SerDes鎖定時間有苛刻的要求。

Continuous-Mode的協議如SONET/SDH則要求容忍較長的連0, 而且對CDR的抖動傳輸性能也有嚴格的要求(因為loop timing)。

如果收(Rx)發(Tx)是異步模式(asynchronous mode),或者頻譜擴展(SSC)應用中,則要求CDR有較寬的相位跟蹤范圍以跟蹤Rx/Tx頻率差。

根據應用場景的不同需求,CDR的實現也有非常多種架構。FPGA SerDes常常采用的基于數字PLL的CDR,和基于相位插值器的CDR。這兩種CDR在環路中采用數字濾波器,相對模擬charge pump加模擬濾波器的結構更節省面積。

圖2.13是基于相位插值器的CDR。鑒相器陣列對輸入的串行數據與M個等相位間隔的時鐘在多個UI的跨度上進行相位比較,得到多個UI跨度上的相位誤差信號。相位誤差信號的頻率很高,寬度也很寬,經過抽取器降速并平滑后,送給數字濾波器。數字濾波器的性能會影響環路的帶寬,穩定性,反應速度等。經數字濾波器平滑后的誤差信號送給相位插值器(phase rotators)修正時鐘相位。最終環路鎖定時,理論上相位誤差為零,90度偏移的時鐘作為恢復時鐘采樣串行輸入。

圖2.14是基于DPLL的CDR, 分為兩個環路,對數據鎖相的環路(phase tracking loop)和圖2.13的CDR工作原理類似。鑒相器陣列對輸入的串行數據與M個等相位間隔的時鐘進行相位比較(也可能是在多個UI的跨度上),得到相位誤差信號。

相位誤差信號送給數字濾波器。數字濾波器的性能會影響環路的帶寬,穩定性,反應速度等。經數字濾波器平滑后的誤差信號送給VCO修正時鐘相位。最終環路鎖定時,理論上相位誤差為零,90度偏移的時鐘作為恢復時鐘采樣串行輸入。

基于DPLL的CDR多了一個頻率跟蹤環路(Frequency Tracking Loop)。這是為了減小CDR的鎖定時間,減少對環路濾波器的設計約束。只有當 頻率跟蹤環路 鎖定后,才會切換到數據相位跟蹤環路。相位跟蹤環路失鎖時,再自動切換到頻率跟蹤環路。

N倍參考時鐘(Reference Clock)頻率 和線路速率接近相等,因此兩個環路的VCO穩態控制電壓是接近相等的。借助 頻率跟蹤環路,減小了 相位跟蹤環路 的捕獲時間。

相位跟蹤環路鎖定時,頻率跟蹤環路不會影響相位環路。因此SerDes接收側對參考時鐘的抖動沒有很高的要求。

基于相位插值器的CDR的參考時鐘可以是收發公用的PLL,也可以是每個通道獨立的PLL。這種結構的參考時鐘抖動會直接影響恢復時鐘的抖動以及接收誤碼率。

鑒相器(PD)

鑒相器用來比較相位誤差,相位誤差以UP或者DN的信號表示, UP/DN持續的時間正比于相位誤差。一個bang-bang結構鑒相器的例子如圖2.15。例子中只用了四個相位的恢復時鐘作為例子。

抽取器和濾波器

抽取器是為了讓濾波器在較低的頻率下工作。抽取的步長,平滑的方法都會影響環路的性能。數字濾波器有比例分支(Proportion)和積分分支(Integral)構成,分別跟蹤相位誤差和頻率誤差。另外數字濾波器的處理延時也不能太大,如果處理延時過大,就會導致環路不能跟蹤相位和頻率的快速變化,導致誤碼。

CDR的結構不限于以上兩種,還有其他很多變種。基本上都是一個鎖相環路。環路的跟隨性能,穩定性(STABILITY),帶寬(bandwidth)/增益(gain)性能分析是一個非常學術的問題,用小信號線形模型分析,有非常多的書籍和資料解釋了環路的量化性能。CDR環路有一些的特點總結如下:

環路帶寬

1.頻率低于環路帶寬的相位抖動會透過CDR轉移到恢復時鐘上。換句話說,頻率低于環路帶寬的抖動可以被CDR跟蹤,不會引起誤碼。高頻的抖動分量根據抖動幅度的大小,可能會引起誤碼。

2.環路帶寬越大,鎖定時間越短,恢復時鐘的抖動也越大。反之則鎖定時間越長,恢復時鐘的抖動也越小。作為CDR,我們希望環路帶寬大一點,這樣可以有更大的抖動容忍能力,但是對于loop timing的應用如SONET/SDH對恢復時鐘的抖動有限制,又不能太大。

- 開關電源的開關頻率一般小于環路帶寬,可以被CDR跟蹤。但是,一方面開關電源耦合到VCO(Digital to Multi-Phase Convertor)上的噪聲不能被環路跟蹤,低成本Ring VCO尤其對電源噪聲敏感。另一方面開關電源的諧波可能超出環路帶寬。

一些協議提供了CDR增益模板,如SDH/SONET。兼容這些協議需要計算輸入和輸出的抖動預算。

2.5 公用鎖相環(PLL)

SerDes需要一個工作在數據波特率上的內部時鐘,或者1/2數據波特率的內部時鐘,工作在DDR模式。片外提供給SerDes的參考時鐘頻率遠遠低于數據波特率,PLL用來倍頻產生內部高頻時鐘。FPGA的SerDes PLL一般有8x,16x,10x,20x,40x模式,以支持常用的SerDes接口協議。比如PCIExpress工作在5Gbps, 在40x模式下需要提供125MHz的片外參考時鐘,20x模式下需要提供250MHz的片外參考時鐘。

一個三階PLL電路如圖2.17,輸入信號的相位和VCO反饋信號的相位由鑒相器比較,相位誤差有charge pump轉化為電壓或電流信號,經過Loop Filter平滑后產生控制電壓,修正VCO的相位,最終使相位誤差趨于零。

Figure 2.17 A 3-order Type II PLL

PLL的工作過程分為入鎖過程和跟蹤過程。在入鎖過程,環路的模型可以用一個非線性微分方程表示,可以評估捕獲時間,捕獲帶寬等指標。入鎖后,在小信號范圍內,PLL的模型是一個常系數線性方程,可以在拉普拉斯變換域研究PLL的帶寬,增益,穩定性等性能, 圖2.18是小信號數學模型。

PLL以傳輸函數極點(分母的根)個數命名環路的階數。VCO對相位有積分作用(Kvco/s),因此不帶濾波器的環路稱為一階環。帶一階濾波器的環路稱為二階環。一階環和二階環是無條件的穩定系統。然而高階環路有更多的極點和零點可以獨立的調整帶款,增益,穩定性,捕獲帶,捕捉時間等性能。

PLL的頻域傳輸函數特性主要有環路濾波器F(s)|s=jw決定, 一個通用的PLL頻域傳輸曲線如圖2.19所示。有兩個重要特征,環路帶款和jitter peaking。過大的peaking會放大jitter, 大的阻尼系數(damping factor)可以限制peaking, 但是會增加環路的如鎖時間, 影響滾降的速度和固有頻率(natural frequency)。

l 當環路鎖定后,固定相位差:

Kdc為環路的直流開環增益,Δω為VCO中心頻率和受控頻率的差。對于charge pump + passive filter結構的PLL相位誤差為零。

l 當環路鎖定后,只有固定相位差,兩個輸入信號頻率相等。

fr/M = fo/N

l 對于輸入端的噪聲,環路是一個低通濾波器,可以抑制高于環路截止頻率的噪聲或干擾。作為SerDes的PLL, 希望帶寬的小一些,以抑制參考時鐘上的干擾和噪聲。

對于VCO噪聲,環路是一個高通濾波器的作用。只有低于環路截止頻率的VCO噪聲得到了抑制。過量的VCO高頻噪聲會惡化時鐘的抖動。低速SerDes(<5Gbps)的VCO出于成本考慮采用Ring結構的VCO,噪聲大且對電源敏感。高速SerDes的VCO采用噪聲小較小的LC結構VCO

發布評論請先 登錄

相關推薦

SerDes的技術原理 SerDes的重要概念和技術概述

請教關于K2 Gigabit Ethernet (GbE) Switch Subsystem的一些問題

SerDes是怎么工作的

Evaluate Serializer-Deserializ

符合EMIEMC標準的SerDes—基本測試策略和指南

An Introduction to Preemphasis and Equalization in Maxim GMSL SerDes Devices

什么是差分信號,差分信號的優缺點分析

深度解讀SerDes(Serializer-Deserializer)1

深度解讀SerDes(Serializer-Deserializer)3

SerDes的基礎知識

SerDes是怎么設計的?(一)

深度解讀SerDes(Serializer-Deserializer)2

深度解讀SerDes(Serializer-Deserializer)2

評論