人們在研發新產品時,往往急于實現產品的功能,于是沿用低頻、低速時的經驗,滿足于利用軟件將單片機、芯片和元器件連接起來,就希望實現產品功能、效能和性能,結果事與愿違,不僅只是在低水平徘徊,而且延誤了寶貴的時間。

其實,隨著集成電路時鐘速率的提高,上升、下降沿速率加快,電源電壓降低以及產品復雜性和密集度的提高、設計周期的不斷縮短,沿用低頻、低速時的經驗已完全不能實現產品的功能、效能和性能。如果在產品設計的后期重新設計,則成本很高。如果延誤日期,損失就更大。

因此,“第一時間推出產品”的設計目標,是生死攸關的競爭需要。要在第一時間實現產品規定功能、使產品效能得以充分發揮,并達到最高性能,就必須做好EMC設計。為了以最低的成本解決EMC問題,就必須在功能設計的同時,進行EMC設計,并選用正確的方法。

現在,產品設計的重點已從功能設計和邏輯設計,轉移到EMC設計上來了。

進行電磁兼容設計的正確方法,應做到:標本兼治,重在治本。就是從治理電磁兼容問題的源頭出發,按重要性為先后,分為若干層次進行設計,并加以綜合分析,進行適當調整,直到完善:

并且在每一層進行接地、屏蔽和濾波的綜合設計和軟件抗騷擾設計。這就稱為“電磁兼容分層與綜合設計法”。可以做到電磁兼容試驗一次成功。

“電磁兼容分層與綜合設計法” 是本文作者在2000年5月“全國電磁兼容標準與質量認證研討會”上,首次提出,至今已十余年。在全國推廣十余年以來, 一批企業先后走出”測試修改法”導致電磁兼容試驗失敗的“怪圈”,做到在產品設計之初,就主動進行電磁兼容設計。而且,電磁兼容設計的投入僅需1% (國內一般為5%至10%)。既降低了成本,又縮短了研發時間。同時,也使“電磁兼容分層與綜合設計法”更加充實與完善,得到了全國許多企業和單位的認可。

第一層 有源器件的選型和印刷電路板設計

在電磁兼容問題的源頭,根本上解決EMC問題,必須首先做好芯片的選型和印刷電路板設計。

一.有源器件的敏感度特性與發射特性

- 電磁敏感度特性

模擬器件帶內敏感度特性取決于靈敏度和帶寬;帶外敏感度特性用帶外抑制特性表示。

邏輯器件帶內敏感度特性取決于噪聲容限或噪聲抗擾度,帶外敏感度特性也是用帶外抑制特性表示。

2.電磁發射特性

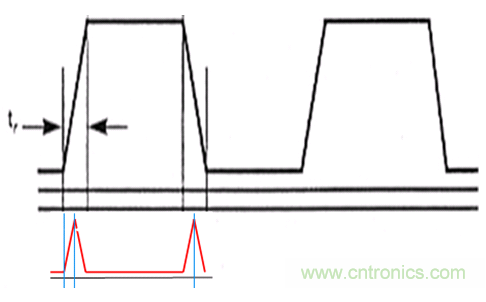

邏輯器件是一種騷擾發射較強的最常見的寬帶騷擾源。時鐘波形的上升時間tr 越短,對應邏輯脈沖所占帶寬越寬

BW=1/ptr

此帶寬也是最高頻率分量。實際輻射頻率范圍可能達到BW的十倍以上。通過器件手冊可以查出tr的典型值。

人們普遍認為:在PCB設計中,需要考慮的關鍵問題是時鐘頻率,其實,時鐘波形的上升時間tr才是最關鍵的因素。上升時間tr定義為從波形的10%處上升到90%處所需要的時間。如果在互連線的一端輸入方波,要求在另一端也得到方波,則該互連線不僅必須能傳輸方波的基波,還必須能傳輸全部高次諧波,至少為15次諧波。這就是說,PCB的時鐘頻率并不重要,上升時間tr和需要重新產生的諧波才是最重要的。描述這個要求的詞語就是帶寬BW,也即最高頻率分量。

- △I 噪聲電流、瞬態負載電流IL的產生和危害

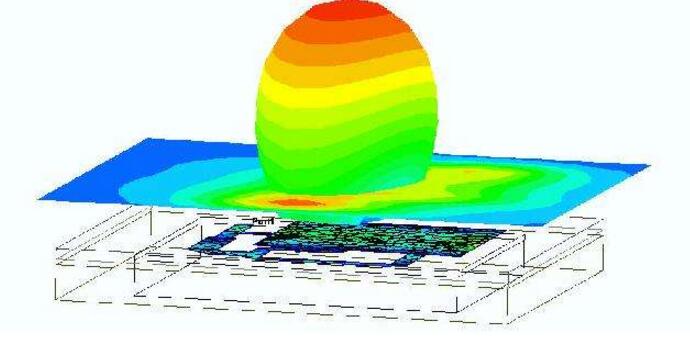

當數字集成電路在加電工作時,它內部的門電路將會發生 “0”和“1”的變換,即開關狀態。在變換的過程中,該門電路中的晶體管將發生導通和截止狀態的轉換,會有瞬間變化電流-浪涌電流di/dt從所接電源流入門電路,或從門電路流入地線,這個變化電流就是△I噪聲的初始源,稱△I噪聲電流。如圖1所示。

圖1 △I噪聲電流

設驅動線對地電容與驅動門輸入電容之和為負載電容 Cs,平時被充電,其值為電源電壓。驅動門由高電位翻轉為低電位時Cs放電,放電電流稱為瞬態負載電流:

IL = Cs×dv/dt

瞬態負載電流IL與△I噪聲電流復合后,會產生更強的電磁騷擾發射。是阻礙實現產品規定功能、使產品效能得不到充分發揮的主要原因。由于PCB上,信號線、電源線和地線等都存在一定的引線電感L,瞬態負載電流IL與△I噪聲電流復合后產生的瞬間變化電流di/dt,將通過引線電感L的感抗引起尖峰電壓

V= - Ldi/dt

即△I噪聲電壓,稱為同步開關噪聲(Simultaneous Switch Noise SSN),如圖2所示,會引發地電位和電源電壓的波動(Ground/Power Bounce),產生電磁騷擾發射。所以,引線電感L是產生傳導騷擾和輻射騷擾的根源之一。

圖2 尖峰電壓

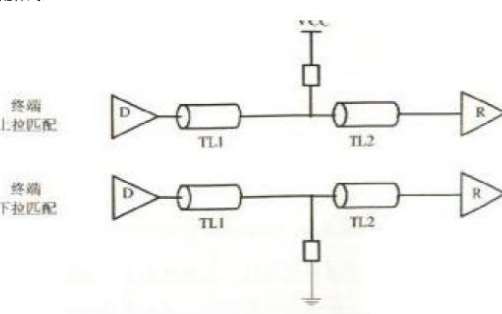

電磁騷擾發射的另一根源為等效電壓源的源阻抗,也即電源分配系統輸入阻抗Z,系統要求尖峰電壓應在正常電源電壓的±2.5%至±5%以內。等效于源阻抗Z要足夠低

V= Z×ΔI

不論ΔI如何變化,都可保持V變化很小。這可通過安裝去耦電容達到。

理想電源的源阻抗Z為零,電源平面上任何一點電位保持恒定。

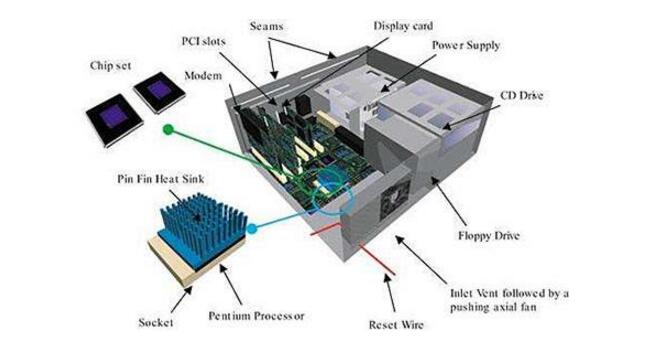

4.掌握IC設計和封裝特性抑制EMI

IC封裝也是產生電磁騷擾的原因之一。IC封裝包括芯片,內部PCB以及焊盤。直接影響IC封裝的電容和電感。

芯片是作為系統的一部分而存在的,硅芯片必須采用某種封裝,然后焊接到PCB板上。這一互連鏈,即芯片通過封裝連接到PCB板上,本身就是一個復雜系統。

應將芯片設計、封裝和印刷電路板作為一個系統來考慮。以保證最后組裝和加電后能得到所期望的結果。最好的方法是,對所有這些進行并行設計、分析和驗證。

封裝是指安裝半導體集成電路芯片用的外殼,它不僅起著安放,固定,密封,保護芯片和增強電熱性能的作用,而且還是溝通芯片內部世界與外部電路的橋梁--芯片上的接點用導線連接到封裝外殼的引腳上,這些引腳又通過印制板上的導線與其它器件建立連接。衡量一個芯片封裝技術先進與否的重要指標是芯片面積與封裝面積之比,這個比值越接近1越好,引線電感越小。封裝技術已經歷了好幾代的變遷:

1)通孔插入式封裝(Through-hole Package)

DIP(Dual In-line Package) 雙列直插式封裝:上世紀 70年代的封裝,最大引腳數64條。其芯片面積/封裝面積為1:8.6,離1相差很遠,說明封裝效率很低,引線很長,引線電感很大;

PGA(Pin Grid Array)針柵陣列式封裝,引腳中心距為2.54mm,引腳數為64-447。表面安裝式PGA引腳中心距為1.27mm,引腳數為250-528,引線電感很大;

2)表面安裝式封裝(Surface Mounted Package )

上世紀80年代出現了芯片載體封裝,有陶瓷無引線芯片載體封裝LCCC,塑料有引線芯片載體封裝PLCC,小尺寸封裝SOP(Small Outline Package),塑料四邊引出扁平封裝PQFP。芯片面積/封裝面積為1:7.8,引線電感仍很大;

3)BGA封裝與CSP封裝

上世紀90年代隨著集成技術的進步和深亞微米技術的使用,LSI,VLSI,ULSI相繼出現,芯片集成度不斷提高,對封裝要求更加嚴格,I/O引腳數急劇增加,功耗也隨之增大。為滿足發展的需要,在原有封裝品種基礎上,又增添了新的品種--球柵陣列封裝簡稱BGA(Ball Grid Array Package)。成為CPU南北橋等VLSI芯片的高密度,高性能,多功能及高I/O引腳封裝的最佳選擇。芯片面積/封裝面積為1:4,引線電感有所減小;1994年9月誕生了一種新的封裝形式命名為芯片尺封裝,CSP(Chip Size Package或ChipScale Package),芯片面積/封裝面積為1:1.1。也就是說,單個芯片有多大,封裝尺寸就有多大,引線電感大大減小;

4)裸芯片組裝

隨著組裝密度和IC的集成度的不斷提高,為適應這種趨勢,IC的裸芯片組裝形式應運而生,并得到廣泛應用。它是從已完工的晶圓(Water)上切下的芯片,不按傳統之 IC 先行封裝成體,而將芯片直接組裝在電路板上,謂之 Bare Chip Assembly。早期的 COB (Chip on Board)做法就是裸芯片的具體使用,不過 COB 是將芯片的背面黏貼在板子上,再行引線及膠封。而新一代的 Bare Chip 卻連引線也省掉,是以芯片正面的各電極點,直接反扣熔焊在板面各配合點上( Flip Chip)。或以芯片的凸塊扣接在載帶自動鍵合(TAB)的內腳上,再以其外腳連接在 PCB 上。此二種新式組裝法皆稱為 裸芯片組裝,寄生 C,L小。并且可節省整體成本約 30% 左右;

5)載帶自動鍵合(TAB):多接腳大型芯片組裝:裸芯片貼裝技術之一

載帶基材為聚酰亞胺薄膜,表面覆蓋上銅箔后,用化學法腐蝕出精細的引線圖形。芯片在引出點上鍍Au、Cu或Sn/Pn合金,形成高度為20-30mm的凸點電極。組裝方法是將芯片粘貼在載帶上,將凸點電極與載帶的引線連接,然后用樹脂封裝。它適用于大批量自動化生產。TAB的引線間距可較QFP進一步縮小至0.2mm或更短。

6)系統芯片(SoC)

SoC就是將系統的全部功能模塊集成到單一半導體芯片上。將一片SoC與現在的板卡相比,其中可能含有的功能模塊有:CPU、RAM、ROM、DSP、無線模塊、模擬和數字模塊、網絡模塊、硬核等。

嵌入式片上系統將整個嵌入式系統集成到一塊芯片中,應用系統的電路板變得簡潔,減小體積和功耗,提高了可靠性。而且,通過改變內部工作電壓,降低芯片功耗;減少芯片對外引腳數,簡化制造過程;減少外圍驅動接口單元與電路板之間的信號傳遞,加快數據處理速度;內嵌線路可避免外部電路板在信號傳遞時所造成的騷擾。

單芯片嵌入式微控制器(MicroController Unit,MCU)俗稱單片機,將整個嵌入式微計算機系統集成到一塊芯片中,從而使功耗和成本下降,可靠性提高。

IC產業技術發展經歷了電路集成、功能集成、技術集成,直到今天基于計算機軟硬件的知識集成,其目標就是將電子產品系統電路不斷集成到芯片中去,力圖吞噬整個產品系統。單芯片的嵌入式系統的出現,以單個芯片實現的產品系統不僅僅限于硬件系統,而是一個帶有柔性性能的軟、硬件集合體的電子系統。SoC是微電子領域IC設計的最終目標。

-

電源

+關注

關注

184文章

17779瀏覽量

250861 -

集成電路

+關注

關注

5389文章

11576瀏覽量

362387 -

emi

+關注

關注

53文章

3595瀏覽量

127860 -

時鐘

+關注

關注

11文章

1736瀏覽量

131597

發布評論請先 登錄

相關推薦

電磁兼容的設計方法

電磁兼容的概念及設計方法

開關電源電磁兼容技術的現狀與解決方法

一文看懂電磁兼容性原理與方法及設計

電磁兼容的重要性_電磁兼容技術應用

電磁兼容設計的常用方法解析

簡述電磁兼容設計的常用方法1

簡述電磁兼容設計的常用方法1

評論