看razavi射頻微電子中,LNA設計的一章,發現上面計算架構的噪聲系數時,基本的步驟是,先算出每個器件在輸出端的噪聲貢獻,然后再將其疊加。

要做到這一步,即可以分析器件的噪聲性能,可以通過電壓源和電流源等熟悉的元件對器件的噪聲進行建模。

電阻的熱噪聲

環境熱能導致電阻中的電荷載流子隨機運動,從而產生噪聲。

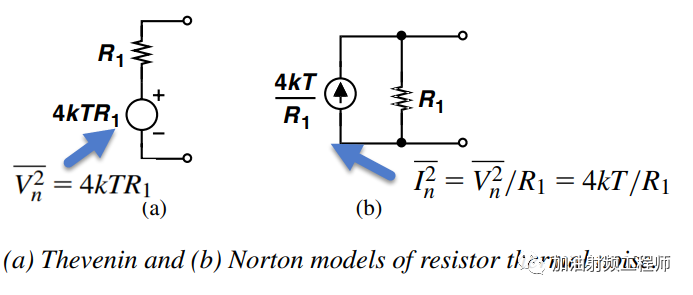

這個噪聲可以通過一個級聯電壓源,或者并聯的電流源來模擬。電壓源和電流源的功率譜密度(PSD,power spectral density), 如下圖所示。模型有時候可以簡化分析,電壓源和電流源的極性并不重要,但是在給定電路的計算中,需要保持一致。

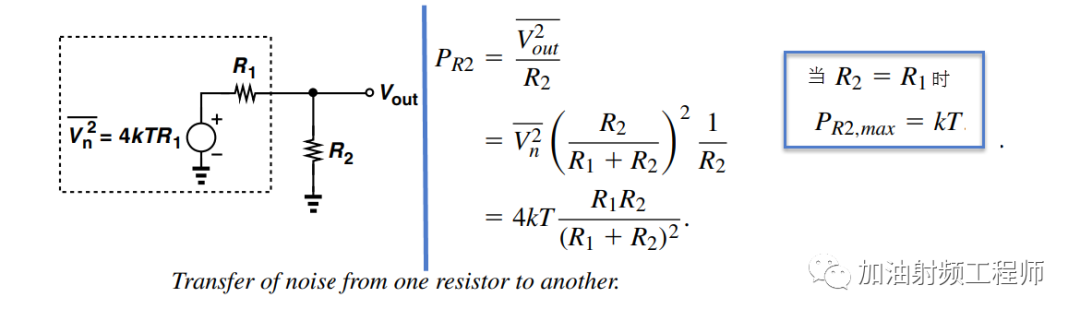

那么,如果電阻將環境熱量轉換為噪聲電壓或電流,我們能否從電阻中提取能量呢?

有趣的是,如果R1和R2處于同樣的環境溫度,它們之間沒有凈流量傳遞,因為R2同樣會產生同樣的噪聲電壓。但是,如果R2的環境溫度T=0K ,那么R1會持續地從它的環境中吸收能量,把它轉換為噪聲,然后把能量傳輸給R2.

傳遞給R2的平均能量為:

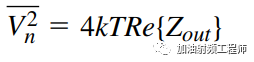

對于一個熱噪聲噪聲密度為4KTR1的電路來說,它不需要一定要包含電阻R1.

如果無源電路耗散能量,那么它一定包含一個物理電阻,因此一定會產生熱噪聲。我們可以籠統的說,有耗電路就有噪聲。

比如:如果一個無源(互易)網絡的兩個端口之間的阻抗的實部等于Re{Zout}, 如下圖所示,那么這兩個端口間熱噪聲的PSD為:

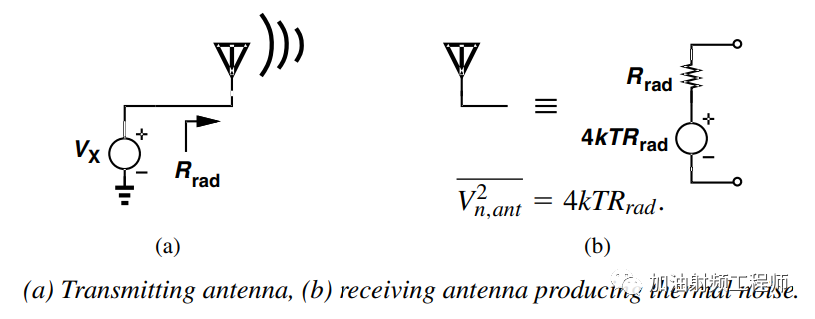

這個理論,并不局限于集總電路。

比如說,一個天線,如果作為發射天線,則其向外輻射能量,其中Rrad稱為輻射電阻,作為接收天線,天線會產生熱噪聲,如下圖所示。

嚴格來說,這是不正確的,因為接收天線的噪聲實際上是由“背景”噪聲(例如宇宙輻射)給出的。然而,在 RF 設計中,通常假設天線噪聲為 4kTRrad。

MOSFET中的噪聲

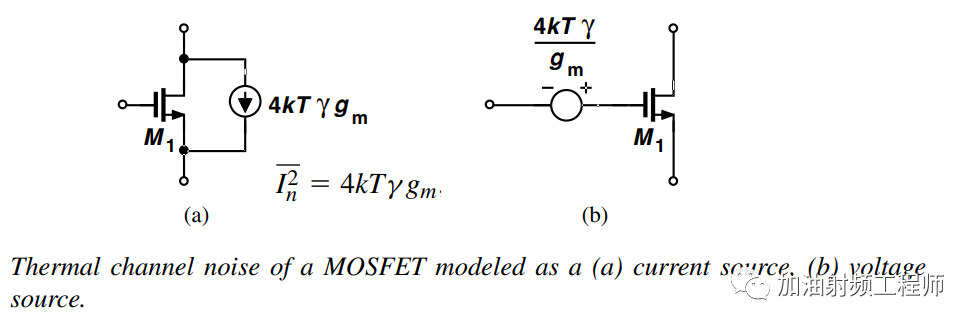

工作在飽和區的MOS晶體管的熱噪聲,可以近似地用源極和漏極之間的電流源表示。如下圖所示。

其中, γ為過量噪聲系數,"excess noise coefficient",gm為跨導(transconductance).

對于長溝道晶體管,γ的值為2/3;對于短溝道晶體管,γ的值為2.

γ的實際值,還取決于其他因素,通常通過對每一代 CMOS 技術的測量獲得。

噪聲也可以用電壓源與MOS管的柵極級聯來模擬,如上圖所示。

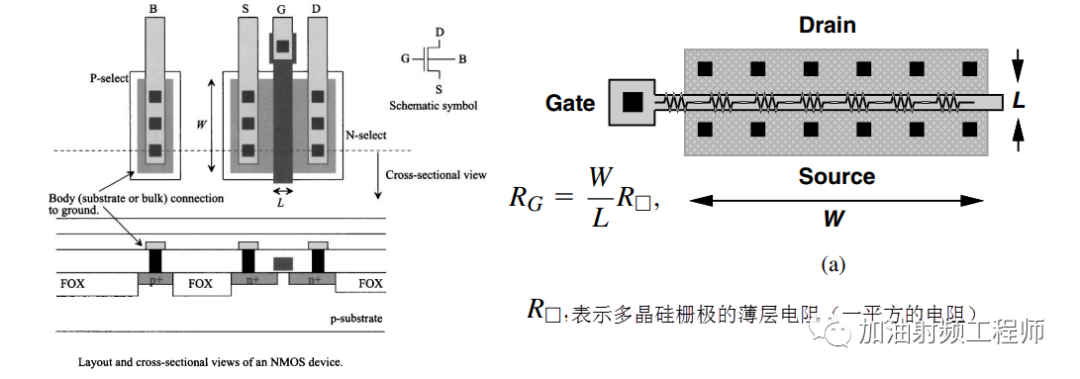

熱噪聲的另一個組成部分,是來自MOS管的柵極電阻,而且當柵極長度縮小時,這個效應會變得更加重要。

如下圖所示,MOS管的寬度為W,長度為L。

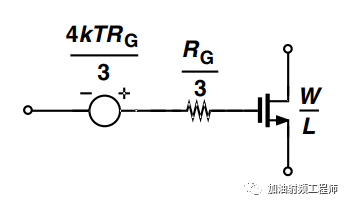

可以證明,這個結構,可以簡化成一個集總模型,其等效柵極電阻為RG/3,熱噪聲PSD為4KTRG/3.

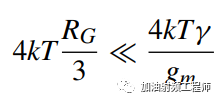

在一個好的設計中,這個噪聲必須小于溝道的噪聲,即

柵極和漏極之間也存在電阻,但是這可以通過使用multiple fingers來減小。

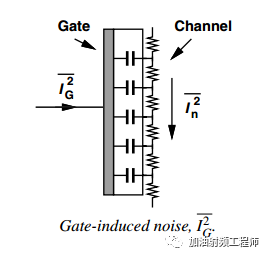

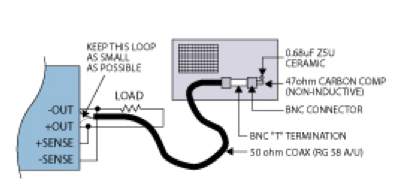

高頻的時候,從溝道流過的熱噪聲電流會通過電容耦合耦合到柵極,因此產生柵極感應噪聲電流“gate-induced noise current”。如下圖所示。該效應,并未在典型的電路放置器中建模,但其重要性仍然不清楚。

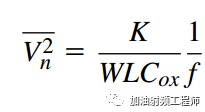

MOS管也有閃爍噪聲,又稱為"1/f"噪聲。

可以用與柵極級聯的電壓源來模擬,這種噪聲的功率譜密度為:

其中,K是一個與工藝相關的恒量。在大多數的CMOS工藝中,PMOS 器件的 K 低于 NMOS 晶體管,因為前者攜帶電荷遠低于氧化硅界面,因此受“表面狀態”(懸空鍵)的影響較小。

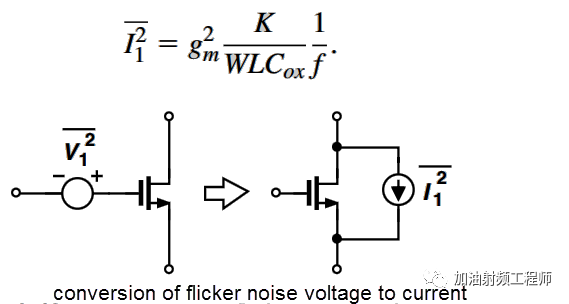

同樣的,閃爍噪聲也可以通過一個電流源來模擬。

如下圖所示,與MOS管柵極相連的電壓源,可以等效為連接在漏極和源極之間的電流源,其值為gmV1。

所以,可以得到下圖。

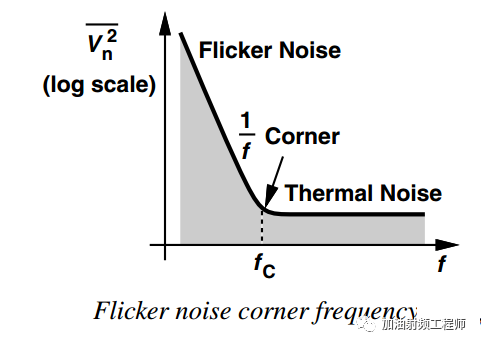

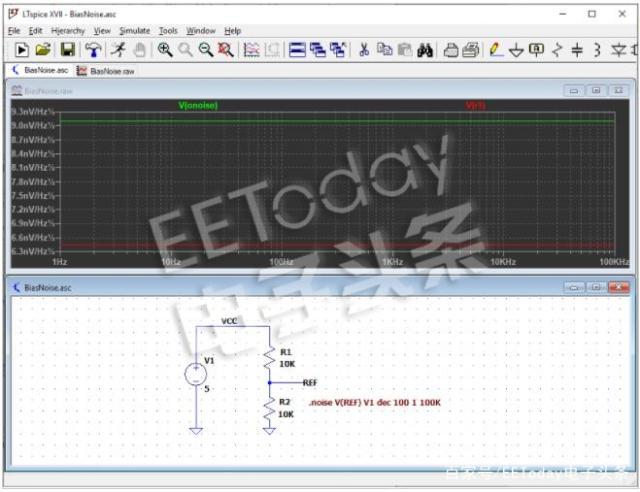

給定器件尺寸和偏置電流,1/f噪聲的功率譜密度和熱噪聲的功率譜密度,在某個頻率點相交,稱為“1/f 噪聲轉角頻率”,如下圖所示。

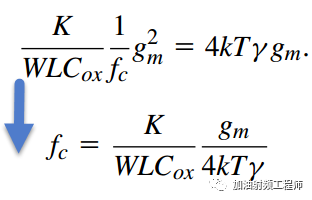

將熱噪聲電流等于閃爍噪聲電流,求得的f即為1/f噪聲拐角頻率,如下式所示。

在現代CMOS工藝中,拐角頻率處于幾十甚至幾百MHz的范圍內。

雖然閃爍噪聲的影響在高頻下似乎可以忽略不計,但我們必須注意,混頻器和振蕩器等電路中的非線性或時間變化,可能會將1/f閃爍噪聲轉換到射頻領域。

審核編輯:劉清

-

電壓源

+關注

關注

1文章

410瀏覽量

32832 -

MOS晶體管

+關注

關注

0文章

18瀏覽量

7691 -

電流源

+關注

關注

4文章

384瀏覽量

29314 -

PSD

+關注

關注

0文章

35瀏覽量

45424

原文標題:噪聲那些事

文章出處:【微信號:加油射頻工程師,微信公眾號:加油射頻工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

對輸出端的噪聲進行建模

對輸出端的噪聲進行建模

評論