在要求采樣率低于 10 MSPS 的應用中,最常見的模數轉換器之一是SAR ADC。該 ADC 非常適合需要 8-16 位分辨率的應用。SAR ADC 是最容易理解的模數轉換器之一,一旦我們知道這種類型的 ADC 的工作原理,它的優缺點就很明顯了。

SAR ADC 的基本操作

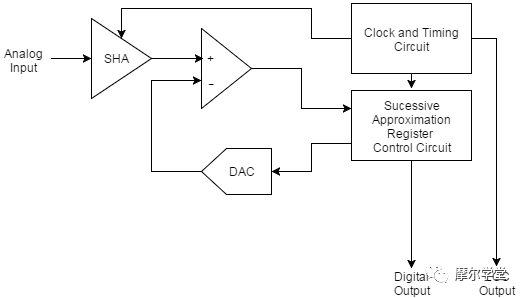

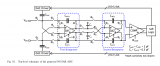

基本逐次逼近寄存器模數轉換器如下圖所示:

SAR ADC 為每個樣本執行以下操作:

- 模擬信號被采樣并保持。

- 對于每一位,SAR 邏輯向 DAC 輸出一個二進制代碼,該代碼取決于正在審查的當前位和已經近似的先前位。比較器用于確定當前位的狀態。

- 逼近所有位后,將在轉換結束 (EOC) 時輸出數字逼近。

SAR 操作最好解釋為二分搜索算法。考慮下面顯示的代碼。在此代碼中,正在審查的當前位設置為 1。由此產生的二進制代碼輸出到 DAC。這與模擬輸入進行比較。如果從模擬輸入中減去 DAC 輸出的結果小于 0,則審查位設置為 0。

%8?bit digital output is all zeros

digital output = zeros(1,8);

%Normalised to one for example

reference voltage = 1;

for i=1:8

%current output bit set to 1:

digital output(i)=1;

compare threshold = 0;

%Output digital output in current form to DAC:

for j=1:i

compare threshold = compare threshold+digital output(j)*reference voltage/(2?j);

end

%Comparator compares analog input to DAC output:

if (input voltage?compare threshold<0)

digital output(i)= 0;

end

end

如果我們考慮 0.425 V 的模擬輸入值和 1 V 的參考電壓的示例,我們可以將 8 位 ADC 的輸出近似如下:

- 將 8 位輸出的第一位設置為 1,因此輸出到 DAC 為 0.5

- 0.425 減去 0.5 小于 0,所以將輸出的第一位設置為 0

- 將 8 位輸出的第二位設置為 1,因此輸出到 DAC 為 0.25

- 0.425 減去 0.25 大于 0,所以輸出的第二位是 1

- 將 8 位輸出的第三位設置為 1,因此輸出到 DAC 為 0.375

- 0.425 減去 0.375 大于 0,所以輸出的第三位是 1

對所有 8 位重復此過程,直到確定輸出為:

01101100

從這個過程中可以明顯看出,N 位 SAR ADC 必須需要 N 個時鐘周期才能成功逼近輸出。因此,盡管這些 ADC 功耗低且需要的空間很小,但它們不適合高速、高分辨率應用。由于這些 ADC 需要的空間非常小,因此它們通常被用作微控制器內部的外設或采用極小的封裝。

功耗與采樣率成比例的事實可能不太直觀。因此,這些 ADC 非常適用于需要 ADC 不經常進行采樣的低功耗應用。

在此架構中需要注意的一件事是缺少管道以及與此相關的延遲。因此,SAR ADC 適用于多路復用應用。

定義 ADC 整體特性的 ADC 的兩個特性并不奇怪,DAC 和比較器。

電容式 DAC

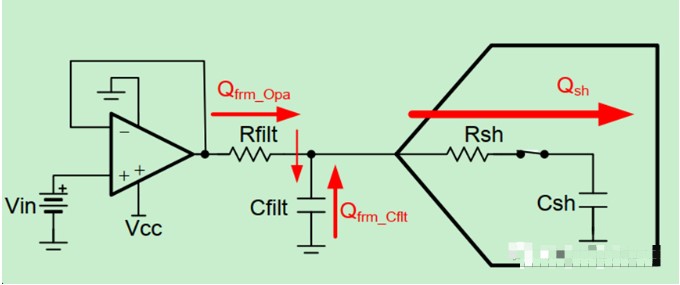

電容式 DAC 包含 N 個電容器,用于 N 位分辨率,并添加了第二個最低有效位電容器。電容式 DAC 的示例如下所示:

在采集過程中,公共端通過關閉 S11 接地,模擬輸入 (Ain) 對電容器進行充電和放電。如果通過打開 S1 斷開輸入,則會出現保持模式。然后打開 S11,將公共端驅動到-Ain。如果 S2 然后連接到 Vref,則等于 Vref/2 的電壓被添加到 -Ain。在此之后確定關于最高有效位的決定。

容性 DAC 的最大穩定時間由最高有效位的穩定時間決定。這是因為 DAC 輸出的最大變化發生在這個最高有效位上。

您可能會認為 16 位 SAR ADC 產生輸出所需的時間是 8 位 SAR ADC 的兩倍,因為輸出位是其兩倍。實際上,16 位 SAR ADC 中內部 DAC 的建立時間比 8 位版本的建立時間要長得多。因此,與低分辨率版本相比,高分辨率 SAR ADC 的采樣率顯著降低。

整個 ADC 的線性度取決于內部 DAC 的線性度。因此,ADC 分辨率受到內部 DAC 分辨率的限制也就不足為奇了。

jpg)

比較器

比較器需要既準確又快速。與 DAC 一樣,比較器必須具有至少與 SAR ADC 一樣好的分辨率也就不足為奇了。與比較器相關的噪聲必須小于 SAR ADC 的最低有效位。

總結

SAR ADC 的優勢

- 低功耗

- 體型小

SAR ADC 的弱點

- 高分辨率的低采樣率

- 由于 DAC 和比較器的限制,分辨率有限

- 大小隨位數增加

SAR ADC 的應用

非常適合采樣頻率低于 10 MHz 且分辨率在 8-16 位之間的多通道數據采集系統。

-

SAR

+關注

關注

3文章

426瀏覽量

46899 -

MSPS

+關注

關注

0文章

417瀏覽量

28399 -

adc

+關注

關注

99文章

6688瀏覽量

549041 -

數據采集

+關注

關注

40文章

7150瀏覽量

116378 -

模數轉換器

+關注

關注

26文章

3342瀏覽量

128220

發布評論請先 登錄

SAR ADC的工作原理是什么?SAR ADC的優點和缺點有哪些?

SAR與ADC不同輸入類型

這個SAR ADC怎么樣?

序列 SAR ADC 使您能夠在 PSoC 4 上配置和使用不同操作模式的 SAR ADC

SAR ADC的原理以及SAR ADC驅動電路設計要點

SAR ADC的隔離

評論