由于PFC的控制地和MOS管組成的雙向開關(guān)的源極不共地,因此需要解決開關(guān)管浮地驅(qū)動(dòng)問題。

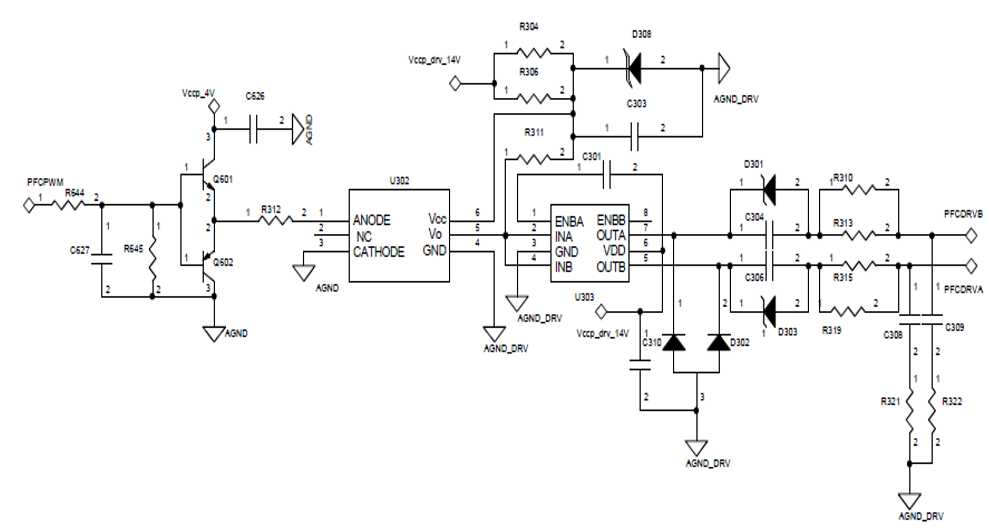

圖2 驅(qū)動(dòng)電路圖

電路圖說明:

2. VCC_4V和AGND是DSP側(cè)的電源和控制地;Vccp_14V和AGND_DRV是MOS管驅(qū)動(dòng)的電源和控制地;

3. PFCDRVA和PFCDRVB分別是2個(gè)開關(guān)管的柵極驅(qū)動(dòng)信號(hào);

4. U302為隔離光藕,U303是集成驅(qū)動(dòng)芯片。

1.1驅(qū)動(dòng)電路基本工作原理

其工作原理大致如下:DSP發(fā)出PWM驅(qū)動(dòng)控制信號(hào);驅(qū)動(dòng)信號(hào)通過后級(jí)推挽等放大電路驅(qū)動(dòng)隔離光藕實(shí)現(xiàn)驅(qū)動(dòng)信號(hào)的隔離傳輸功能(隔離光耦將弱信號(hào)的控制地和強(qiáng)抖動(dòng)電平的驅(qū)動(dòng)地隔離,同時(shí)也利用光傳輸對(duì)前級(jí)驅(qū)動(dòng)的電噪聲進(jìn)行屏蔽和抑制)。由于隔離光耦的輸出電流有一定限制,無法直接驅(qū)動(dòng)MOS管,故需通過驅(qū)動(dòng)芯片將其輸出電平信號(hào)進(jìn)行整形和電平轉(zhuǎn)化,最后驅(qū)動(dòng)MOS管。

1.2隔離光藕和驅(qū)動(dòng)芯片的選擇

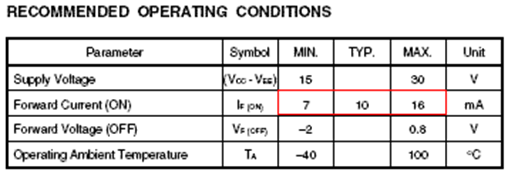

隔離光耦是整個(gè)驅(qū)動(dòng)電路的關(guān)鍵器件,其選型需綜合考慮最大工作隔離電壓、開關(guān)速度、CMTI、傳輸延遲、最大開關(guān)頻率、成本等指標(biāo)。另外關(guān)于隔離光藕的帶寬指標(biāo)如何選擇,其對(duì)于相位裕量的影響有多大,目前還不是十分清楚,還有待后續(xù)進(jìn)一步研究。

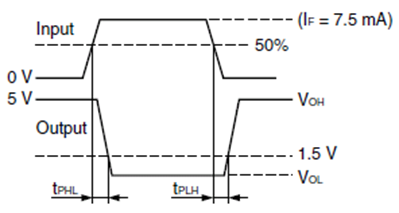

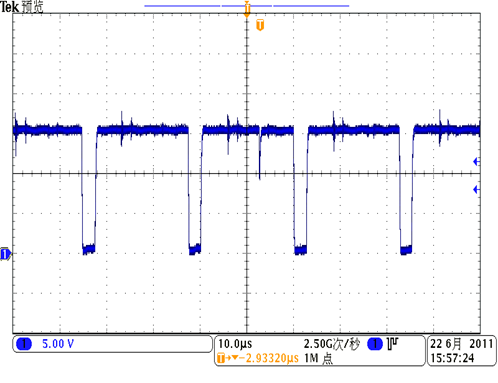

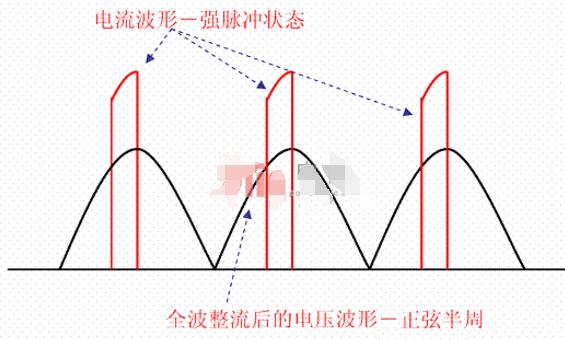

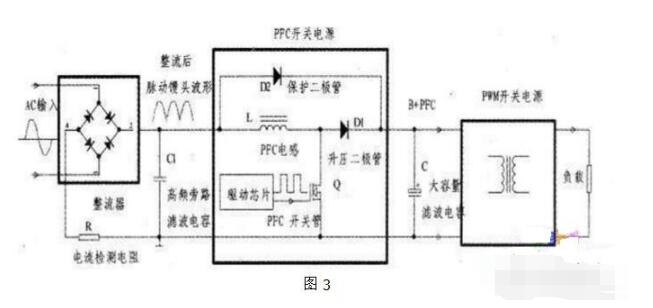

同時(shí),驅(qū)動(dòng)芯片邏輯的選擇也直接取決于電路光藕的選擇。以圖2中的電路為例,由于H7413Z PFC的開關(guān)頻率為70KHz,故需選用高速光藕。圖2中所選用的邏輯光藕U302的輸入輸出信號(hào)為反邏輯,其輸入輸出波形示意如圖3所示(以PS9317為例)。后級(jí)的驅(qū)動(dòng)芯片U303也需選用反邏輯的芯片與之匹配,其輸入輸出邏輯如圖3所示(以UCC27423為例)。

圖3 PS9317輸入輸出波形

1.3 PWM信號(hào)的放大和電平轉(zhuǎn)換

由于DSP的PWM信號(hào)幅值和輸出電流均有限,無法直接驅(qū)動(dòng)隔離光耦的原邊LED,因此需使用電平轉(zhuǎn)換和放大電路,提升驅(qū)動(dòng)能力。并且還需根據(jù)所用隔離光耦的VF特性差異,設(shè)計(jì)不同的前級(jí)電路:

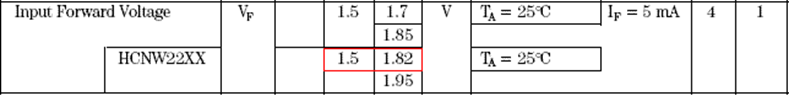

(1) 對(duì)于邏輯門光耦,其LED的VF離散性較小(例如HCNW2211為0.32V,見圖5).

圖5 HCNW2211的VF分布范圍

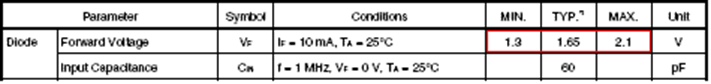

(2) 對(duì)于柵極驅(qū)動(dòng)光耦,由于部分廠家LED的VF離散性較大(例如Renesas PS9552L3為0.45 V,見圖7),如果直接用圖6的推挽放大,當(dāng)VF分別取到上下限時(shí),I-F很難設(shè)計(jì)在7-16mA之間(圖8)。H941AZ設(shè)計(jì)之初為解決HCNW2211的獨(dú)家問題,擬采用驅(qū)動(dòng)光耦(39100114),同時(shí)為滿足I-F的要求,因此設(shè)計(jì)反邏輯+推挽輸出做為前級(jí)電路。

圖7 PS9552L3的VF分布范圍

圖8 PS9552L3和FOD3120的IF推薦范圍

隨著光耦技術(shù)的發(fā)展,業(yè)內(nèi)還出現(xiàn)一種IPM接口驅(qū)動(dòng)光耦,如39100151(ACPL-P480和TLP715)。它們具有更小的封裝(如Stretched SO-6),價(jià)格也合理,而VF離散性較小(約0.2V)。

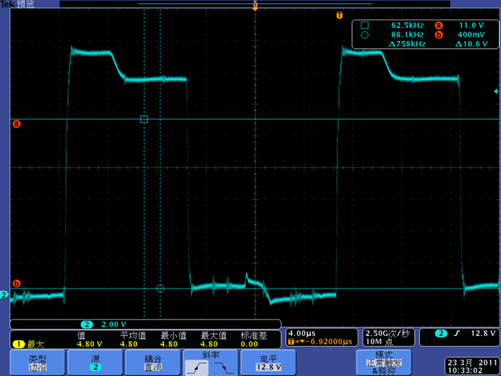

1.4光耦輸出整形和放大

通常,隔離光耦的輸出電流有一定限制。例如邏輯門光耦HCNW2211的IO小于25mA,即便是柵極驅(qū)動(dòng)光耦FOD3120,其最大輸出電流也只有2.5A,無法同時(shí)驅(qū)動(dòng)2個(gè)SPW47N60C3。因此,光耦輸出還需要再加一級(jí)放大電路。在調(diào)試過程中發(fā)現(xiàn),采用三極管推挽放大,由于強(qiáng)共模干擾的存在,會(huì)引起驅(qū)動(dòng)Vgs的高、低電平并不是平直波形,特別是低電平存在雜亂的波動(dòng)(圖9)。如果波動(dòng)超過開關(guān)管的Vgs(th),可能造成誤開通。若改用共地驅(qū)動(dòng)芯片,一方面對(duì)光耦的輸出進(jìn)行整形,提高柵極驅(qū)動(dòng)Vgs電平的平整度(圖10);另一方面利用驅(qū)動(dòng)芯片輸入級(jí)邏輯電平的滯環(huán),進(jìn)一步增強(qiáng)對(duì)光耦輸出干擾信號(hào)的抑制能力。此外,驅(qū)動(dòng)芯片一般采用FET圖騰柱輸出,其開關(guān)速度較推挽三極管更快,有利于減小開關(guān)損耗。

圖9 采用推挽三極管輸出的Vgs

圖10 采用驅(qū)動(dòng)芯片輸出的Vgs

1.5其他附屬電路的工作原理

在圖2中,由于隔離光藕U302與驅(qū)動(dòng)芯片U303對(duì)供電電源的要求不同,為簡(jiǎn)化設(shè)計(jì),我們通過穩(wěn)壓管D308將14V轉(zhuǎn)化為5.1V給隔離光藕U301供電。D302是驅(qū)動(dòng)芯片的負(fù)壓鉗位二極管;在驅(qū)動(dòng)回路,利用穩(wěn)壓管和電容并聯(lián)(如D301,C304)形成負(fù)壓,提高驅(qū)動(dòng)脈沖零電平的抗干擾能力;C301是H7413Z中為防止驅(qū)動(dòng)芯片ENB腳受到干擾導(dǎo)致誤關(guān)斷而增加的,可以根據(jù)實(shí)際調(diào)試情況是否去除。另一種方法可以是,在ENB腳與VDD之間外加大于10Kohm的上拉電阻。

-

MOS管

+關(guān)注

關(guān)注

108文章

2411瀏覽量

66762 -

PWM

+關(guān)注

關(guān)注

114文章

5181瀏覽量

213810 -

PFC

+關(guān)注

關(guān)注

47文章

969瀏覽量

106037 -

驅(qū)動(dòng)電路

+關(guān)注

關(guān)注

153文章

1529瀏覽量

108493 -

開關(guān)管

+關(guān)注

關(guān)注

4文章

226瀏覽量

21643

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

LED驅(qū)動(dòng)電源PFC電路的設(shè)計(jì)

三相PFC矩陣變換器電路拓?fù)浼?b class='flag-5'>工作原理是什么

功率因數(shù)校正電路(pfc)電路工作原理及應(yīng)用

開關(guān)電源pfc的工作原理介紹

pfc電路的作用及組成_pfc電路基本結(jié)構(gòu)和工作原理

pfc電路中用mos管需要注意哪些事項(xiàng)?

如何理解PFC PFC電路的工作原理

雙相PFC電路的工作原理

PFC驅(qū)動(dòng)電路的工作原理

PFC驅(qū)動(dòng)電路的工作原理

評(píng)論