了解DIP

DIP就是插件,采用這種封裝方式的芯片有兩排引腳,可以直接焊在有DIP結(jié)構(gòu)的芯片插座上或焊在有相同焊孔數(shù)的焊位中。其特點(diǎn)是可以很方便地實(shí)現(xiàn)PCB板的穿孔焊接,和主板有很好的兼容性,但是由于其封裝面積和厚度都比較大,而且引腳在插拔過程中很容易被損壞,可靠性較差。

DIP是最普及的插裝型封裝,應(yīng)用范圍包括標(biāo)準(zhǔn)邏輯 IC,存貯器 LSI,微機(jī)電路等,小外形封裝(SOP)、派生出SOJ(J型引腳小外形封裝)、TSOP(薄小外形封裝)、VSOP(甚小外形封裝)、SSOP(縮小型SOP)、TSSOP(薄的縮小型SOP)及 SOT(小外形晶體管)、SOIC(小外形集成電路)等。

DIP器件組裝設(shè)計(jì)缺陷

PCB封裝孔比器件大

PCB的插件孔,封裝引腳孔按照規(guī)格書繪制,在制版過程中因孔內(nèi)需要鍍銅,一般公差在正負(fù)0.075mm。PCB封裝孔比實(shí)物器件的引腳太大的話,會(huì)導(dǎo)致器件松動(dòng),上錫不足、空焊等品質(zhì)問題。

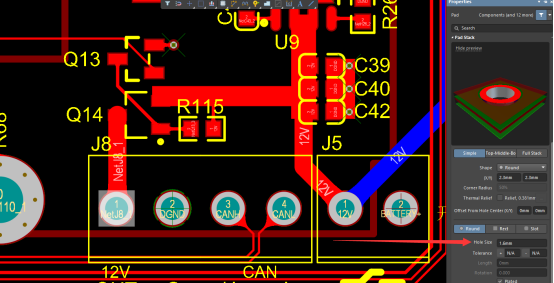

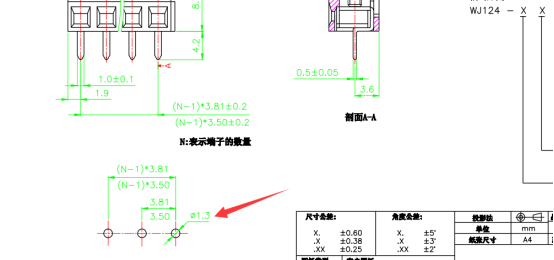

見下圖,使用WJ124-3.81-4P_WJ124-3.81-4P(KANGNEX)的器件引腳是1.3mm,PCB封裝孔是1.6mm,孔徑太大導(dǎo)致過波峰焊時(shí)空焊。

接上圖,按設(shè)計(jì)要求采購WJ124-3.81-4P_WJ124-3.81-4P(KANGNEX)的元器件,引腳1.3mm是正確的。

PCB封裝孔比器件小

PCB板中插件元器件焊盤上的孔小,元器件無法插入。此問題解決辦法只能是把孔徑擴(kuò)大再插件,但是會(huì)孔無銅,如果是單雙面板可以使用此方法,單雙面板都是外層電氣導(dǎo)通的,焊上錫可以導(dǎo)通;多層板插件孔小,內(nèi)層有電氣導(dǎo)通的情況下只能重做PCB板,因內(nèi)層導(dǎo)通無法擴(kuò)孔補(bǔ)救。

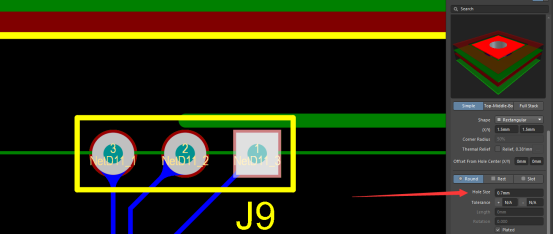

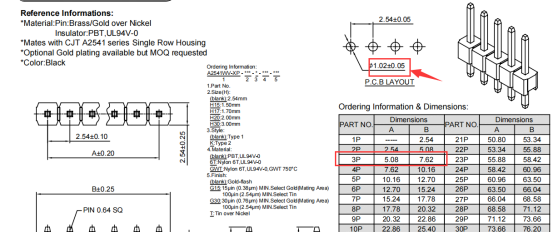

見下圖,按設(shè)計(jì)要求采購A2541Hwv-3P_A2541HWV-3P(CJT)的元器件,引腳是1.0mm,PCB封裝焊盤孔是0.7mm,導(dǎo)致無法插入。

接上圖,按設(shè)計(jì)要求采購A2541Hwv-3P_A2541HWV-3P(CJT)的元器件,引腳1.0mm是正確的。

封裝引腳間距與器件不同

DIP器件的PCB封裝焊盤不只是孔徑與引腳一致,而且引腳的間距同樣要一樣的距離,引腳孔的間距與器件不一致會(huì)導(dǎo)致器件無法插入,腳距可調(diào)的元器件除外。

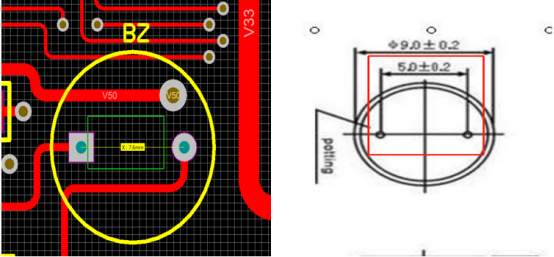

見下圖,PCB封裝引腳孔距是7.6mm,采購的元器件引腳孔距是5.0mm,相差2.6mm導(dǎo)致器件無法使用。

PCB封裝孔距過近

PCB設(shè)計(jì)繪制封裝時(shí)需注意引腳孔的距離,引腳孔間距小即便是裸板能生成出來,在組裝時(shí)過波峰焊也容易造成連錫短路。

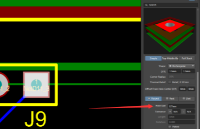

見下圖,可能因引腳距離小導(dǎo)致連錫短路,波峰焊連錫短路的原因有很多種,如果在設(shè)計(jì)端能夠提前對可組裝性進(jìn)行預(yù)防,可降低問題的發(fā)生率。

DIP器件引腳問題案例

物料尺寸與PCB焊盤孔尺寸不匹配

問題描述

某產(chǎn)品DIP過完波峰焊后發(fā)現(xiàn),網(wǎng)絡(luò)插座固定腳焊盤上錫嚴(yán)重不足,屬于空焊。

問題影響

導(dǎo)致網(wǎng)絡(luò)插座與PCB板的穩(wěn)固性變差,產(chǎn)品使用過程中會(huì)導(dǎo)致信號pin腳受力,最終導(dǎo)致信號pin腳的連接,影響產(chǎn)品性能,造成用戶使用中出現(xiàn)故障的風(fēng)險(xiǎn)。

問題延伸

網(wǎng)絡(luò)插座的穩(wěn)固性差,信號pin腳的連接性能差,存在品質(zhì)問題,因此可能給用戶帶來安全隱患,最終造成的損失是不可想象的。

DIP器件組裝分析檢查

DIP器件引腳相關(guān)問題非常多,很多關(guān)鍵點(diǎn)容易被忽視而造成最后廢板,那么要如何快速完整的一次性解決這類問題呢?

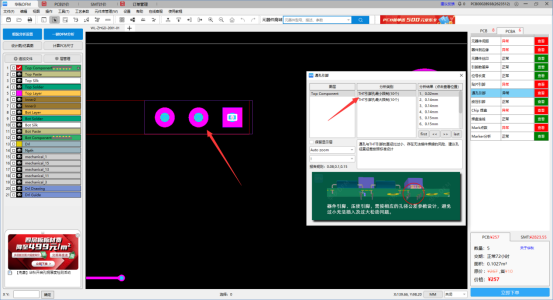

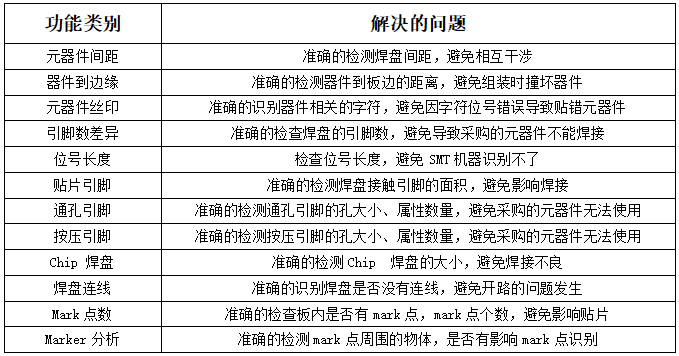

這里可以使用華秋DFM軟件的組裝分析功能,對DIP器件的引腳有專項(xiàng)檢查,檢查項(xiàng)有通孔的引腳數(shù)、THT引腳限大、THT引腳限小、THT引腳的屬性,引腳的檢查項(xiàng)基本涵蓋DIP器件引腳設(shè)計(jì)可能出現(xiàn)的問題。

在PCB設(shè)計(jì)完成后,使用PCBA裝配分析功能,可提前發(fā)現(xiàn)設(shè)計(jì)的缺陷,在產(chǎn)品生產(chǎn)前解決設(shè)計(jì)異常,還可避免在組裝過程時(shí)出現(xiàn)設(shè)計(jì)問題,耽誤生產(chǎn)時(shí)間、浪費(fèi)研發(fā)成本。

其組裝分析功能具有10大項(xiàng)、234細(xì)項(xiàng)檢查規(guī)則,涵蓋所有可能發(fā)生的組裝性問題,比如器件分析,引腳分析,焊盤分析等,可解決多種工程師無法提前預(yù)料的生產(chǎn)情況。

華秋DFM軟件是國內(nèi)首款免費(fèi)PCB可制造性和裝配分析軟件,擁有300萬+元件庫,可輕松高效完成裝配分析。

目前已有30+萬工程師正在使用,更有超多行業(yè)大咖強(qiáng)烈推薦!操作簡單易上手,不光提高工作效率,還能提高容錯(cuò)率!

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_fsylt.zip

-

pcb

+關(guān)注

關(guān)注

4319文章

23084瀏覽量

397638 -

元器件

+關(guān)注

關(guān)注

112文章

4713瀏覽量

92245 -

DFM

+關(guān)注

關(guān)注

8文章

464瀏覽量

28200 -

DIP

+關(guān)注

關(guān)注

0文章

241瀏覽量

30142

原文標(biāo)題:【避坑總結(jié)】那些關(guān)于DIP器件不得不說的坑

文章出處:【微信號:gh_9b9470648b3c,微信公眾號:電子發(fā)燒友論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

有關(guān)充電電池不得不說的幾個(gè)問題

那些關(guān)于DIP器件不得不說的坑

Android系統(tǒng)開發(fā)環(huán)境搭建不得不說的的那些事(二)

(免費(fèi)資料+福利)多層高速pcb設(shè)計(jì)中那些不得不說的事

【系列直播免費(fèi)分享】多層高速pcb設(shè)計(jì)中那些不得不說的事

那些關(guān)于DIP器件不得不說的坑

那些關(guān)于DIP器件不得不說的坑

筆記本電池不得不說的秘密

那些關(guān)于DIP器件不得不說的坑

那些關(guān)于DIP器件不得不說的坑

【避坑總結(jié)】那些關(guān)于DIP器件不得不說的坑

【避坑指南】那些關(guān)于DIP器件不得不說的坑

【避坑總結(jié)】那些關(guān)于DIP器件不得不說的坑

【避坑總結(jié)】那些關(guān)于DIP器件不得不說的坑

【避坑總結(jié)】那些關(guān)于DIP器件不得不說的坑

評論