FPGA 的設計流程就是利用 EDA 開發軟件和編程工具對 FPGA 芯片進行開發的過程。原理圖和HDL(Hardware description language,硬件描述語言)是兩種最常用的數字硬件電路描述方法。其中,運用 HDL 設計方法具有更好的移植性、通用性以及利于模塊劃分的特點,在工作學習中被廣泛使用。典型 FPGA 的開發流程一般如下圖所示, 其包括功能定義/器件選型、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真、板級仿真以及芯片編程與調試等主要步驟。

第1節 功能定義/器件選型

在 FPGA 設計項目開始之前需要進行方案論證、系統設計和 FPGA 芯片的選型等準備性工作,在確定并評估好方案后需要進行系統功能的定義和模塊的劃分。根據方案中任務要求,如方案中所確定的系統功能以及復雜度,對硬件的工作速度和器件自身的資源、成本、以及性能指標等各個方面進行綜合考慮,選擇出較合適的器件類型。

**在設計方法上,一般都采用自頂向下的設計方法,首先將整個系統劃分成若干個基本模塊,然后再將每個基本模塊劃分為下一層次的基本單元,這樣依次劃分后確定好各個模塊的功能以及各個模塊需要設計的輸入輸出信號,再通過 EDA 工具進行各個模塊的設計。**最終要實現的目標是:針對每個輸入信號,利用 EDA 工具以及 FPGA 的資源設計出需要的輸出信號邏輯。

第2節 設計輸入( Design Entry)

設計輸入是指在 EDA 工具中,通過使用該開發軟件設計出所希望得到的系統或電路的一個過程。在日常工作學習中 最常使用的方式是通過硬件描述語言( HDL)的方式來描繪設計出最終的數字電路 。以此方式設計電路的過程需要在 EDA 軟件上通過文本描述,將實際的電路用硬件語言表述出來。

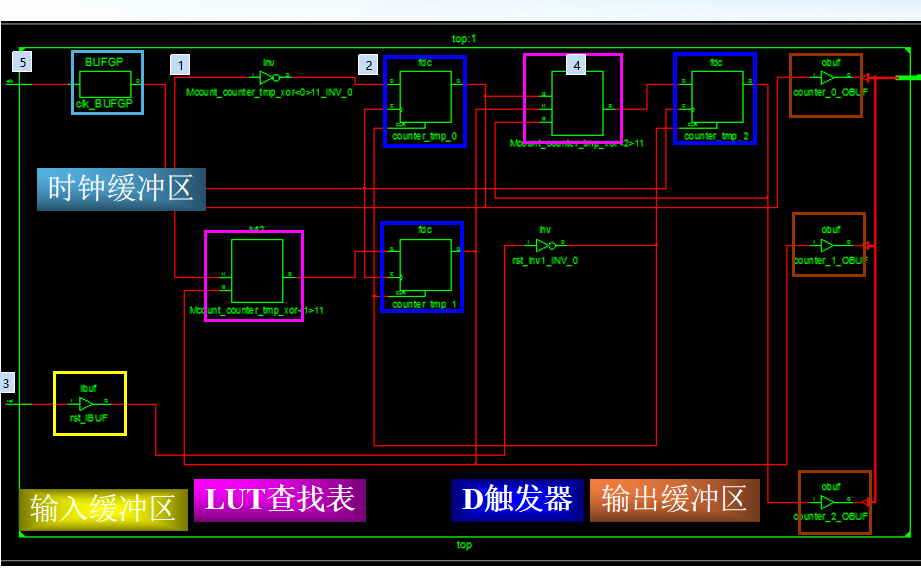

設計好文本后,編譯器會將硬件語言進行綜合、布局布線,最后轉換成一個個的邏輯門、寄存器、數據選擇器等實際電路。 設計師接觸比較多的 HDL 語言是行為 HDL,其主流語言是 Verilog HDL 和 VHDL,這兩種語言都是 IEEE 的標準,雖然兩者在語法結構以及設計標準上存在差別,但是都有一個共同的特點:語言與芯片工藝無關。在任一款 FPGA 芯片上,使用任何一種語言都可以設計出想要的數字電路。

另一種設計方式是使用原理圖輸入的方法進行設計輸入。原理圖輸入方式是一種最直接的描述方式,通過從元件庫中調出來需要的器件,畫出原理圖。

這一方式有點類似于硬件開發過程中設計原理圖的過程, 其在可編程邏輯陣列發展的前期應用的比較廣泛。使用這種方法具有設計直觀且易于仿真的優勢,但是設計效率不高,且難以維護改動,對模塊的構造和重用的支持度極不友好。當芯片升級后,所有的原理圖需要重新進行一定的改動,可移植性很差。

除了這 IEEE 標準語言外還有廠商自己的語言, 在實際的設計中也可以用 HDL 為主,原理圖為輔的混合設計方式,以發揮兩者的各自特色與優勢。

第3節 功能仿真( RTL-Simulation)

功能仿真也稱為綜合前仿真,用戶設計好數字邏輯后需要檢查自己的設計是否符合預期,在不需要綜合之前通過仿真軟件對電路進行邏輯驗證。

在功能仿真器件電路可以不用考慮延遲等因素,僅對初步的功能進行檢驗。通過建立測試平臺即 Testbench,利用波形編譯器(仿真軟件)和硬件描述語言建立好波形文件和激勵信號,在仿真軟件上會模擬實際電路的波形顯示出輸出波形信號,并生成報告文件。用戶通過觀察各個時間點信號的變化情況來驗證自己所設計邏輯的正確性。

綜合前仿真在 FPGA 開發過程中不是一定要進行的步驟,但卻是極為關鍵的一步。在實際的工作學習中,充分利用好仿真工具,能夠提高設計的效率并及時發現設計缺陷,從而為后續的開發過程提供保障。常用的硬件描述語言的仿真工具有 Model Tech 公司的 ModelSim、 VCS、 Ncsim 以及 NC-VHDL 等軟件。

第4節 綜合優化( Synthesis)

綜合即針對給定的電路實現功能和實現該電路的約束條件,如速度、功耗、成本及電路類型等,通過計算機進行優化處理獲得一個能滿足上述要求的電路設計方案。

也就是說,被綜合的文件是HDL 文件(或其他相應文件),綜合的依據是邏輯設計的描述和各種約束條件,綜合的結果則是一個硬件電路的實現方案,該方案必須同時滿足預期的功能和約束條件。

對于綜合來說,滿足要求的方案可能有多個,綜合器將產生一個最優的或接近最優的結果。因此,綜合的過程也就是設計目標的優化過程,最后獲得的結構與綜合器的工作性能有關。 常用的綜合工具有 Synplicity 公司的 Synplify/Synplify Pro 軟件以及各個 FPGA 廠家自己推出的綜合開發工具。

第5節 綜合后仿真

綜合后仿真是用來檢查綜合結果是否和原設計一致。后仿真與前仿真的區別在于: 前仿真是指綜合前的仿真,如在 Modelsim 對撰寫的代碼直接進行仿真,而后仿真是綜合后的仿真,也就是功能仿真。

假設設計師在 Modelsim 中用 HDL 編寫了一個計數器代碼, 其通過了行為級的仿真后被加載到 quartus 或者其他的綜合工具中進行綜合, 完成綜合后會生成功能網表, 將行為語言轉換成寄存器傳送級語言, 此時設計師再將其加載到 Modelsim 中進行的仿真被叫做后仿真。

后仿真成功后還需要在 quartus 中進行映射和布局布線, 并進行時序分析生成時序網表,描述器件里門或者布線的延時。 最后將延時網表和功能網表一起加載到 Modelsim 中仿真,這一仿真為門級仿真,而在實際的設計過程中,一般來說不做綜合后仿真也不會帶來太大的影響。

第6節 布局布線( Place & Routes)

布局布線可理解為利用實現工具把邏輯映射到目標器件結構的資源中從而決定邏輯的最佳布局,選擇邏輯與輸入輸出功能鏈接的布線通道進行連線,并產生相應文件(如配置文件與相關報告)。

實現是 將綜合生成的邏輯網表配置到具體的 FPGA 芯片上,布局布線是其中最重要的過程 。在完成綜合之后,就是相當于有了各種元件, 但如何建立元件之間的連接,就像在 PCB 上把元件放在哪里,元件之間的連接以及相連關系又是怎么樣的,這個都是布局布線完成的工作,綜合的結果可能每次都一樣,但是布局布線的結構基本每次都不會一樣。

布局將邏輯網表中的硬件原語和底層單元合理地配置到芯片內部的固有硬件結構上,并且往往需要在速度最優和面積最優之間作出選擇。布線根據布局的拓撲結構,利用芯片內部的各種連線資源,合理正確地連接各個元件。

目前, FPGA 的結構非常復雜,特別是在有時序約束條件時,需要利用時序驅動的引擎進行布局布線。布線結束后,軟件工具會自動生成報告,提供有關設計中各部分資源的使用情況。由于只有 FPGA 芯片生產商對芯片結構最為了解,所以布局布線必須選擇芯片開發商提供的工具。

第7節 時序仿真( Timing)

時序仿真,也稱為后仿真,是指將布局布線的延時信息反標注到設計網表中來檢測有無時序違規(即不滿足時序約束條件或器件固有的時序規則,如建立時間、保持時間等)現象。

時序仿真使用布局布線后器件給出的模塊和連線的延時信息, 在最壞的情況下對電路的行為作出實際地估計。時序仿真使用的仿真器和功能仿真使用的仿真器是相同的,所需的流程和激勵也是相同的,唯一的差別是: 時序仿真加載到仿真器的設計包括基于實際布局布線設計的最壞情況的布局布線延時,并且在仿真結果波形圖中時序仿真后的信號加載了時延,而功能仿真沒有。

由于不同芯片的內部延時不一樣,不同的布局布線方案也給延時帶來不同的影響。因此在布局布線后,通過對系統和各個模塊進行時序仿真,分析其時序關系,估計系統性能,以及檢查和消除競爭冒險是非常有必要的。在功能仿真中介紹的軟件工具一般都支持綜合后仿真。

第8節 板級仿真與驗證

板級仿真主要應用于高速電路設計中,對高速系統的信號完整性、電磁干擾等特征進行分析,一般都以第三方工具進行仿真和驗證,在實際的工作中一般接觸較少。

第9節 編程與調試

設計的最后一步就是芯片的編程與調試。編程是指將 FPGA 開發工具最后產生使用的數據文件(位數據流文件, Bitstream Generation)加載到 FPGA 芯片中。

其中,芯片編程需要滿足一定的條件,如編程電壓、 編程時序和編程算法等,而這些條件一般廠家都會事先完成設計, 設計師直接按照規范操作即可。

數據文件下載到 FPGA 芯片中以后還需要進行調試驗證,=邏輯分析儀(Logic Analyzer, LA)便是 FPGA 設計的主要調試工具。使用 LA 需要引出大量的測試管腳,且 LA 價格昂貴,但是當工程較大、所需要調試觀察的信號過多時,仍舊需要 LA 來對芯片內部的信號進行觀察驗證。

目前,主流的 FPGA 芯片生產商都提供了內嵌的在線邏輯分析儀(如 Xilinx ISE 中的 ChipScope、 Altera QuartusII 中的 SignalTapII 以及 SignalProb),它們只需要占用芯片少量的邏輯資源便可達到同樣的效果,在實際的工程調試中發揮了極大的作用。之后將會詳細介紹 SIGNALTAP 工具的使用。

版權聲明:本文為CSDN博主「原來如此呀」的原創文章,遵循CC 4.0 BY-SA版權協議,轉載請附上原文出處鏈接及本聲明。

原文鏈接:https://blog.csdn.net/Royalic/article/details/120995615

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603004 -

芯片

+關注

關注

455文章

50714瀏覽量

423152 -

eda

+關注

關注

71文章

2755瀏覽量

173201 -

HDL

+關注

關注

8文章

327瀏覽量

47377

發布評論請先 登錄

相關推薦

FPGA入門之FPGA 開發流程

FPGA入門之FPGA 開發流程

評論