今天在群里有工程師問我,怎么才叫學會了FPGA,怎么才叫學好了FPGA?我相信有很多朋友有類似的問題,因為在多數人的潛意識里,F(xiàn)PGA是非常高深莫測的技術,能夠玩轉FPGA的都是大神級的人物。

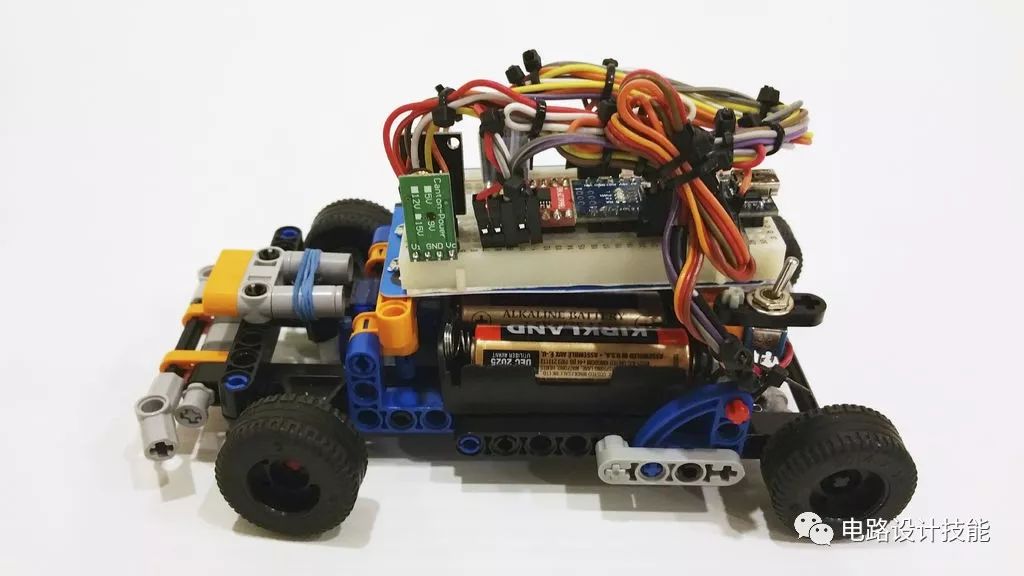

其實呢,這是一種誤解,你可以把FPGA當做是數字世界的樂高(Lego),它由幾種最基本的單元(每種單元數量有很多很多)讓你組成自己想實現(xiàn)的功能。能玩好樂高就一定能玩好FPGA。樂高玩得好不好,取決于什么因素?

通過一些最基本的積木塊可以拼出任何復雜的物體

- 第一要素 - 先要了解供你玩的“樂高”套裝里都有哪些單元?每個單元都有哪些特性?不同單元之間是如何拼接的?沒有這些全局的信息和知識在你的腦子里,你要從幾千個piece里面去組裝一輛車、構建一個城堡,將是非常困難甚至不可能的。

- 第二要素 - 要有正確的思維方式。你至少要知道搭建一輛車需要四個輪子、一個方向盤、一個發(fā)動機,這些部件之間如何通過其它的單元有機組合在一起,彼此之間如何搭配。不知道車子需要輪子,不知道輪子要裝在底盤上是無法組裝出一輛車來的,即便有再多的單元也沒有用。

要通過積木構建一輛車,首先要知道都有哪些積木零件可以用,其次要知道這些部件之間的邏輯關系

學習使用FPGA的道理跟玩樂高沒啥區(qū)別,同樣是:

- 了解FPGA是什么?玩樂高的人不用操心什么是樂高,這個知識是由玩樂高的人的父母掌握了,并幫他選好型了;

- 要充分了解FPGA內部都有什么功能單元(邏輯單元、存儲器、時鐘產生、可編程IO等) ,這些單元都有什么用?用起來都有哪些要注意的地方,各個單元之間如何配合?尤其是針對你要用的具體型號,你要知道你用的這個型號的器件內部的各種功能單元具體有多少數量,夠不夠你項目使用的;

- 數字邏輯的設計思想 - 針對任意一項具體的功能,如何組合你器件內的單元來實現(xiàn),需要哪些單元?如何連接這些單元?各個單元之間連接的先后順序如何?這就需要比較扎實的數字電路/數字系統(tǒng)設計的基礎知識以及邏輯思維能力。

當然你也需要一些工具來幫助你實現(xiàn),比如一套從頭到尾執(zhí)行的設計環(huán)境(FPGA廠商提供的編譯工具 - Lattice的Diamond、Intel的Quartus、Xilinx的Vivado),一種連接你的邏輯思維和機器操作之間的溝通工具 - 設計語言(原理圖、Verilog、VHDL等等)。

下面我們以小腳丫FPGA為例,看看我們要學好FPGA必須掌握哪些知識。

首先FPGA是什么?

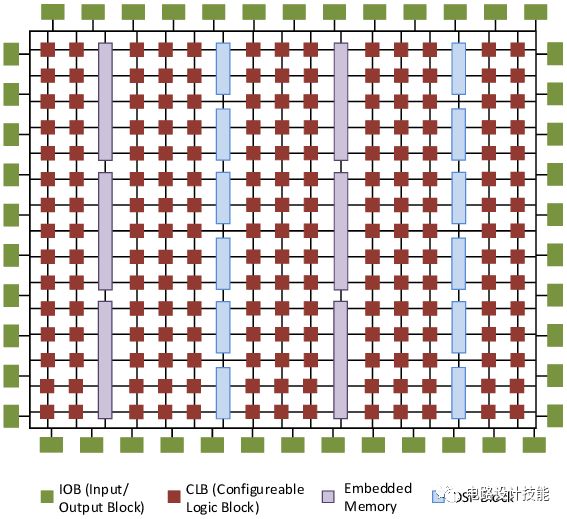

四個字母Field(現(xiàn)場) Programmable(可編程) Gate(邏輯門) Array(陣列)凸顯了大量的 邏輯門單元 ,這些邏輯單元是可以在任何地方隨時進行組裝的,這是不是跟樂高玩具一樣?邏輯門單元是構成一切數字邏輯器件的基本單元,在數字世界里你想做任何事情、實現(xiàn)任何功能,都可以通過邏輯門的堆砌來實現(xiàn),也就是說FPGA在數字領域里幾乎無所不能,因此n年前我國的某一個FPGA公司在向國務院領導描述其產品的時候稱他們做的是“萬能芯片”(用這種通俗易懂的說法忽悠國家的經費)。萬能有些夸張,但FPGA高度靈活,理論上來講,只要有足夠的資源(積木數量足夠多)幾乎可以實現(xiàn)數字域的任何功能,受限的是速度、功耗以及系統(tǒng)的成本。

一個典型的FPGA架構及其內部主要功能單元

FPGA里面有什么?

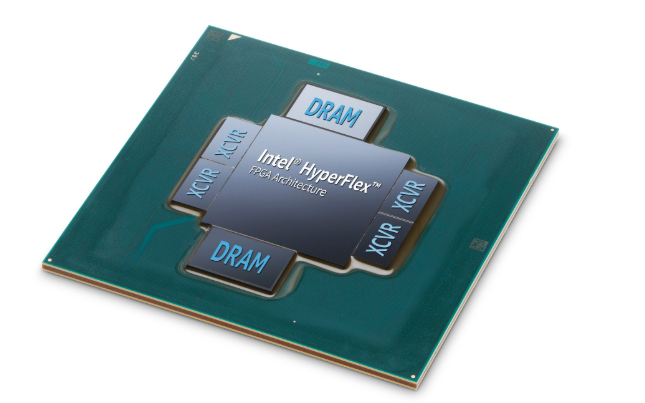

我們以基于Lattice的FPGA的小腳丫看一下該FPGA內部都有哪些資源以及相應資源的數量,如下是該器件LCMXO2-4000HC-4MG132C內部的功能框圖:

Lattice版本小腳丫FPGA芯片內部的主要功能單元

該器件的具體資源參數如下:

- 4320個LUT資源 - 每個LUT(查找表)有4個輸入,16種狀態(tài),并一個寄存器,這就像樂高里的積木塊,用來實現(xiàn)各種邏輯功能,至于4320是多還是少?這個要看你做的項目需要的邏輯資源,對于FPGA的初學者來講4000多個LUT已經足夠多,實現(xiàn)很多沒聽說過的功能都已經綽綽有余了;

- 92Kbit RAM - 這是在邏輯之外的成塊狀的存儲器,可以靈活配置成各種位寬、各種讀寫模式的存儲功能,比如FIFO、雙口RAM等;

- 96Kbit用戶閃存 - 這是Lattice 的一個創(chuàng)新,后來Altera/Intel也學著做了MAX10,就是將配置FPGA的存儲器從外面的PROM變成了集成在FPGA內部的Flash,可以反復編程,從此FPGA不再外掛一個累贅了,用起來就像PLD一樣方便;

- 嵌入式功能塊(硬核):一路SPI、一路定時器、2路I2C,這可是MCU除了ALU、總線之外最基本的功能模塊,都硬化到該FPGA內部了,也就意味著如果你想用這個FPGA做一個MCU玩玩,可以直接將這些已經硬化的功能塊通過總線掛在處理器上,沒必要再寫這些功能,并且占用邏輯資源了;

- 2+2路PLL+DLL - 我們前面講過外部常用的時鐘產生器(比如晶振)產生的頻率不高,但FPGA內部可以工作到很高的速度,因此現(xiàn)在幾乎所有FPGA器件都有內置的PLL將外部的低頻率的時鐘整到很高頻率,比如小腳丫的外部時鐘為12MHz,內部PLL可以將它倍頻到400MHz,非常快吧?

- 支持DDR/DDR2/LPDDR存儲器 - 這是說該器件能夠直接掛這些存儲器,適配它們的電平和時序;

- 104個可熱插拔I/O - 每個I/O管腳可以單獨編程為輸入、輸出、上拉或下拉、并可以設置器輸出阻抗,以便支持不同的接口協(xié)議,就像城市連接外部的道路可進可出、有的鋪瀝青、有的是土路;

- 內核電壓2.5-3.3V,供電電壓的范圍比較寬;

- 132腳BGA封裝,引腳間距0.5mm,芯片尺寸8mm x 8mm;

FPGA能做什么?

知道了FPGA內部的資源,也就心里有數它能做什么了。就像一座城堡,內部居民的生活豐富多彩,無論他們以何種形式進行組合,他們所做的事情取決于這些居民以及他們擁有的資源,其生活模式被城堡的設計者所定義(城市管理、文化等等等)。

但從宏觀上來看這個城堡起到的功能很大程度上取決于這個城堡同外部世界的連接,沒有這些同系統(tǒng)的連接,城堡內部的任何行為對于系統(tǒng)來講都沒有意義。FPGA可以是系統(tǒng)的一個重要組成部分,但它僅僅是一個部分而已,就像一個城堡一樣,它只有同外部進行連接并執(zhí)行系統(tǒng)通過這些連接給其分配的功能才有意義。

因此FPGA通過其I/O管腳連接外面的世界,我們使用的小腳丫芯片有132個管腳,除去電源、地之外還有104個管腳可以用來同外界進行聯(lián)系。

)

做為一款讓FPGA初學者學習的平臺,首先要滿足初學者基于掌握的數字電路知識進行做項目的定位,先要體驗組合邏輯、時序邏輯、狀態(tài)轉換等數字電路的基礎概念,而體驗這些概念就需要一些必要的輸入(按鍵、開關)和必要的輸出(通過單色LED燈、三色燈、數碼管進行各種方式的顯示),綜合考慮板子的尺寸以及初學者隨時隨地能練習的要求,我們經過取舍后選定了如下的板上功能及連接:

通過FPGA的IO管腳連接的板上的功能

板載資源:

- 兩位7段數碼管 - 可以以狀態(tài)、數值的變化來顯示內部邏輯運行的信息;

- 兩個RGB三色LED - 可以以LED的亮度、顏色燈的變化顯示內部邏輯運行的信息;

- 8路用戶LED - 可以通過組合來形象地顯示內部邏輯運行的信息;

- 4路撥碼開關 - 做為狀態(tài)的輸入;

- 4路按鍵 - 做為外部條件變換的輸入;

板子上的這些功能說明

當然作為一個靈活的學習模塊,我們還要給用戶留下一定的靈活擴展的空間,讓用戶以各種方式來連接其計劃連接的其它器件,在這個模塊的周邊我們留出了36個信號管腳(4個電源、地除外)給用戶,用戶可以靈活配置、應用這些管腳,讓自己的系統(tǒng)充分利用這些管腳讓FPGA內部的邏輯資源執(zhí)行分配的任務。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603013 -

單片機

+關注

關注

6035文章

44554瀏覽量

634668 -

存儲器

+關注

關注

38文章

7484瀏覽量

163765

發(fā)布評論請先 登錄

相關推薦

怎樣才叫學好了FPGA?

怎樣才叫學好了FPGA?

評論