CLB是指可編程邏輯功能塊(Configurable Logic Blocks),顧名思義就是可編程的數(shù)字邏輯電路。CLB是FPGA內(nèi)的三個基本邏輯單元。CLB的實際數(shù)量和特性會依器件的不同而不同,但是每個CLB都可配置,在Xilinx公司的FPGA器件中,CLB由2個 相同的SliceL或則一個SliceL和一個SliceM構成。每個Slice不僅可以用于實現(xiàn)組合邏輯、時序邏輯。其中,SliceM還可以配置為分布式RAM和分布式ROM。

下面以Xilinx的ZYNQ的7000系列為例介紹其功能與結構

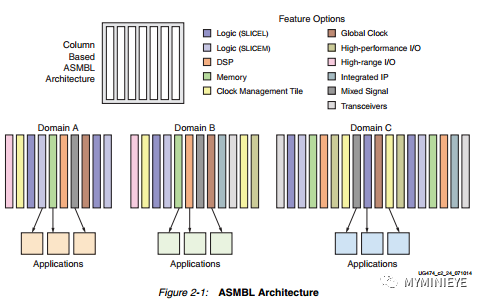

ZYNQ7000系列采用了Xilinx全新的第四代ASMBL架構。

新的架構優(yōu)化了芯片布局,消除了IO數(shù)量增長帶來的芯片陣列的尺寸約束;

新的架構能夠滿足在芯片的任何位置放置電源和地;

增加了更多電源和地;

允許多種完全不同功能的IP單元在芯片內(nèi)獨立排布;

獨特的SSI技術;

且分布式RAM和移位寄存器只能在SliceM中

1.SLICE: (1Slice=4LUT+8FF)

Slice是Xilinx公司定義的基本邏輯單位,其內(nèi)部結構如圖1-4所示,一個Slice由四個6輸入的LUTS、進位邏輯、算術邏輯、存儲邏輯和多路復選器組成。算術邏輯包括一個異或門(XORG),一個異或門可以使一個Slice實現(xiàn) 2bit全加操作,專用與門用于提高乘法器的效率;進位邏輯由專用進位信號和函數(shù)復用器(MUXC)組成,用于實現(xiàn)快速的算術加減法操作;4輸入函數(shù)發(fā)生器用于實現(xiàn)4輸入LUT、分布式RAM或16比特移位寄存器(Virtex-5系列芯片的Slice中的兩個輸入函數(shù)為6輸入,可以實現(xiàn)6輸入LUT或 64比特移位寄存器);進位邏輯包括兩條快速進位鏈,用于提高CLB模塊的處理速度

每個Slice包含:

?四個6輸入查找表LUT

?八個存儲單元

?多路復選器

?進位邏輯

所有Slice均使用這些單元來提供邏輯,算術和ROM功能。在

此外,某些slice還支持兩個附加功能:使用分布式存儲數(shù)據(jù)

RAM和32位寄存器的移位數(shù)據(jù)。支持這些附加功能的slice

稱為SLICEM;其他的則稱為SLICEL。

SLICEL如圖2-4所示。

每個CLB可以包含兩個SLICEL或一個SLICEL和一個SLICEM。

Slices分為SliceL和SliceM,一般情況下,SliceL>SliceM數(shù)

2.LUT查找表

1個Slice包含4個6輸入的LUT,兩個LUT通過F7MUX進行級聯(lián)可以形成一個7輸入的LUT,1個Slice可以形成2個7輸入的LUT;還可通過F8MUX進行級聯(lián)形成一個8輸入的LUT,邏輯資源換算關系:6輸入查找表是4輸入查找表的1.6倍查找表LUT本質是RAM,相當于一個多路選擇器LUT可參與進位邏輯,進行算數(shù)運算單元進行異或運算等,也可直接輸出。

3.存儲單元

每個Slice有8個存儲單元,4個可配置成DFF或者鎖存器,另外4個只能配置為DFF

控制信號

控制信號

而SliceL與SliceM最大的區(qū)別就是沒有分布式RAM和移位寄存器。

4.分布式RAM(僅限SliceM)

SLICEM可以配置成分布式RAM,多bit的情況需要增加相應倍數(shù)的LUT進行并聯(lián)。

分布式RAM比塊RAM有更好的靈活性,但塊RAM的資源比較寶貴,分布式RAM適用小規(guī)模存儲場景。

5.移位寄存器(僅限SliceM)

SLICEM在不使用觸發(fā)器的情況下可以設置成32bit的移位寄存器,4個LUT可級聯(lián)成128bit的移位寄存器。SliceM之間級聯(lián)還可形成更大的移位寄存器

6.多路復選器MUX

1個LUT可配置成4:1MUX

2個LUT最多可配置成8:1MUX

4個LUT最多可配置成16:1MUX

也可通過布線資源連接多個Slice形成更大規(guī)模的設計

但會占用布線資源,產(chǎn)生較大延遲

有兩條快速進位鏈,它與本列的上下slice的進位鏈相連,實現(xiàn)數(shù)據(jù)運算時的進位操作,每個slice有4bit 的進位鏈,每bit都由一個進位MUX和一個異或門組成

可實現(xiàn)加法/減法器時生成進位邏輯,也可產(chǎn)生一般邏輯。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603012 -

ROM

+關注

關注

4文章

563瀏覽量

85733 -

RAM

+關注

關注

8文章

1368瀏覽量

114646 -

CLB

+關注

關注

0文章

29瀏覽量

5950

發(fā)布評論請先 登錄

相關推薦

基于直方圖算法進行FPGA架構設計

FPGA架構演進之路 FPGA架構設計原則和實現(xiàn)挑戰(zhàn)

Altera加速替代ASIC市場關注FPGA架構和軟件創(chuàng)新

soc fpga架構下的讀心術

FPGA架構和應用基礎知識

【設計技巧】FPGA架構設計漫談

基于DSP+FPGA架構的在線棉結檢測裝置

基于DSP和FPGA架構的嵌入式圖像處理系統(tǒng)設計

FPGA的基礎架構

FPGA的基礎架構

評論