在IC領域,SRAM(Static Random-Access Memory)是一種靜態的隨機存取存儲器。“靜態”是相對于動態隨機存取存儲器(DRAM)而言,只要系統不斷電,里面儲存的數據就可以一直保持。而DRAM里面用電容儲存的數據就需要周期性地刷新。

為什么要聊一聊SRAM,因為比較大一點的IC芯片中都可能有SRAM的電路。如CPU中的 caches,或者一些芯片中用作緩存大量的數據(如果用常規的LATCH 或者 DFFP存大量數據,那所耗費的面積就太大了),或者作為IP用在ASIC和FPGA中。而且SRAM的基本原理相對比較簡單,好掌握。

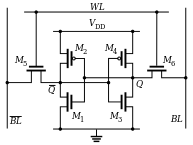

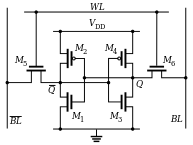

其實常用的SRAM的架構也很簡單,下圖就是包含6個晶體管的CMOS SRAM最基本單元。

兩個反相器的輸入、輸出Q,Q非交叉連接,再加上2個控制管M5和M6。

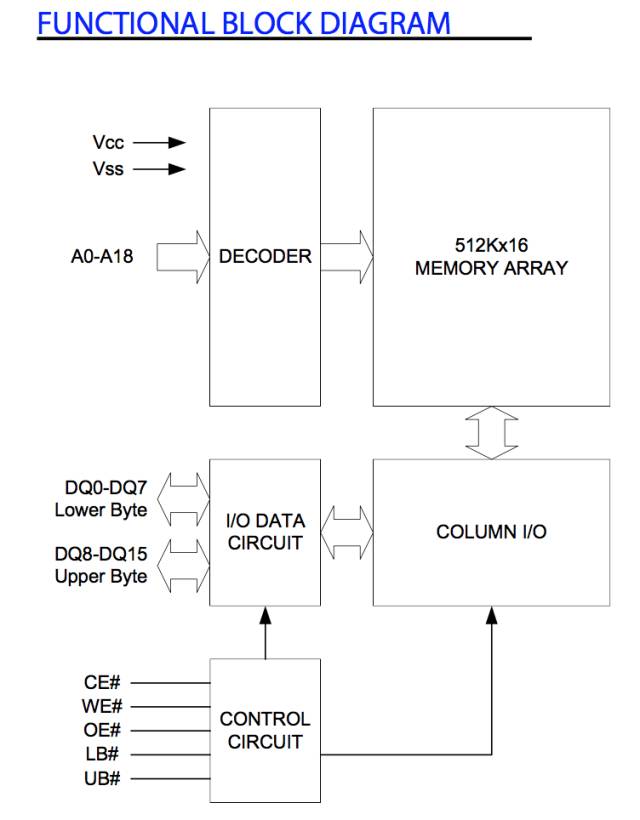

網上隨便找了一個SRAM的datasheet,截了一張功能塊的圖:

這個SRAM的容量就是8M bit ,就是8M X 6管基本單元。 左上是一個地址譯碼電路 產生6管單元中的WL/BL 信息。 中間的I/O DATA CIRCUIT 和 COLUMN I/O就是用來寫數據的bus線輸入以及讀數據bus線的輸出。最下面的CONTROL CIRCUIT是讀寫的控制電路。

SRAM有3種工作狀態:空閑standby , 讀 reading ,寫 writing .

Standby

如果WL都沒選中,那么控制管M

5與M6斷開,由M1– M4組成的兩個反相器作為latch一直保持自己的狀態。Reading

假設SRAM一開始存的內容為 0 , Q點的電位為低, Q非點為高。讀操作開始后,有上拉信號將BL/BL非這2條線拉為高電壓VDD,隨后譯碼選出的WL電壓變成VDD, 使得控制管M

5與M6導通,因為BL和BL非連到一個SA(放大器)的兩端,只要BL與BL有電位差,SA就會把這種差異放大,得到最終的輸出結果。當然這邊要注意這幾個管子的size,如果M6管比較強,BL在被拉低的過程中,Q點會被充電,電壓有可能會變高到超過M1的閾值電壓,從而導致這個latch存的值被沖掉。所以這邊M3 M6存在管子的size要求,簡單而言M3 > M6。具體的計算方法一些教科書上都有。

Writing

寫操作開始后,同樣也會有上拉信號將BL/BL非 拉為高電壓VDD,選中的WL電壓變成VDD,使得控制管M

5與M6導通,寫控制電路會驅動BL和BL非。假設現在要寫0,原來存的是1, 那BL和BL非就會被驅動成0和1,M6 與M4管開始fighting,直到Q點的電壓降到低于M1管的閾值電壓,M1關斷,SRAM存儲的值才能翻轉。同樣這邊管子M4 M6存在特定的size要求,簡單而言M6 > M4,不然M6 fighting 不過 M4,無法寫入數據。具體的size計算方法一些教科書上都有。

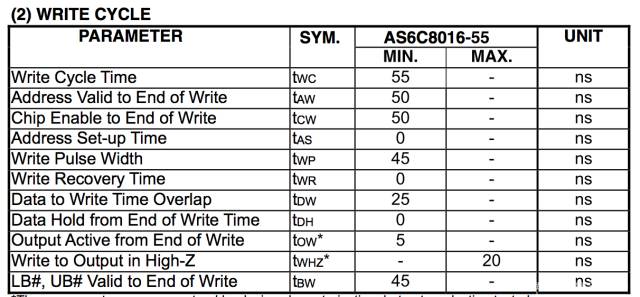

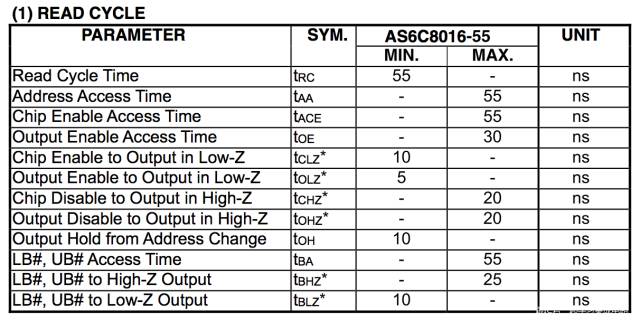

上面2張圖是我從SRAM datasheet里面找的AC特性,可以看出讀寫量級都是幾十ns的量級,不過這個時間應該跟SRAM的容量有很大的關系,容量小的更快一點,大家設計的時候可以參考一下

-

DRAM

+關注

關注

40文章

2316瀏覽量

183565 -

IC

+關注

關注

36文章

5957瀏覽量

175713 -

存儲器

+關注

關注

38文章

7494瀏覽量

163911 -

sram

+關注

關注

6文章

768瀏覽量

114712 -

隨機存取存儲器

+關注

關注

0文章

44瀏覽量

8989

發布評論請先 登錄

相關推薦

從焊接角度聊一聊,設計PCB的5個建議

來聊一聊Altium中Fill,Polygon Pour,Plane的區別和用法

聊一聊stm32的低功耗調試

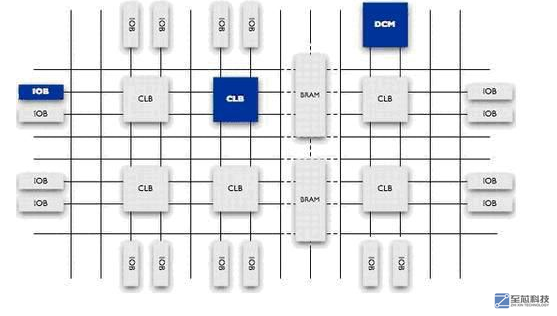

聊一聊7系列FPGA的供電部分

聊一聊FPGA的片內資源相關知識

聊一聊IIC總線設計

小米米聊2月19日停止服務 米聊宣布關閉服務器

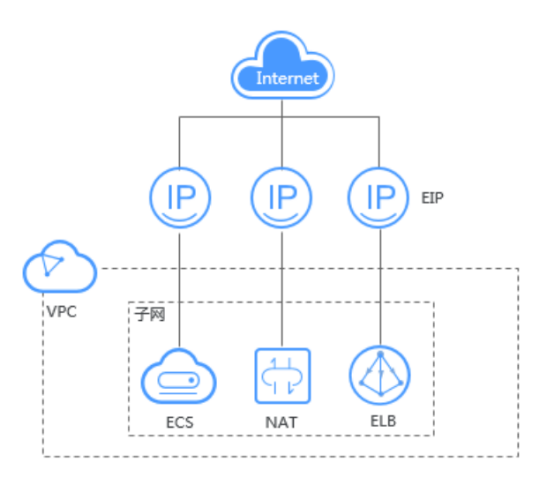

聊一聊華為云彈性公網IP的那些事兒

聊一聊IC領域中的SRAM

聊一聊IC領域中的SRAM

評論