數(shù)字仿真器(Simulator)是一種大型EDA工業(yè)軟件,是數(shù)字驗(yàn)證領(lǐng)域的基礎(chǔ)工具之一,也是為數(shù)不多的簽核(sign-off)級(jí)工具。其實(shí)歷史上第一款 EDA 軟件SPICE,就是從仿真開始的。可以說,EDA軟件從誕生之日起,就帶著強(qiáng)烈的仿真基因。因此,如果沒有一款獨(dú)立自主的數(shù)字仿真器,國產(chǎn)EDA實(shí)現(xiàn)對(duì)國外工具壟斷的打破就無從談起。

目前,行業(yè)主流的仿真器,諸如VCS,Xcelium, Questa等,都是國外EDA大廠花了數(shù)十年的時(shí)間開發(fā)、迭代而來的。這些軟件內(nèi)部設(shè)計(jì)極其復(fù)雜、代碼量巨大,單單維護(hù)的團(tuán)隊(duì)人數(shù)就可達(dá)數(shù)百人甚至上千人。由此可見,數(shù)字仿真器技術(shù)開發(fā)難度之大。

合抱之木,生于毫末;九層之臺(tái),起于累土。2021年11月,國內(nèi)系統(tǒng)級(jí)驗(yàn)證EDA解決方案提供商芯華章發(fā)布了首款數(shù)字仿真器產(chǎn)品穹鼎GalaxSim,并得到中科院半導(dǎo)體、芯來科技等用戶一線項(xiàng)目部署。GalaxSim在開發(fā)過程中,結(jié)合國產(chǎn)EDA的迫切需求,選擇了合適的技術(shù)路線、開發(fā)模式,依托研發(fā)團(tuán)隊(duì)的豐富EDA經(jīng)驗(yàn)及高效的工作,站在更高的技術(shù)起點(diǎn)上,用幾年的時(shí)間正在追趕國外幾十年的路。

現(xiàn)在我們梳理實(shí)踐所得和淺見,希望與行業(yè)同仁進(jìn)行分享交流,幫助志在推動(dòng)國內(nèi)EDA數(shù)字仿真器進(jìn)步的有志之士,提供一些可能的啟發(fā)和參考,共同建立良好的EDA發(fā)展生態(tài)。

本篇我們將以穹鼎GalaxSim為例,展示一款商用級(jí)別的數(shù)字仿真器從0到1的開發(fā)過程,包括商用仿真器的技術(shù)指標(biāo)、開發(fā)模式、技術(shù)路線等方面。

1. 數(shù)字仿真器的技術(shù)要求

數(shù)字仿真器在驗(yàn)證中發(fā)揮著舉足輕重的作用。判斷一款國產(chǎn)仿真器是否能真的商用,甚至可以與國際主流選擇的仿真器并駕齊驅(qū), 一般要看它是否滿足以下四點(diǎn)硬性要求:

1

全面的SystemVerilog語法覆蓋

SystemVerilog可以說是最復(fù)雜的語言之一,而數(shù)字仿真器又是EDA工具中對(duì)SystemVerilog支持最全面的工具。

2

仿真器相對(duì)其他驗(yàn)證工具,是sign-off級(jí)別的,因此要求仿真器必須嚴(yán)格按照事件驅(qū)動(dòng)型的算法進(jìn)行仿真調(diào)度,符合IEEE1800等標(biāo)準(zhǔn)。

3

高性能

仿真器的性能直接決定了用戶在驗(yàn)證上的成本。假如某個(gè)優(yōu)化可以使仿真速度提高2x, 那可以使原本一個(gè)月完成的回歸測(cè)試縮短到二周,從而給客戶省掉很大的驗(yàn)證支出。

4

高可靠性

作為大型工業(yè)軟件,仿真器的設(shè)計(jì)極其復(fù)雜。一款大型軟件,涉及到的模塊非常多,參與的開發(fā)者也非常多。如何確保軟件質(zhì)量可控,在客戶的超大設(shè)計(jì)上能跑幾十小時(shí),甚至幾周不出現(xiàn)故障,是考驗(yàn)一個(gè)仿真器能否真正商用的重要指標(biāo)之一。因此,作為用戶sign-off 的工具,仿真器的故障率必須極低。即使出現(xiàn)故障,也能在很短的時(shí)間內(nèi)排查并修復(fù)。

2.開發(fā)模式的選擇:瀑布式開發(fā)VS敏捷開發(fā)

?

?

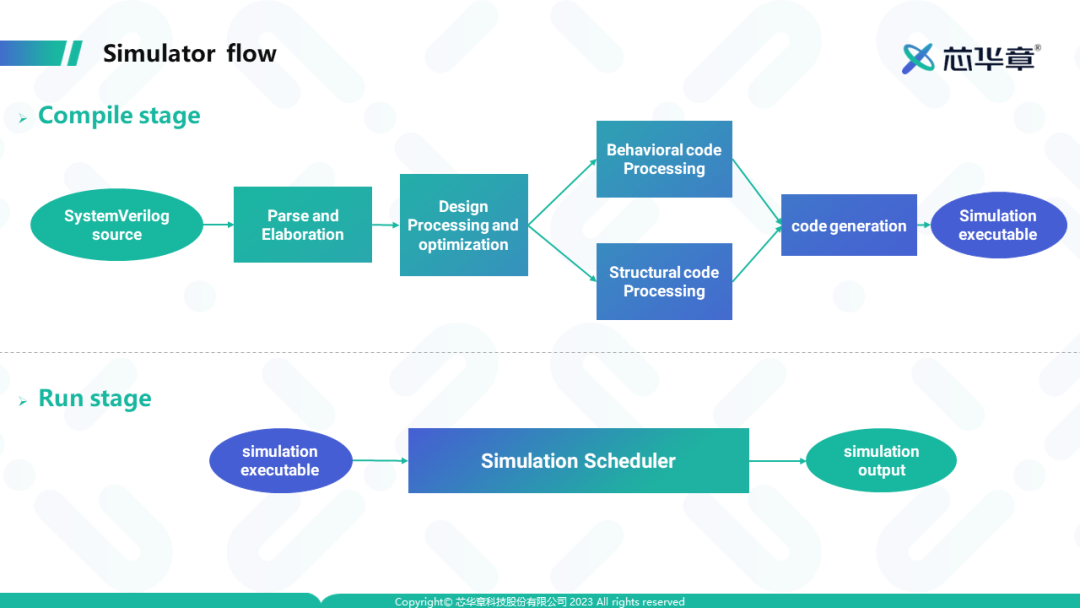

編譯型數(shù)字仿真器的原理如上圖所示,它從verilog source到最終機(jī)器碼生成,中間經(jīng)歷了多個(gè)環(huán)節(jié)。它既具備了Compiler的特點(diǎn),同時(shí)又是一個(gè)數(shù)字電路仿真器。它集成了多種底層技術(shù),涉及編譯、算法、圖論等知識(shí)。

盡管從概念上,我們可以把這個(gè)過程分解成不同的階段,但是在實(shí)際實(shí)現(xiàn)上,我們其實(shí)很難單獨(dú)把某一塊抽出來。以parser/elaboration階段為例,這個(gè)階段需要把RTL的語法解析出來。從功能上,它和后面的階段是不同的。然而,如果把它作為一個(gè)模塊獨(dú)立開發(fā),就會(huì)面臨無法測(cè)試的困難。因?yàn)橛行〆laboration的結(jié)果,需要到了runtime階段才可能測(cè)出是否正確。

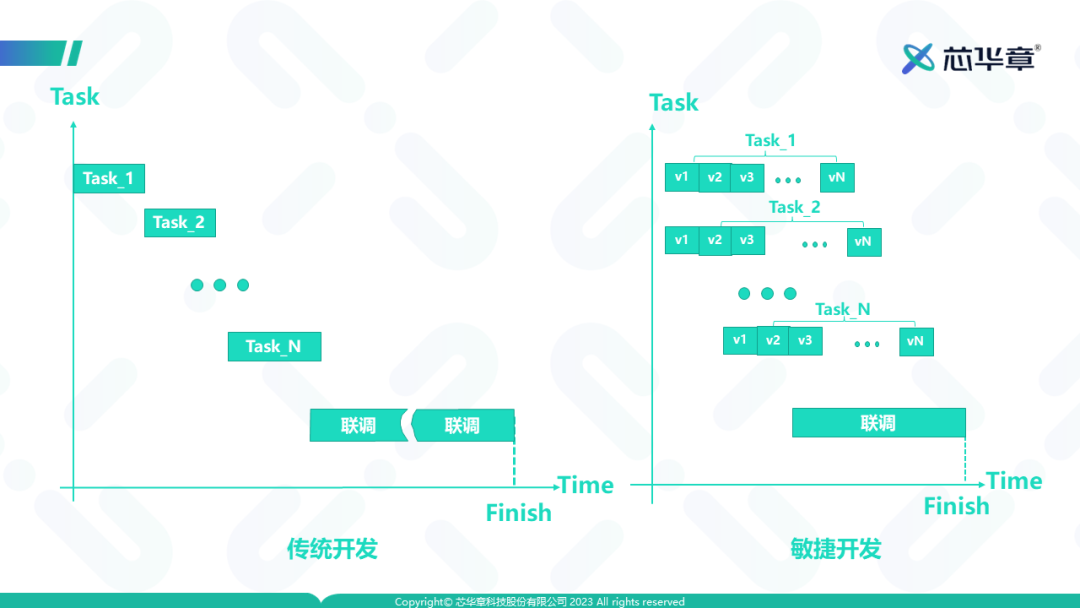

軟件開發(fā)有兩種模式,一種是傳統(tǒng)的瀑布式模式,把一個(gè)軟件劃分成若干模塊。每個(gè)模塊都定義好spec,然后分配給各個(gè)團(tuán)隊(duì)開發(fā);到了一定節(jié)點(diǎn),再進(jìn)行聯(lián)調(diào)。另一種是敏捷開發(fā),就是快速將flow打通,進(jìn)行不停地迭代,就像生物界胚胎的成長(zhǎng)一樣,逐步將軟件迭代成熟。  ?

?

上圖給出了兩種不同模式的區(qū)別。由于Simulator涉及到的環(huán)節(jié)非常多,有很多任務(wù)是有依賴關(guān)系的,只能串行開展。如果按照傳統(tǒng)的模式,不僅完成所有任務(wù)的總時(shí)間會(huì)變得很長(zhǎng),它還會(huì)導(dǎo)致最后聯(lián)調(diào)的時(shí)間非常的不確定。因?yàn)楹芏嗄K的耦合性很強(qiáng),很多問題需要等到最后所有模塊放在一起后才能發(fā)現(xiàn)。

基于此,為了降低研發(fā)風(fēng)險(xiǎn),提高開發(fā)效率,GalaxSim的開發(fā)采用了敏捷開發(fā)模式。在敏捷開發(fā)模式下,每個(gè)任務(wù)可以不用一步到位,而是可以先做一個(gè)比較初級(jí)的版本,從v1開始進(jìn)行迭代,直到vN。完成每個(gè)迭代的時(shí)間,是大大短于完成整個(gè)任務(wù)的時(shí)間的。這樣,依賴于該任務(wù)的其他任務(wù)就可以提前開展了。聯(lián)調(diào)階段的不確定也會(huì)大大降低,因?yàn)楹芏鄦栴}都可以在前期階段暴露出來。通過敏捷開發(fā),芯華章的GalaxSim可以更合理地調(diào)配資源,并通過大量迭代,使得產(chǎn)品能達(dá)到商用要求。

3. 技術(shù)路線的選擇:守正、創(chuàng)新

從0到1,開發(fā)一款具備國產(chǎn)自主知識(shí)產(chǎn)權(quán)的仿真器,肯定不能僅僅做一個(gè)me too的產(chǎn)品,需要有創(chuàng)新、超越。我們面臨的問題是,做一個(gè)怎樣的仿真器,能在解決國產(chǎn)替代的基礎(chǔ)上,實(shí)現(xiàn)最終的超越?這里面既要守正,也要?jiǎng)?chuàng)新。

何謂守正?創(chuàng)新的前提首先要先解決有無的問題。上文提到,不管采用什么技術(shù),仿真器都必須滿足四個(gè)指標(biāo):SystemVerilog、精度、性能、可靠性。因此,任何研發(fā)路線與技術(shù)的選擇,都必須滿足以上4個(gè)約束條件。

與此同時(shí),我們吸取主流數(shù)字仿真器的歷史研發(fā)教訓(xùn),針對(duì)國內(nèi)使用環(huán)境進(jìn)行客制化創(chuàng)新。比如在SystemVerilog方面,很多主流仿真器的支持其實(shí)并不是一步到位完成的,而是在一系列并購后集成進(jìn)來的。GalaxSim在這方面,可以發(fā)揮后發(fā)優(yōu)勢(shì),采用全新的設(shè)計(jì)框架,更好實(shí)現(xiàn)SystemVerilog的豐富語法,讓整個(gè)compile flow無縫對(duì)接,避免不斷“打補(bǔ)丁”帶來的技術(shù)冗余與滯澀,提供更完整、一體化的驗(yàn)證解決方案。

以性能為例,runtime是仿真器的一項(xiàng)重要技術(shù)指標(biāo)。大多數(shù)國際主流仿真器在過去數(shù)十年都做了大量的工作。然而,compile time 也是性能的一部分。近5-10年,隨著設(shè)計(jì)規(guī)模越來越大,compile time 也日益成為性能瓶頸。而且,compile time 和 run time常常是矛盾的。GalaxSim使用創(chuàng)新底層架構(gòu),在提高runtime性能的同時(shí),兼顧了compile time的控制。

4. “蝶變”:GalaxSim的迭代歷程

敏捷開發(fā)意味著快速的軟件迭代。GalaxSim 的迭代歷程,比較類似于一個(gè)胚胎的成長(zhǎng)過程。胚胎每一步的變化并不大(比如細(xì)胞分裂),然而,經(jīng)過足夠的變化,最終就會(huì)由量變到質(zhì)變,就像蝶變一樣。

如何確保GalaxSim的迭代是按照我們?cè)O(shè)計(jì)的方向,而不會(huì)走偏呢?這里面,軟件的迭代又非常像生物的進(jìn)化,我們需要設(shè)計(jì)好一個(gè)目標(biāo)(生存條件),以及一個(gè)進(jìn)化環(huán)境。根據(jù)前文所述,GalaxSim從0到1的第一階段目標(biāo),是要演變成一個(gè)至少滿足4個(gè)約束條件的仿真器。

4.1

以終為始,設(shè)計(jì)迭代目標(biāo)

第一階段我們會(huì)以終為始,根據(jù)上文提到的四點(diǎn)對(duì)仿真器的硬性要求,分別制定多維度可量化的迭代目標(biāo),通過不斷的調(diào)試達(dá)成各項(xiàng)指標(biāo)。

4.2

進(jìn)化環(huán)境的搭建

如何確保軟件向著我們?cè)O(shè)置的目標(biāo)進(jìn)化,而不是走偏,進(jìn)化環(huán)境至關(guān)重要。芯華章的研發(fā)團(tuán)隊(duì)為此專門搭建了一套內(nèi)部CICD flow, 包含了回歸測(cè)試系統(tǒng),這個(gè)系統(tǒng)包含了大量的測(cè)試用例,各種測(cè)試基準(zhǔn)(benchmark)。GalaxSim在這些用例中的表現(xiàn)結(jié)果會(huì)被實(shí)時(shí)監(jiān)控。尤其是性能方面,我們的系統(tǒng)引入了類似銀行的記賬功能。每個(gè)研發(fā)環(huán)節(jié)導(dǎo)致的slowdown都會(huì)被記錄備案,每一筆帳都可以追溯。這些嚴(yán)苛的環(huán)境,確保了軟件最終的性能及質(zhì)量。

值得一提的是,這套系統(tǒng)是我們?cè)诘谝惶炀烷_始著手搭建的,與GalaxSim的核心代碼是同步開發(fā)的。

4.3

Galaxsim的主要迭代節(jié)點(diǎn):

? ? ? ? ? ? ? ? ? ? ? ? ?

? ? ? ? ? ? ? ? ? ? ? ? ?

5. 現(xiàn)狀:已獲得一線項(xiàng)目部署

目前GalaxSim已經(jīng)在中科院半導(dǎo)體所、芯來科技等若干客戶的一線項(xiàng)目中得到應(yīng)用,性能符合客戶預(yù)期。

6. 總結(jié)

在未來,GalaxSim的進(jìn)化還會(huì)繼續(xù),并擁抱更多的創(chuàng)新,最終實(shí)現(xiàn)國產(chǎn)數(shù)字仿真器的超越。

接下來,我們將結(jié)合GalaxSim的具體性能表現(xiàn)、技術(shù)指標(biāo)以及對(duì)數(shù)字仿真器主流技術(shù)趨勢(shì)的分析,繼續(xù)探討一款高性能、高精度的數(shù)字仿真器應(yīng)該具備哪些技術(shù)特征。后續(xù)系列文章請(qǐng)大家關(guān)注、指導(dǎo)。

審核編輯:劉清

-

EDA工具

+關(guān)注

關(guān)注

4文章

267瀏覽量

31789 -

仿真器

+關(guān)注

關(guān)注

14文章

1017瀏覽量

83727 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110078 -

SPICE

+關(guān)注

關(guān)注

6文章

182瀏覽量

42563

原文標(biāo)題:解碼國產(chǎn)EDA數(shù)字仿真器系列之一 | 從零到一 如何構(gòu)建一款先進(jìn)的數(shù)字仿真器

文章出處:【微信號(hào):Rocker-IC,微信公眾號(hào):路科驗(yàn)證】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TI磁感應(yīng)仿真器功能簡(jiǎn)介

隔離認(rèn)證標(biāo)準(zhǔn)揭秘:光耦合器與光耦仿真器

如何構(gòu)建一款先進(jìn)的數(shù)字仿真器?

如何構(gòu)建一款先進(jìn)的數(shù)字仿真器?

評(píng)論