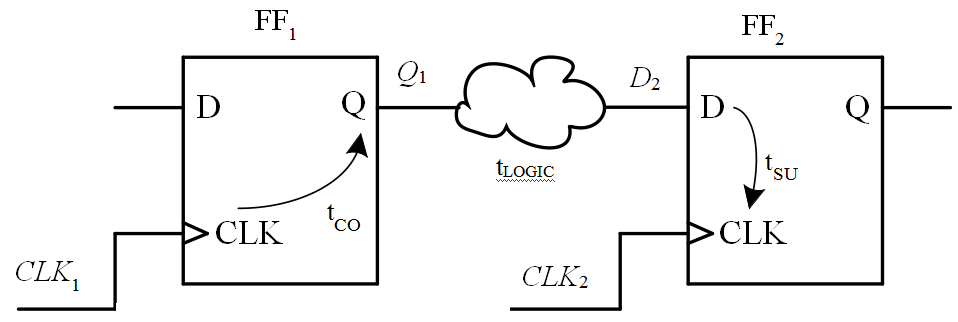

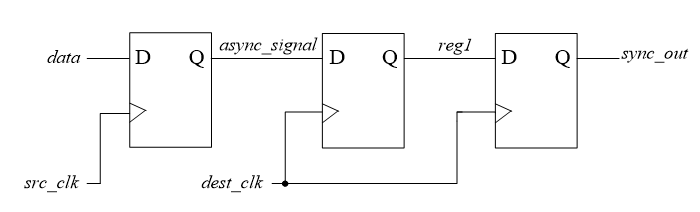

在基于FPGA的數(shù)字系統(tǒng)設計中,異步時序是指時序邏輯電路內部寄存器的時鐘來自兩個及以上的時鐘源,如圖1所示,而且時鐘源之間沒有確定的相位關系。 相應地,把信號從寄存器FF1傳輸?shù)郊拇嫫?FF2,稱為跨時鐘域傳輸 (Clock Domain Crossing,CDC),其中FF1稱為源寄存器,F(xiàn)F2稱為目的寄存器 。

圖1 異步時序電路示例

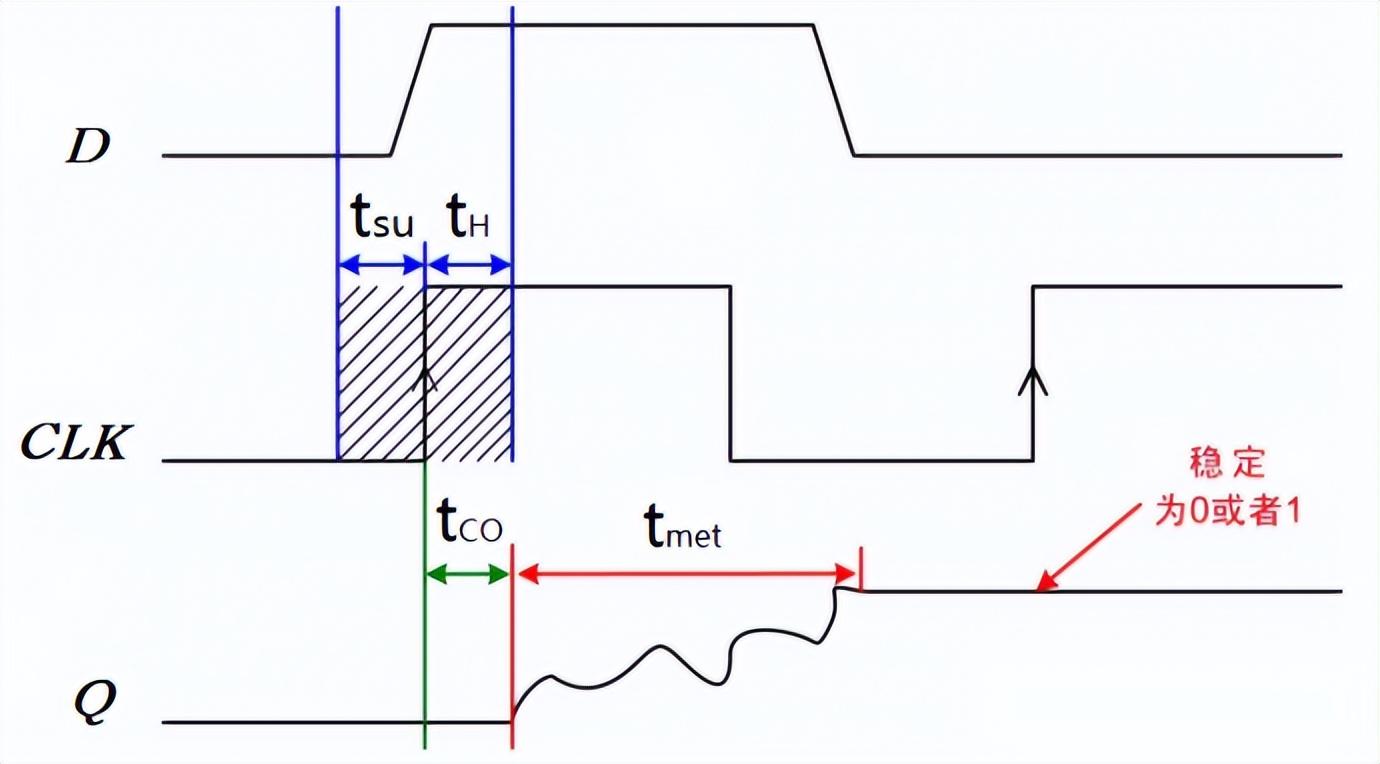

信號在跨時鐘域傳輸時,由于源寄存器的時鐘和目的寄存器的時鐘之間相位沒有確定的相位關系,所以數(shù)據(jù)從源寄存器FF1發(fā)出后,有可能在任何時刻到達目的寄存器,因此無法保證能夠滿足目的寄存器FF2的建立時間和保持時間要求。 如果信號不能在目的寄存器的建立時間和保持時間定義的窗口內保持穩(wěn)定,那么目的寄存器的輸出有可能進入 非0非1 (介于VOHmin和VOLmax之間)的不確定狀態(tài),如圖2所示,這個狀態(tài)稱為亞穩(wěn)態(tài) (metastability)。 相應的,把目的寄存器脫離亞穩(wěn)態(tài)進入穩(wěn)態(tài)的時間稱為決斷時間 (resolution time),用tmet表示。 經過決斷時間后,目的寄存器的輸出最終穩(wěn)定到0還是1是隨機的,與輸入信號沒有必然的關系。

圖2 時序違規(guī)導致亞穩(wěn)態(tài)

處于亞穩(wěn)態(tài)的寄存器在決斷時間前輸出電壓在高電平與低電平之間振蕩時,可能會導致后續(xù)的數(shù)字部件作出不同的判斷,可能判斷為0、可能判斷為1,也可能進入亞穩(wěn)態(tài),從而引發(fā)數(shù)字系統(tǒng)產生錯誤。

除了信號的跨時鐘域傳輸外,異步時序還有另外兩種情況。

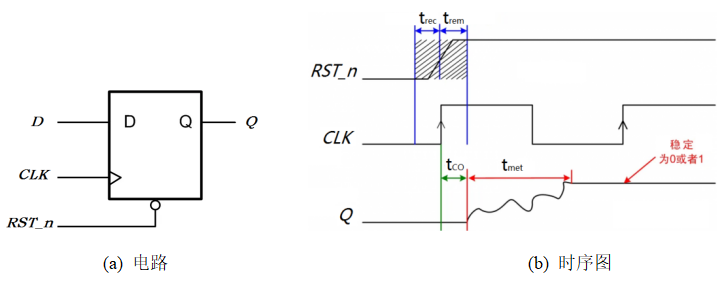

第一種情況是系統(tǒng)復位時,無論是異步復位還是同步復位。

對于異步復位來說,復位信號如果不能在觸發(fā)器的恢復時間和撤除時間窗口內保持穩(wěn)定,如圖3所示,那么就可能影響觸發(fā)器輸入數(shù)據(jù)的鎖存過程而產生亞穩(wěn)態(tài)。 觸發(fā)器的輸出在Tco后可能會進入亞穩(wěn)態(tài),最終可能穩(wěn)定到0,也可能穩(wěn)定到1,從而導致系統(tǒng)發(fā)生錯誤。

圖3 異步復位電路及時序圖

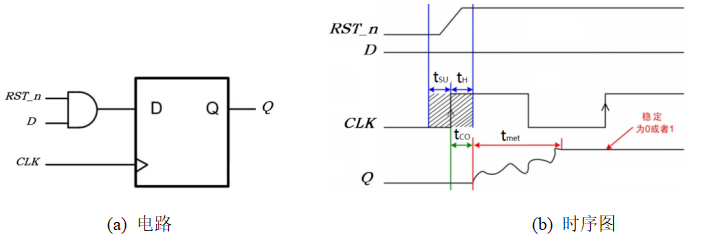

對于同步復位來說,當輸入信號D為高電平時,如果復位信號不能在觸發(fā)器的建立時間和保持時間定義的窗口內保持穩(wěn)定,如圖4所示,同樣可能產生亞穩(wěn)態(tài)。

圖4 同步復位電路及時序圖

第二種情況是系統(tǒng)對外部信號的采集。

對于按鍵和外部中斷等輸入信號,由于信號的作用時間不受系統(tǒng)時鐘的控制,因此在采集過程中,外部信號可能在任何時刻發(fā)生變化,所以也無法保證滿足寄存器建立時間和保持時間的要求。

綜上分析,亞穩(wěn)態(tài)產生的原因是 :觸發(fā)器的輸入信號變化不滿足寄存器建立時間和保持時間的要求,或者復位信號不滿足觸發(fā)器恢復時間和撤除時間的要求。

亞穩(wěn)態(tài)是觸發(fā)器固有的特性。 在基于FPGA的數(shù)字系統(tǒng)設計中,主要應用三種方法減小亞穩(wěn)態(tài)傳播的概率 :①引入同步器來減小單bit信號亞穩(wěn)態(tài)傳播的概率,實現(xiàn)異步信號與目的時鐘域的同步; ②應用異步FIFO實現(xiàn)多bit數(shù)據(jù)的跨時域傳輸; ③應用異步復位同步釋放信號改善純異步復位信號的特性,提高系統(tǒng)復位的可靠性。

下面分別講述這三種方法。

01單bit信號的跨時鐘域同步

單bit信號跨時鐘傳輸產生亞穩(wěn)態(tài)的原因是因為信號與目的時鐘不同步,導致信號不能滿足目的寄存器建立時間和保持時間的要求,從而導致寄存器不能輸出正確的邏輯值。

亞穩(wěn)態(tài)傳播的概率與采集延遲時間之間近似為指數(shù)關系。 延遲時間越長,亞穩(wěn)態(tài)傳播的概率越小。 對于單bit信號的采集,減小亞穩(wěn)態(tài)發(fā)生概率最簡單的方法是應用由移位寄存器構成的 兩級同步器(double-flop synchronizer)來延長信號的采集時間,如圖5所示。 其中同步器輸入的異步信號為 async_signal ,第一級完成觸發(fā)器的輸出為 reg1 ,第二級觸發(fā)器的輸出為同步信號 sync_out 。

圖5 兩級同步器

同步器在第一個時鐘脈沖作用后,第一級觸發(fā)器的輸出reg1可能會產生亞穩(wěn)態(tài),但是reg1有機會在被第二級觸發(fā)器鎖存之前穩(wěn)定下來,所以在第二個時鐘脈沖作用后,輸出的同步信號sync_out能夠保持穩(wěn)定。

需要注意的是,組合邏輯電路的輸出不能直接應用同步器進行同步。 這是因為組合電路的輸出可能存在競爭-冒險現(xiàn)象,會增加同步器中第一級觸發(fā)器產生亞穩(wěn)態(tài)的概率,從而影響同步器輸出信號的可靠性。 所以,在跨時鐘域同步之前,還需要在源時鐘域先將組合電路的輸出信號鎖存后輸出,如圖5中所示,然后再進行同步。

圖5所示的同步器適合于將慢時鐘域的單bit信號同步到快時鐘域,要求異步信號async_signal的脈沖寬度至少應維持一個同步器的時鐘周期,才能保證信號在目的時鐘域被采集到,輸出同步信號sync_out的寬度取決于信號在目的時鐘域被采集到的次數(shù)。

同步器的級數(shù)以2~3級為宜。 因為級數(shù)越多,將導致異步信號同步到目的時鐘域的延遲時間越長,因此對異步信號的變化反應越慢。 對于只關心信號邊沿跳變的應用場合,還可以應用同步器提取脈沖的邊沿。 描述信號邊沿檢測電路的Verilog HDL代碼參考如下:

module edge_detector (

input det_clk, // 時鐘,50MHz

input rst_n, // 復位信號,低電平有效

input x_signal, // 被測信號

output wire rising_edge, // 上升沿標志,高電平有效

output wire fall_edge // 下降沿標志,高電平有效

);

// 3級同步寄存器定義

reg [0:2] sync_reg;

// 同步移存過程

always @( posedge det_clk or negedge rst_n )

if ( !rst_n )

sync_reg <= 3'b000;

else

sync_reg[0:2] <= { x_signal, sync_reg[0:1] };

// 邊沿檢測邏輯

assign rising_edge = sync_reg[1] & ~sync_reg[2];

assign fall_edge = ~sync_reg[1] & sync_reg[2];

endmodule

02多bit數(shù)據(jù)的跨時鐘域傳輸

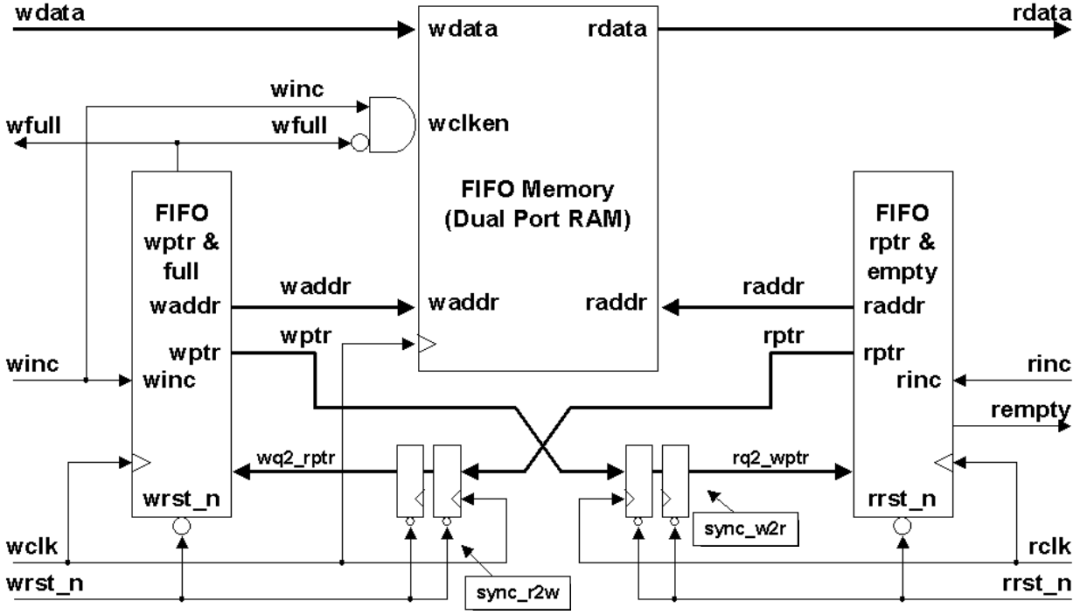

對于多bit數(shù)據(jù),普遍的方法是應用圖6所示的異步FIFO實現(xiàn)跨時域傳輸。

圖6 跨時域異步FIFO結構

應用異步FIFO最關鍵的問題是如何判斷FIFO的狀態(tài),產生空/滿標志。 因為異步FIFO的讀/寫操作在不同的時鐘域,所以無法像同步FIFO那樣,通過統(tǒng)計存儲數(shù)據(jù)的個數(shù)來產生empty和full標志。

1)異步FIFO空/滿的檢測方法

FIFO為空有兩種情況:①FIFO復位時; ②當讀指針rp追上了寫指針wp,讀/寫指針相同時。 FIFO已滿只有一種情況:當寫指針wp多走了一圈, 折回來(wrapped around)追上了讀指針rp,讀/寫指針再次相同時。

綜上所述,F(xiàn)IFO為空和已滿時讀/寫指針都相同。 為了區(qū)分指針相同時FIFO為空還是已滿,需要在FIFO的讀/寫指針前再多加一個標志位來區(qū)分寫指針是否比讀指針多寫了一圈。 所以,對于存儲深度為2^n的異步FIFO,讀/寫指針應定義為n+1位 (標志位+n位地址),即對于深度為8的異步FIFO,需要定義4位地址指針,取值為0000~0111和1000~1111,其中最高位為折回標志,低3位為地址值。

添加了標志位后,每當讀/寫指針遞加并越過FIFO的最后一個存儲單元后,將讀/寫指針的最高位翻轉,其余位回零。 因此,判斷異步FIFO空/滿的方法是:當讀/寫指針的所有位均相同時,說明FIFO為空; 當讀/寫地址的最高位不同而其余均相同時,說明寫指針比讀指針多走了一圈,說明FIFO已滿。

2)讀/寫指針的同步方法

由于異步FIFO的讀/寫在不同的時鐘域,所以還需要將讀/寫指針同步到另一個時鐘域與寫/讀指針進行比較才能產生空/滿標志。 但是,二進制讀/寫指針不能直接同步到另一個時鐘域。 這是因為,當n+1位二進制讀/寫地址有多位同時發(fā)生變化(如地址從0111變化到1000)時,如果直接應用同步器進行同步,則可能會因不同數(shù)位亞穩(wěn)態(tài)決斷時間的差異而導致同步后的指針值產生中間值而造成同步后的地址發(fā)生錯誤。

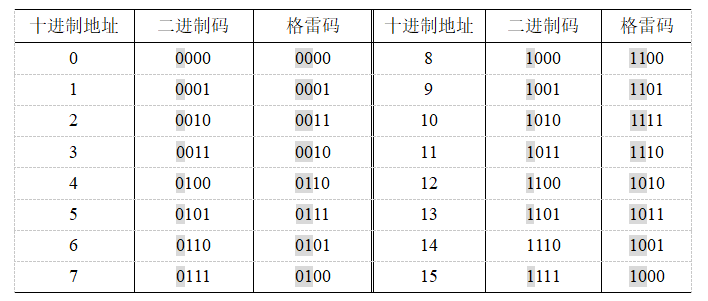

為了解決這一問題, 一般的處理方法是,先將二進制讀/寫指針值轉換為格雷碼后再進行同步。 因為格雷碼的相鄰碼之間只有一位發(fā)生變化,其余位不變,如表1所示,而不像二進制地址那樣,存在多位同時發(fā)生變化的情況。 由于FIFO的讀/寫通過地址加1實現(xiàn)的,因而應用格雷碼能夠有效地避免同步后的指針產生中間值而造成地址錯誤。

表1 4位格雷碼與二進制碼比較表

將讀/寫地址轉換為格雷碼后,能不能直接應用同步后的格雷碼產生空/滿標志呢? 下面再進行分析。

深度為2^n的異步FIFO共有n+1位讀/寫指針。 設格雷碼寫指針用 wptr[n:0] 表示,讀指針用 rptr[n:0]表示,F(xiàn)IFO為空用rempty表示,為滿用wfull表示。

判斷FIFO是否為空比較簡單: 當讀/寫指針值完全相同時,無論用二進制指針還是用格雷碼指針 。 因此,空標志產生的Verilog代碼為

empty = ( rptr == wptr );

FIFO為滿時二進制讀/寫指針的最高位不同而其余位相同。 從表1中的二進制碼和格雷碼的對應關系可以看出,F(xiàn)IFO為滿時格雷碼指針的最高位和次高位不同,其余位相同。 因此,基于格雷碼判斷FIFO已滿的Verilog代碼為

wfull = ( wptr[n:n-1] == ~rptr[n:n-1])&&( wptr[n-2:0] == rptr[n-2:0]);

3)跨時鐘域異步FIFO的工作原理

對于圖6所示的跨時鐘域異步FIFO,在 寫時鐘域(wclk)收到寫指令 (write instruction,簡寫為winc)時,需要根據(jù)wfull標志判斷FIFO是否已滿,因為FIFO已滿時不能再寫。 在FIFO不滿的情況下,使寫允許信號wclken有效,將數(shù)據(jù)wdata寫入FIFO后寫地址(waddr)加1,同時將格雷碼寫指針(wptr)同步到讀時鐘域與格雷碼讀指針(rptr)進行比較,產生rempty標志 。 在讀時鐘域(rclk)收到讀指令(read instruction,簡寫為rinc)時,需要根據(jù)rempty標志判斷FIFO是否為空,因為FIFO為空時不能再讀。 在FIFO非空的情況下,讀出數(shù)據(jù)rdata后讀地址 (raddr)加1,同時將格雷碼讀指針(rptr)同步到寫時鐘域與格雷碼寫指針(wptr)進行比較,產生wfull標志 。

需要注意的是,由于異步FIFO通過比較讀/寫指針產生空/滿標志,而讀/寫指針屬于不同的時鐘域,所以在比較時需要將讀/寫指針經過兩級同步器同步到另一個時鐘域,因此產生的滿/空標志會延遲兩個時鐘周期。 如果在同步時間內有新的數(shù)據(jù)寫入,則同步后的寫指針一定小于當前實際的寫地址,所以判斷FIFO為空時實際上不一定為空,因此不會出現(xiàn)讀空的情況。 同樣的道理,如果在同步時間內有數(shù)據(jù)讀出,則同步后的讀指針一定小于當前的讀指針,所以判斷FIFO已滿時不一定真滿,因此不會出現(xiàn)寫滿的情況。 因此,異步FIFO空/滿標志的延遲會導致空/滿的判斷更趨于保守,雖然會影響FIFO性能,但是不會出錯。

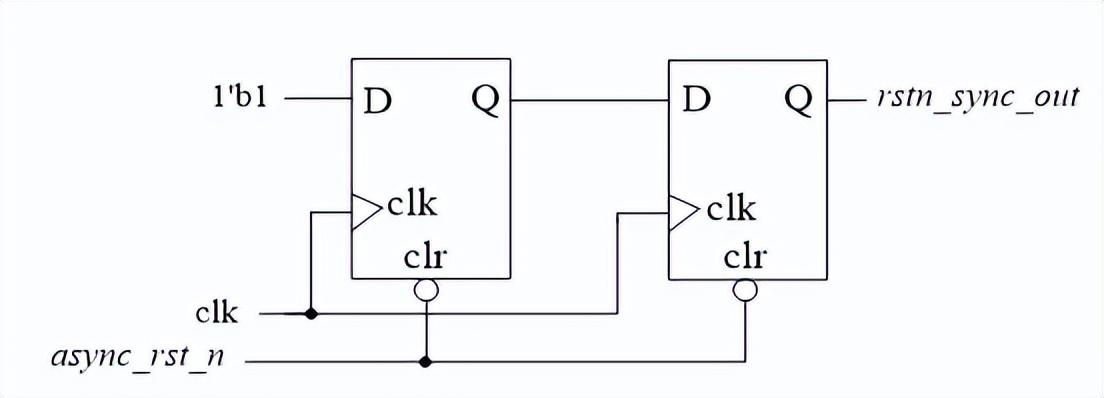

03應用同步釋放電路改善異步復位信號的特性

異步復位信號不受時鐘的控制,具有直接快速的優(yōu)點。 但是,當異步復位信號的釋放時間不滿足觸發(fā)器的恢復時間和撤除時間要求時,有可能產生亞穩(wěn)態(tài)。 改進方法是應用異步復位信號對系統(tǒng)內部所有的寄存器復位后,釋放時再經過時鐘脈沖進行同步。 這樣做的好處是既能夠應用異步復位信號對系統(tǒng)進行快速復位,又避免了異步復位信號直接釋放時帶來的亞穩(wěn)態(tài)風險。

異步復位信號的同步釋放電路原理如圖7所示。 當異步復位信號async_rst_n有效時,能夠直接將兩個觸發(fā)器復位,因此第二個觸發(fā)器的輸出rstn_sync_out=0 ,當復位信號async_rst_n釋放后,兩個觸發(fā)器的復位信號轉為無效,第一個觸發(fā)器輸入的高電平經過兩個時鐘脈沖后才能使rstn_sync_out=1,因此第二個觸發(fā)器的輸出rstn_sync_ out具有異步復位同步釋放特性。 因此,應用rstn_sync_out作為系統(tǒng)的全局復位信號時,既能夠對系統(tǒng)中的所有寄存器直接復位,又能夠避免了復位信號直接釋放時帶來的亞穩(wěn)態(tài)風險。

圖7 異步復位信號同步釋放原理電路

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603048 -

寄存器

+關注

關注

31文章

5336瀏覽量

120257 -

觸發(fā)器

+關注

關注

14文章

2000瀏覽量

61134 -

亞穩(wěn)態(tài)

+關注

關注

0文章

46瀏覽量

13272 -

異步時序

+關注

關注

0文章

6瀏覽量

8637

發(fā)布評論請先 登錄

相關推薦

利用IDDR簡化亞穩(wěn)態(tài)方案

FPGA中亞穩(wěn)態(tài)——讓你無處可逃

簡談FPGA學習中亞穩(wěn)態(tài)現(xiàn)象

在FPGA復位電路中產生亞穩(wěn)態(tài)的原因

探尋FPGA中三種跨時鐘域處理方法

FPGA--中復位電路產生亞穩(wěn)態(tài)的原因

今日說“法”:讓FPGA設計中的亞穩(wěn)態(tài)“無處可逃”

FPGA系統(tǒng)中三種方式減少亞穩(wěn)態(tài)的產生

簡述FPGA中亞穩(wěn)態(tài)的產生機理及其消除方法

亞穩(wěn)態(tài)產生原因、危害及消除方法

什么是亞穩(wěn)態(tài)?如何克服亞穩(wěn)態(tài)?

FPGA系統(tǒng)中三種方式減少亞穩(wěn)態(tài)的產生

pwm產生的三種方法

FPGA設計中的亞穩(wěn)態(tài)解析

FPGA系統(tǒng)中三種方法減少亞穩(wěn)態(tài)的產生

FPGA系統(tǒng)中三種方法減少亞穩(wěn)態(tài)的產生

評論