上一篇文章提到了DLL的諧波問題,解決該問題的有效措施是對Vcont進行復位上拉。

01 DLL的一種應用場景:面對諧波鎖定的風險

本篇文章是對DLL的諧波鎖定問題做進一步的探討。我們考慮下面這樣一種應用情景:一款帶Vcont復位上拉的DLL電路,在復位結束之后,參考時鐘在很長一段時間之后才到來。請問,這時候該DLL有沒有可能發生諧波鎖定問題?

答案是有可能。在復位結束之后,Vcont雖然為VDD,如果這時候DLL還沒有參考時鐘輸入,Vcont將很難保持VDD大小的電壓,這是因為即使電荷泵的上下通路為高阻抗,還是會存在一定的電荷泄露,隨著時間的加長,Vcont電壓會逐漸減小。此外,沒有參考時鐘輸入,UP和DN的狀態并不確定,Vcont的初值還面對著可能被放電路徑釋放的風險(如果DN剛好有效)。這種情況下,假設參考時鐘在很長一段時間后才來到,那么此時的Vcont已經降低到0~VDD之間的某個中間值,且該值在不同工藝角、溫度、供電下是不同的,且難以預測,因此仍然有可能出現諧波鎖定現象(詳細原因可以看參考帖)。

這就像是,雖然我們增加了Vcont賦初值的預防措施,但仍然會有一些特殊的場景使初值存在的作用失效。

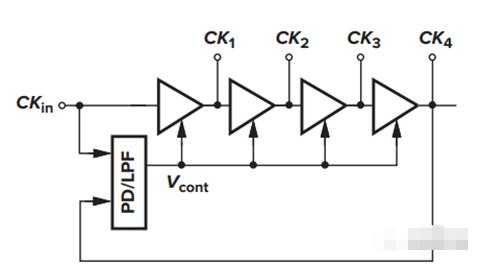

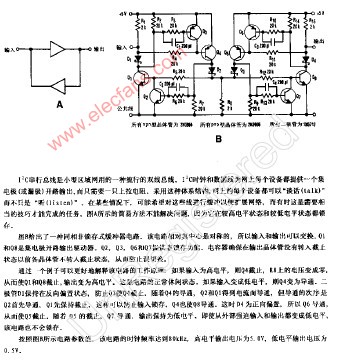

圖1 DLL典型結構

02 VCDL時鐘檢測電路解決問題

我們思考一下,上述問題的關鍵是在參考時鐘到來之前Vcont的電壓漂移問題。因此在參考時鐘給到之前,我們只要保證Vcont即使在復位釋放之后仍然能保持在VDD大小,那么該問題就得到了解決。基于這個思路,下圖所示的電路在工程實踐上得到了廣泛的應用。

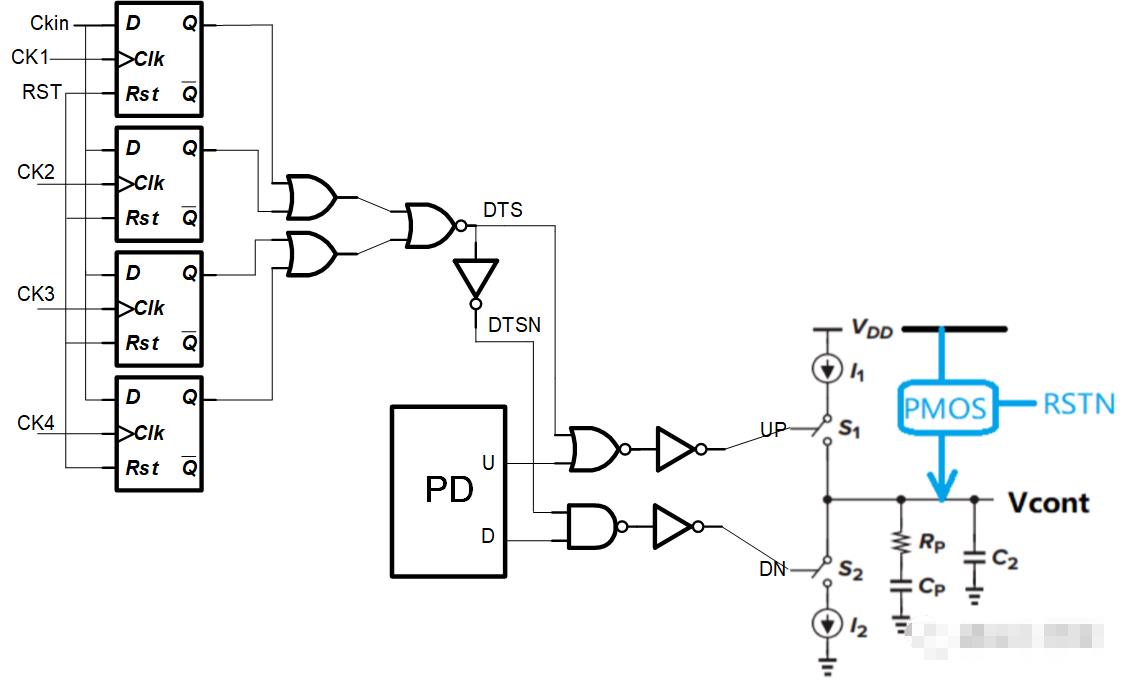

圖2 增加時鐘檢測電路后的電路

該電路利用多個DFF設計了一個VCDL時鐘檢測電路,CKin連接到DFF的數據端,從上到下每個DFF的時鐘端從VCDL引出,且每個DFF被同步復位。在沒有參考時鐘時,VCDL也無法輸出時鐘。在復位期間,RST=1,一方面,RSTN=0,Vcont被上拉到VDD;另一方面,時鐘檢測電路中,所有DFF被復位,Q=0,DTS=1,DTSN=0,此時S1=1,S2=0,充電電流源打開,放電電流源關閉,Vcont的電位被進一步加強,使其保持VDD大小。

我們再回顧一下前文提到的應用場景,再看看這時候DLL會如何反應:當復位釋放之后,假設CKin仍然沒有到來,所有的DFF的時鐘端不會出現邊沿跳變,作為邊沿觸發型的DFF,其Q端維持之前的值,因此DTS仍等于1,所以S1仍然打開,S2仍然關閉,Vcont端被充電,其始終維持VDD電位不變。當CKin一旦到來,CK1~CK4自然會有時鐘輸出,DFF會有采樣輸出,只要有一路Q=1,DTS就跳變為0,關閉對PD輸出狀態的控制。此后,Loop將在負反饋作用下進入鎖相過程。

總結:

和前一篇帖子的核心點一致:保證Vcont賦初值。本篇針對一種特殊的、但并不是不常見的應用場景進行了分析,指出了該場景下DLL面對的諧波鎖定風險,并給出了解決方案。解決的辦法需要增加額外的電路,即VCDL時鐘檢測電路。

-

檢測電路

+關注

關注

13文章

312瀏覽量

58999 -

dll

+關注

關注

0文章

116瀏覽量

46238 -

諧波

+關注

關注

7文章

877瀏覽量

42865 -

時鐘

+關注

關注

11文章

1903瀏覽量

133371 -

VDD

+關注

關注

1文章

316瀏覽量

35434

發布評論請先 登錄

三級放大電路噪音問題(解決問題可發紅包)急!!

基于SOC的血沉儀時鐘及溫度檢測系統

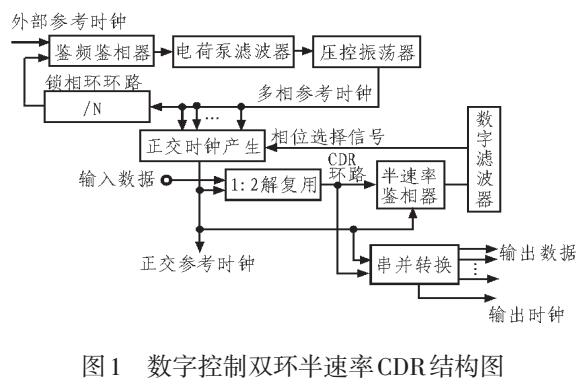

基于高速CMOS時鐘的數據恢復電路設計與仿真

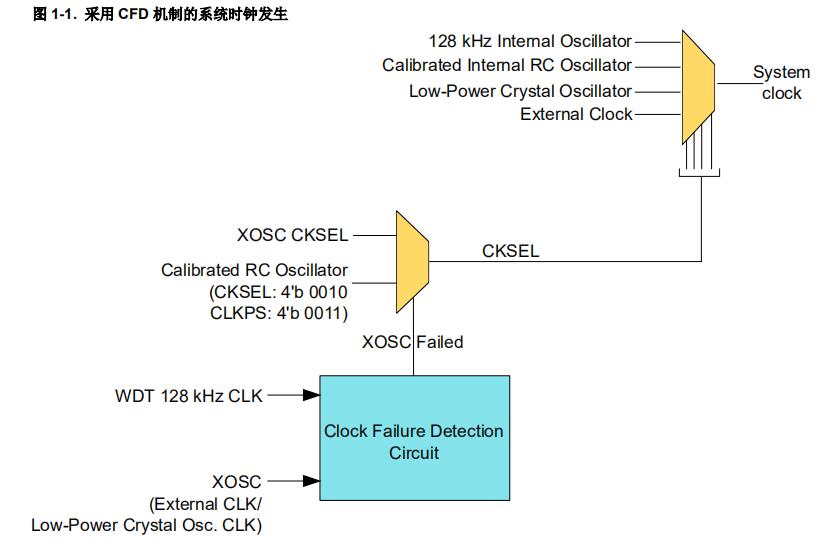

使用ATmega328PB的時鐘故障檢測

評論