D 觸發器

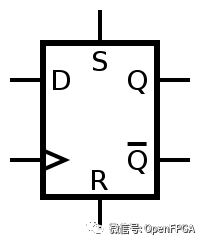

D 觸發器符號D觸發器被廣泛使用。它也被稱為“data”或“delay”觸發器。

D 觸發器在時鐘周期的特定部分(例如時鐘的上升沿)捕獲 D 輸入的值。捕獲的值成為 Q 輸出。在其他時候,輸出 Q 不會改變。D觸發器可以看作是一個存儲單元、一個零階保持器或一條延遲線。

D 觸發器真值表

(X表示無關條件,表示信號無關)

IC 中的大多數 D 型觸發器都具有強制 set 或者 reset狀態(忽略 D 和時鐘輸入)的能力,就像 SR 觸發器一樣。通常,非法 S = R = 1 條件在 D 型觸發器中得到解決。設置 S = R = 0 使觸發器的行為如上所述。以下是其他可能的 S 和 R 配置的真值表:

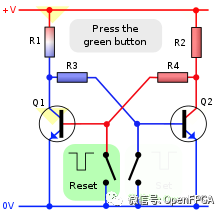

4 位串行輸入并行輸出 (SIPO) 移位寄存器這些觸發器非常有用,因為它們構成了移位寄存器的基礎,而移位寄存器是許多電子設備的重要組成部分。D觸發器相對于D型“透明鎖存器”的優勢在于D輸入引腳上的信號在觸發器被計時的那一刻被捕獲,并且D輸入上的后續變化將被忽略,直到下一個時鐘事件。一個例外是一些觸發器有一個“復位”信號輸入,它會將 Q 復位(為零),并且可能與時鐘異步或同步。

上述電路將寄存器的內容向右移動,在時鐘的每個有效轉換上移動一位。輸入 X 被移到最左邊的位位置。

經典的正邊沿觸發 D 觸發器

幾種不同類型的邊沿觸發 D 觸發器

一個上升沿觸發的 D 觸發器

一個上升沿觸發的 D 觸發器## 主從邊沿觸發 D 觸發器

主從 D 觸發器。它在使能輸入的下降沿響應(通常是時鐘)

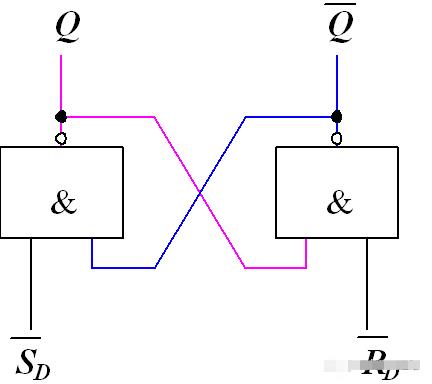

在時鐘上升沿觸發的主從 D 觸發器的實現通過串聯兩個門控 D 鎖存器并將使能輸入反相到其中一個來創建主從 D 觸發器。之所以稱為主從鎖存器,是因為主鎖存器控制從鎖存器的輸出值 Q 并在從鎖存器啟用時強制從鎖存器保持其值,因為從鎖存器總是從主鎖存器復制其新值并更改其值僅響應主鎖存器和時鐘信號值的變化。

對于上升沿觸發的主從 D 觸發器,當時鐘信號為低電平(邏輯 0)時,第一個或“主”D 鎖存器(反相時鐘信號)看到的“使能”為高電平(邏輯 1) . 這允許“主”鎖存器在時鐘信號從低電平轉換為高電平時存儲輸入值。隨著時鐘信號變高(0 到 1),第一個鎖存器的反相“啟用”變低(1 到 0),并且在主鎖存器的輸入處看到的值被“鎖定”。幾乎同時,第二個或“從”D 鎖存器的兩次反相“啟用”隨著時鐘信號從低電平變為高電平(0 到 1)。這允許現在“鎖定”的主鎖存器在時鐘上升沿捕獲的信號通過“從屬”鎖存器。

移除電路中最左邊的反相器會創建一個 D 型觸發器,該觸發器在時鐘信號的下降沿觸發。這有一個像這樣的真值表:

雙沿觸發 D 觸發器

雙邊沿觸發 D 觸發器的實現在時鐘的上升沿和下降沿讀入新值的觸發器稱為雙邊沿觸發觸發器。如圖所示,可以使用兩個單邊觸發 D 型觸發器和一個多路復用器來構建這種觸發器。

雙邊沿觸發 D 觸發器的電路符號## 邊沿觸發的動態 D 存儲元件

具有復位功能的動態邊沿觸發觸發器的 CMOS IC 實現只要時鐘足夠頻繁,就可以使用動態電路(其中信息存儲在電容中)來制作 D 觸發器的有效功能替代方案;雖然不是真正的觸發器,但由于其功能作用,它仍然被稱為觸發器。雖然主從 D 元件在時鐘邊沿觸發,但其組件均由時鐘電平觸發。所謂的“邊沿觸發 D 觸發器”,盡管它不是真正的觸發器,但它不具有主從屬性。

邊沿觸發的 D 觸發器通常在使用動態邏輯的集成高速操作中實現。這意味著數字輸出存儲在寄生器件電容上,而器件不轉換。這種動態觸發器的設計還可以實現簡單的復位,因為復位操作可以通過簡單地對一個或多個內部節點進行放電來執行。一種常見的動態觸發器種類是真正的單相時鐘 (TSPC) 類型,它以低功率和高速執行觸發器操作。然而,動態觸發器通常不會在靜態或低時鐘速度下工作:如果有足夠的時間,泄漏路徑可能會使寄生電容放電到足以導致觸發器進入無效狀態的程度。

T 觸發器

T型觸發器的電路符號如果 T 輸入為高電平,則只要時鐘輸入被選通,T 觸發器就會改變狀態(“toggles”) 。如果 T 輸入為低電平,則觸發器保持先前的值。這種行為由特征方程描述:

并且可以用真值表來描述:

T觸發器真值表

當 T 保持高電平時,觸發觸發器將時鐘頻率除以 2;也就是說,如果時鐘頻率為 4 MHz,則從觸發器獲得的輸出頻率將為 2 MHz。這種“除法”功能適用于各種類型的數字計數器。AT 觸發器也可以使用 JK 觸發器(J 和 K 引腳連接在一起并充當 T)或 D 觸發器(T 輸入 XOR Q驅動 D 輸入)構建。

JK 觸發器

正沿觸發 JK 觸發器的電路符號

JK觸發器時序圖JK 觸發器通過將 J = K = 1 條件解釋為“翻轉”或切換命令來增強 SR 觸發器的行為(J: Set, K: Reset)。具體來說,J=1,K=0的組合是設置觸發器的命令;J = 0,K = 1的組合是復位觸發器的命令;J = K = 1 的組合是觸發觸發器的命令,即將其輸出更改為其當前值的邏輯補碼。設置 J = K = 0 保持當前狀態。要合成 D 觸發器,只需設置 K 等于 J 的補碼(輸入 J 將充當輸入 D)。類似地,要合成一個 T 觸發器,設置 K 等于 J。因此 JK 觸發器是通用觸發器,因為它可以配置為 SR 觸發器、D 觸發器或T觸發器。

JK觸發器的特征方程為:

對應的真值表為:

JK觸發器真值表

時序

時序參數

觸發器設置、保持和時鐘到輸出時序參數輸入必須在時鐘上升沿附近的一段時間內保持穩定,稱為孔徑。想象一下在睡蓮上拍一張青蛙的照片。假設青蛙之后跳入水中。如果你拍青蛙跳入水中的照片,你會看到青蛙跳入水中的模糊照片——不清楚青蛙處于哪種狀態。但如果你在青蛙穩穩地坐著的時候拍照在墊子上(或穩定地在水中),您將獲得清晰的圖像。同樣,觸發器的輸入必須在觸發器的孔徑期間保持穩定。

建立時間是在時鐘事件之前數據輸入應保持穩定的最短時間,以便時鐘可靠地采樣數據。

保持時間是時鐘事件后數據輸入應保持穩定的最短時間,以便時鐘可靠地采樣數據。

孔徑是建立時間和保持時間的總和。在此期間,數據輸入應保持穩定。

恢復時間是在時鐘事件之前異步置位或復位輸入應處于非活動狀態的最短時間,以便時鐘可靠地采樣數據。因此,異步置位或復位輸入的恢復時間類似于數據輸入的建立時間。

移除時間是在時鐘事件之后異步置位或復位輸入應處于非活動狀態的最短時間,以便時鐘可靠地采樣數據。因此,異步置位或復位輸入的移除時間類似于數據輸入的保持時間。

應用于異步輸入(設置、復位)的短脈沖不應在恢復移除期間完全應用,否則將完全無法確定觸發器是否將轉換到適當的狀態。在另一種情況下,異步信號只是在恢復/移除時間之間進行一次轉換,最終觸發器將轉換到適當的狀態,但輸出上可能會或可能不會出現非常短的毛刺,具體取決于在同步輸入信號上。第二種情況可能對電路設計有重要意義,也可能沒有意義。

設置和復位(和其他)信號可以是同步的或異步的,因此可以用建立/保持或恢復/移除時間來表征,并且同步性非常依賴于觸發器的設計。

在驗證較大電路的時序時,通常需要區分建立/保持時間和恢復/移除時間,因為可能會發現異步信號不如同步信號重要。這種差異化使電路設計人員能夠獨立定義這些類型的信號的驗證條件。

亞穩態

觸發器存在稱為亞穩態的問題,當兩個輸入(例如數據和時鐘或時鐘和復位)幾乎同時發生變化時,就會發生這種情況。當順序不明確時,在適當的時序限制內,結果是輸出可能會出現不可預測的行為,需要比正常時間長很多倍的時間才能穩定到一種狀態或另一種狀態,甚至在穩定之前振蕩幾次。理論上,安定下來的時間是沒有限制的。在電腦里系統,如果在另一個電路使用它的值之前狀態不穩定,這種亞穩態會導致數據損壞或程序崩潰;特別是,如果兩條不同的邏輯路徑使用觸發器的輸出,當它尚未解析為穩定狀態時,一條路徑可以將其解釋為 0,而另一條路徑可以將其解釋為 1,從而使機器進入不一致的狀態。

通過確保數據和控制輸入在時鐘脈沖之前和之后的指定時段(分別稱為建立時間(t su ) 和保持時間(th h ))保持有效和恒定,可以避免觸發器中的亞穩態。這些時間在設備的數據表中指定,現代設備通常在幾納秒到幾百皮秒之間。根據觸發器的內部組織,可以構建具有零(甚至負)設置或保持時間要求但不能同時具有兩者的設備。

不幸的是,并不總是能夠滿足建立和保持標準,因為觸發器可能連接到一個實時信號,該信號可能隨時變化,不受設計人員的控制。在這種情況下,設計人員能做的最好的事情就是根據電路所需的可靠性將出錯的概率降低到一定水平。抑制亞穩態的一種技術是將兩個或多個觸發器連接成一個鏈,以便每個觸發器的輸出饋入下一個觸發器的數據輸入,并且所有設備共享一個公共時鐘。使用這種方法,亞穩態事件的概率可以降低到可以忽略不計的值,但絕不會為零。隨著串聯觸發器數量的增加,亞穩態的概率越來越接近于零。級聯的觸發器數量稱為“ranking”;“dual-ranked”觸發器(兩個觸發器串聯)是一種常見的情況。

所謂的metastable-hardened觸發器是可用的,它通過盡可能減少建立和保持時間來工作,但即使這些也不能完全消除問題。這是因為亞穩態不僅僅是電路設計的問題。當時鐘和數據中的轉換在時間上接近時,觸發器被迫決定哪個事件首先發生。無論設備制造得有多快,輸入事件總是有可能靠得太近,以至于無法檢測到哪個事件先發生。因此,從邏輯上講,構建一個完美的亞穩態觸發器是不可能的。觸發器有時以最大穩定時間為特征(它們在指定條件下保持亞穩態的最長時間)。

傳播延遲

觸發器的另一個重要時序值是時鐘到輸出延遲(數據手冊中的常用符號:t_CO)或傳播延遲(t_P ),即觸發器在時鐘邊沿。從高到低的轉換時間(t_PHL)有時與從低到高的轉換時間(t_PLH)不同。

當級聯共享相同時鐘的觸發器時(如在移位寄存器中),重要的是要確保前一個觸發器的 t_CO長于后一個觸發器的保持時間 (t_h ),因此,出現在后續觸發器輸入端的數據會在時鐘的有效沿之后正確“移入”。如果觸發器物理上相同,則通常可以保證t_CO和 t_h之間的這種關系。此外,為了正確操作,很容易驗證時鐘周期必須大于總和 t_su + t_h。

總結

觸發器至少可以通過兩種方式進行概括:使它們成為 1-of-N 而不是 1-of-2,以及使它們適應具有兩個以上狀態的邏輯。在 1-of-3 編碼或多值三進制邏輯的特殊情況下,這種元件可以稱為觸發器。

在傳統的觸發器中,恰好兩個互補輸出中的一個為高電平。這可以推廣到具有 N 個輸出的存儲元件,其中恰好一個為高(或者,恰好其中一個為低)。因此,輸出始終是one-hot(分別是 one-cold)表示。結構類似于傳統的交叉耦合觸發器;每個輸出,當高,抑制所有其他輸出。或者,可以使用或多或少的傳統觸發器,每個輸出一個,并帶有額外的電路,以確保一次只有一個是真實的。

傳統觸發器的另一種概括是用于多值邏輯的存儲元件。在這種情況下,存儲元件恰好保留其中一種邏輯狀態,直到控制輸入引起變化。此外,還可以使用多值時鐘,從而產生新的可能的時鐘轉換。

-

存儲

+關注

關注

13文章

4326瀏覽量

85939 -

脈沖

+關注

關注

20文章

892瀏覽量

95668 -

鎖存器

+關注

關注

8文章

906瀏覽量

41550 -

觸發器

+關注

關注

14文章

2000瀏覽量

61212

發布評論請先 登錄

相關推薦

恒壓變壓器的發展史

5G的發展史

unix系統發展史

觸發器發展史及類型(上)

觸發器發展史及類型(下)

觸發器發展史及類型(下)

評論