1.LDO基本原理

LDO是Low Dropout Regulator的縮寫,意思是低壓差線性穩(wěn)壓器。

低壓差 是指輸入電壓-輸出電壓的值比較低。傳統(tǒng)的線性穩(wěn)壓器壓差高達2V,而LDO的壓差只有幾百mV。

線性 是指PMOS基本處于線性工作狀態(tài)(傳統(tǒng)的線性穩(wěn)壓器是PNP原理,也工作在線性放大狀態(tài))。

穩(wěn)壓器 是指在正常的VIN范圍內(nèi),輸出VOUT都穩(wěn)定在一個固定值,這個固定值就是我們想要的電壓值。比如VIN是電池電壓3~4.4V,VOUT始終保持2.7V輸出。

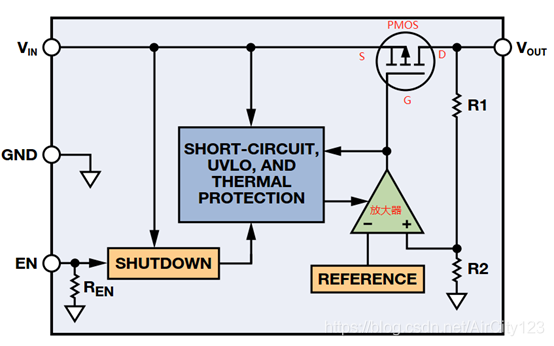

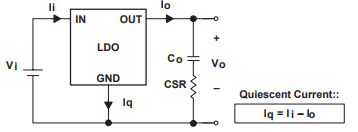

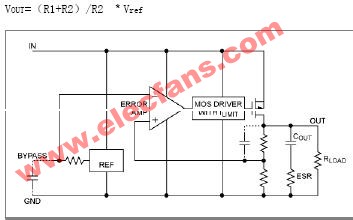

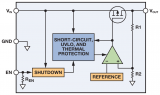

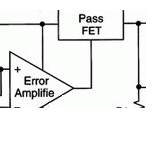

下圖是一個簡單的LDO原理框圖:

LDO是一個負反饋系統(tǒng),當VOUT增大,R2上電壓增大,放大器輸出電壓增大,PMOS的VGS電壓減小,這樣PMOS輸出電流減小,電壓也減小。所有的LDO都是同樣的負反饋原理。

我們經(jīng)常拿LDO與DCDC做對比,兩者的原理差別很大,特性也不一樣:LDO簡單,功率小,效率低,噪聲非常低。DCDC復雜,功率大,效率高,噪聲也很高。

重點說明一下,LDO有非常好的噪聲隔離作用,具體指標是PSRR,它表示輸出噪聲對輸入噪聲的比值。在一些對噪聲敏感的電路中,如ADC,DAC,Camera sensor模擬電壓等,必須選擇LDO,而且是高PSRR的LDO,而不是DCDC。下文解釋一些LDO的關(guān)鍵技術(shù)指標。

2.LDO關(guān)鍵參數(shù)的理解

以TOSHIBA的TCR3DG系列LDO為例,解釋一下LOD的各項參數(shù)指標。這個系列的LDO在手機行業(yè)應(yīng)用非常多。

2.1壓差(Drop-out Voltage)

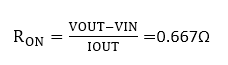

壓差是指保證VOUT輸出電壓、電流情況下,VIN與VOUT的最小電壓差。這個壓差可以理解為LDO輸出電流在PMOS上的壓降。PMOS有導通電阻,假設(shè)VIN=3.4V,VOUT=3.2V,輸出電流300mA,則可以推算出PMOS的內(nèi)阻是

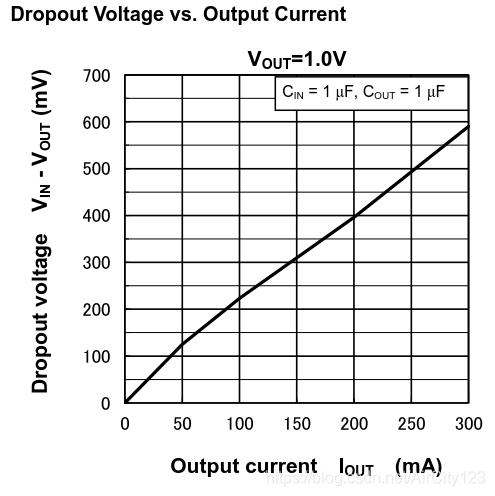

LDO工作必須滿足壓差要求,但壓差不是一個固定值,它與IOUT大小有關(guān)。下圖是一個VOUT=1V的LDO的輸出電流與壓差要求的關(guān)系曲線,可見輸出電流越小,對壓差要求也越小。壓差越小,LDO的效率越高。所以盡量不要讓LDO工作在接近極限的大電流狀態(tài),否則效率很低,LDO發(fā)熱嚴重,容易燒毀。

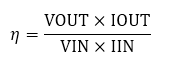

2.2效率

LDO效率定義如下:

其實IOUT和IIN基本是相等的,因為IIN就比IOUT多了個IGND,這個電流非常小,幾乎可以忽略。所以效率公式簡化如下。

可以簡單把LDO看做是一個穩(wěn)壓管,壓差越小,LDO的效率越高。

2.3靜態(tài)電流(IQ)

靜態(tài)電流Quiescent Current是外部負載電流為0時,LDO內(nèi)部電路供電所需的電流。內(nèi)部電路包括帶隙基準電壓源、誤差放大器、輸出分壓器以及過流和過溫檢測電路。這個電流經(jīng)過從LDO的GND流出。

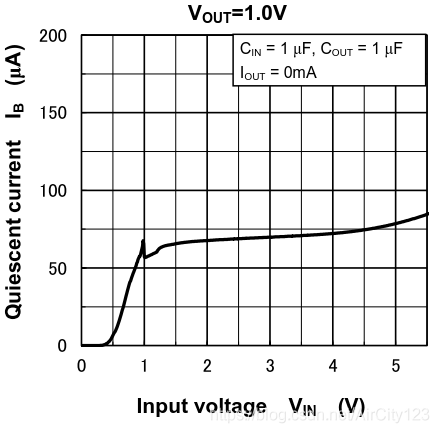

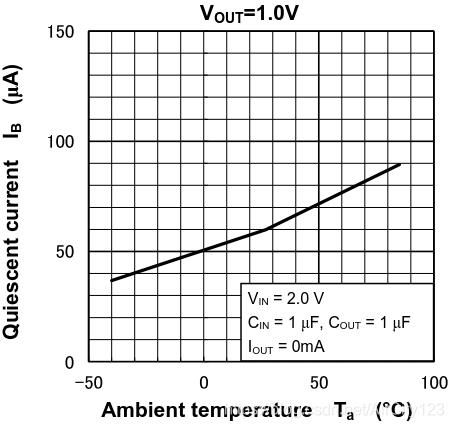

靜態(tài)電流受溫度和輸入電壓影響較大,高性能的ADI品牌LDO可能做到靜態(tài)電流對溫度電壓不敏感。下面兩幅圖是一個普通的LDO靜態(tài)電流隨VIN和溫度變化的曲線。常溫下靜態(tài)電流一般在uA和nA級別。

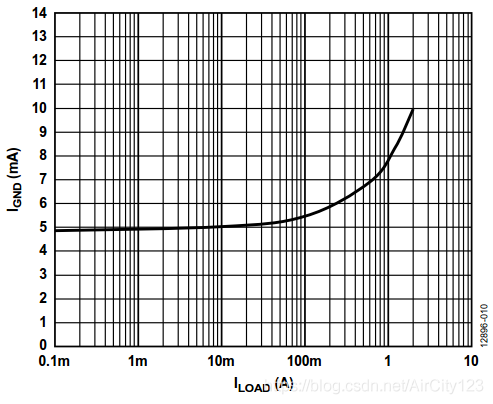

當輸出電流增大時,這個時候的靜態(tài)電流IQ,我們稱期為IGND,某些大功率的LDO,IGND也到了mA的級別:

大部分LDO的IQ很小,它是衡量LDO在低負載情況下的自身消耗的一個重要指標,IQ越小越好。在消費類電子領(lǐng)域,低IQ有利于更長的續(xù)航時間,低IQ值顯得尤為重要。

2.4關(guān)斷電流

LDO的輸出使能管腳ENn拉低后,VOUT=0V,此時VIN上消耗的電流就是關(guān)斷電流IQ(OFF)。關(guān)斷電流最高不會超過幾個uA。

2.5負載瞬態(tài)響應(yīng)Load Transient Response

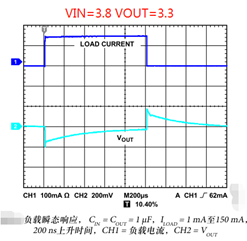

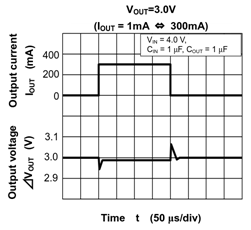

負載電流IOUT階躍變化時,輸出電壓VOUT的變化率。它與輸出端的電容值,電容的ESR,LDO控制環(huán)路的增益帶寬以及負載電流變化的大小和速率有關(guān)。文章開頭已經(jīng)講了,LDO是一個負反饋回路,其相位裕量越大,負載的瞬態(tài)響應(yīng)越好。下圖是ADP165和TCR3DG的瞬態(tài)響應(yīng)對比。第一幅圖VOUT電壓變化了約5.7%,第二幅圖VOUT變化了2.6%。東芝的LDO勝出。

有些廠家用電流負載調(diào)整率來表示這個值,公式如下:

負載調(diào)整率=?VOUT/?IOUT

道理是一樣的。

這個指標對輸出紋波有影響,越小越好。

2.6線路瞬態(tài)響應(yīng)Line Transient Response

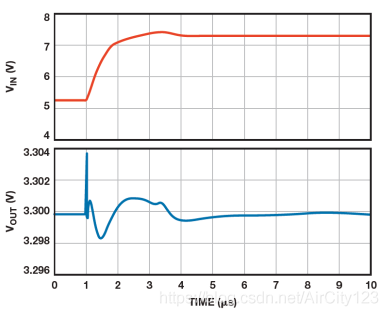

表示VIN階躍變化,VOUT的變化情況,如下圖。輸出電壓偏差顯示了環(huán)路帶寬和PSRR的特性,對于1.5us內(nèi)的2V變化,輸出電壓變化約2mV,表明1KHz是PSRR約為60dB。當VIN緩慢變化時,可能只會看到一個凹陷,沒有振鈴。

有些規(guī)格書稱這個指標為電壓負載調(diào)整率,并給出了公式,電壓負載調(diào)整率=?VIN/?VOUT。道理是一樣的。

Line Transient Response 隨負載電流增加而變差,因為LDO的總環(huán)路增益不斷降低。此外,LDO的功耗也隨著電壓差的增大而增加,這會導致PMOS結(jié)溫升高而使帶隙電壓和內(nèi)部失調(diào)電壓降低。

這個指標對輸出紋波有影響,越小越好。

2.7電源抑制比PSRR

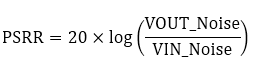

表示LDO對VIN上的噪聲的抑制能力,公式如下:

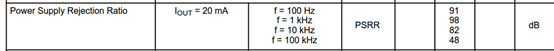

100K到1MHz內(nèi)的PSRR非常重要,這個是DCDC的噪聲頻率范圍,LDO經(jīng)常作為DCDC的下一級,要有能力濾除來自DCDC的大量噪聲。

在ADC,DAC,Camera的AVDD供電上,我們要選擇PSRR大于80dB(@100Hz)的LDO。

LDO的環(huán)路控制往往是確定電源抑制性能的主要因素,同時大容量,低ESR的電容對電源一直也非常有用,建議選擇陶瓷電容。

PSRR與頻率有關(guān),LDO的規(guī)格書一般會給出幾個頻點的PSRR值。

PSRR與IOUT有關(guān),通常情況下,輕載的PSRR高于重載。PSRR與LDO的相位裕量也有關(guān)系,這些關(guān)系請參考ADI文章《理解低壓差穩(wěn)壓器(LDO)實現(xiàn)系統(tǒng)優(yōu)化設(shè)計》。

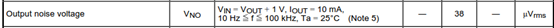

2.8輸出噪聲電壓

恒定輸出電壓電流,VIN上無紋波,給定范圍內(nèi)(10Hz~100KHz),VOUT上的噪聲電壓RMS。這部分噪聲主要來自于LDO內(nèi)部基準電壓源和誤差放大器。如下是某LDO的噪聲水平,通常在uV級別。

LDO輸出噪聲的另一種表示方式是噪聲頻譜密度。只有高精度,低噪聲電路上才需要關(guān)注這個參數(shù)。

2.9 自放電功能

LDO關(guān)閉后,負載電容上仍然后電量。LDO在下次輸出時,會因為這個電量,產(chǎn)生一個快速的Voltage Spike,雖然幅度不高,但對后級電路也會有破壞性。帶自放電功能的LDO能在LDO關(guān)閉輸出后,泄放輸出電容上的點電量。

3.LDO的輸出穩(wěn)定性要求

LDO是一個負反饋系統(tǒng),VIN和VOUT上的電容值,ESR都會影響這個系統(tǒng)的穩(wěn)定性,最主要是ESR在影響穩(wěn)定性。在LDO的規(guī)格書中,都會列出對輸入電容CIN和輸出電容COUT以及ESR的要求。一定要遵守這個要求。

TCR3DG規(guī)格書中要求COUT的ESR不得大于10Ω,位置靠近LDO,沒有其他明確要求,但是推薦CIN和COUT都用1uF。

ADP165規(guī)格書中要求CIN和COUT最小值0.7uF,ESR在0.001~0.2Ω之間。

LP5907SNX-1.8的規(guī)格書要求CIN>0.7uF;COUT=1uF-10uF,ESR=0.005~0.5Ω。

所以幾乎每一家的LDO,CIN和COUT都要求1uF以上,ESR越低越好,最好小于100mΩ,但也不能太小,低于幾個mΩ也可能使LDO工作不穩(wěn)定。

4.LDO選型參考

確定輸出電壓VOUT,建議選擇固定輸出電壓的,不要選有ADJ功能的,這樣節(jié)省器件,降低干擾。

確定輸出電流IOUT,至少留25%裕量。

確定壓差是否合適,一定要查看規(guī)格書上,對應(yīng)最大電流的最小壓差要求。

確認封裝,手機上一般用1x1 CSP的LDO

確認PSRR,如果用在低噪聲場合,一定要選擇高PSRR(80dB以上)的LDO,建議在80dB以上。

如果是電池供電,對續(xù)航要求很高,一定要選擇IQ低的LDO。

注意LDO的CIN和COUT要求,千萬不要錯。

如果要快速響應(yīng),可以選擇帶偏置電壓的LDO。

審核編輯:劉清

-

ldo

+關(guān)注

關(guān)注

35文章

2280瀏覽量

155680 -

PMOS

+關(guān)注

關(guān)注

4文章

265瀏覽量

30299 -

PSRR

+關(guān)注

關(guān)注

0文章

213瀏覽量

39852 -

pnp

+關(guān)注

關(guān)注

11文章

328瀏覽量

52649 -

低壓差線性穩(wěn)壓器

+關(guān)注

關(guān)注

0文章

211瀏覽量

12778

原文標題:LDO選型參考(原理、參數(shù))

文章出處:【微信號:衡麗,微信公眾號:衡麗】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

低壓差線性穩(wěn)壓器的選用技術(shù)

LDO低壓差線性穩(wěn)壓器

LDO低壓差線性穩(wěn)壓器的簡介

低壓差線性穩(wěn)壓器LDO內(nèi)部原理

淺談低壓差線性穩(wěn)壓器的壓差和功耗

低壓差線性穩(wěn)壓器(LDO)

評論