隨著移動(dòng)設(shè)備和可穿戴設(shè)備的日益普及,移動(dòng)存儲(chǔ)器的需求也在穩(wěn)步提升。對(duì)于移動(dòng)設(shè)備來說,便攜性是最重要的考量因素,低功耗和超薄封裝(PKG)技術(shù)也由此成為半導(dǎo)體行業(yè)不可或缺的要素。

內(nèi)聯(lián)重布線層(Inline Re-distribution Layer,簡稱 IRDL)技術(shù)是一種先進(jìn)的FAB技術(shù),使用由絕緣層和鋁組成的額外金屬層來形成布線,使IO焊盤能夠在必要時(shí)自由地重新放置到封裝(PKG)引線鍵合位置。這項(xiàng)技術(shù)使得芯片間的鍵合更薄、工藝更簡單。此外,內(nèi)聯(lián)重布線層(IRDL)技術(shù)是重布線層(RDL)技術(shù)之一。顧名思義,這項(xiàng)技術(shù)的命名是因?yàn)槠湔麄€(gè)過程都在FAB內(nèi)部進(jìn)行,這與封裝重布線層技術(shù)(PKG RDL)有所不同。

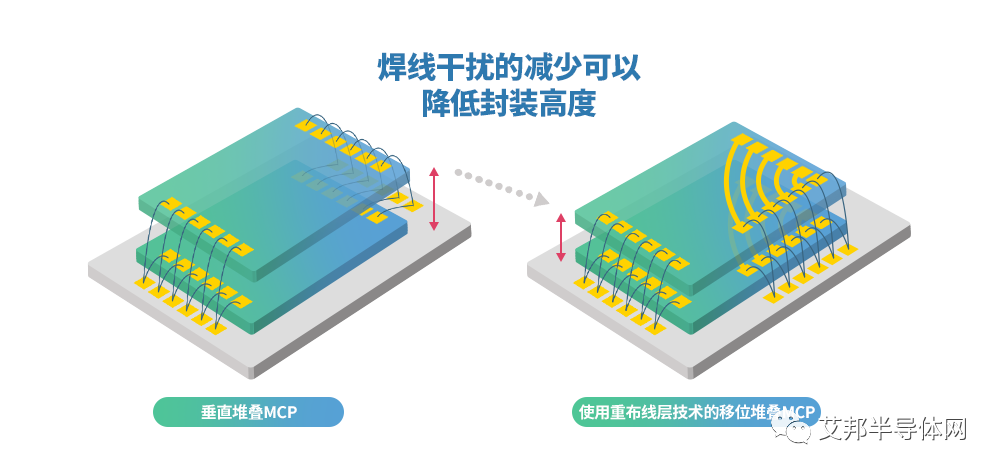

圖1. 垂直堆疊MCP與移位堆疊MCP

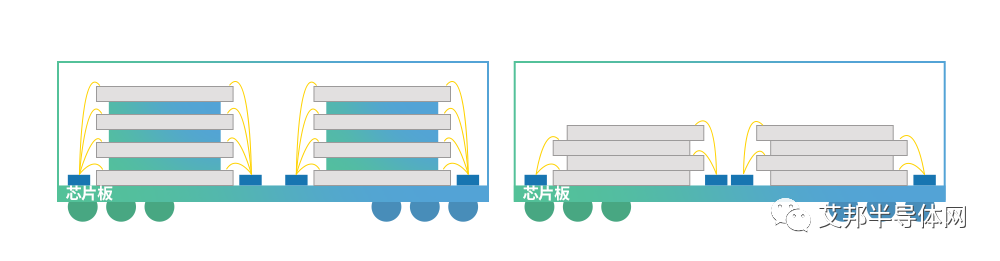

圖2. 圖1的橫斷面視圖

上圖展示了芯片的兩種多芯片封裝(MCP)1*方法。左側(cè)是目前通用的“垂直堆疊MCP”方法,其中上部芯片垂直堆疊在下部芯片的焊盤上;右側(cè)是“使用重布線層(RDL)技術(shù)的移位堆疊MCP”方法,可以避開焊盤。垂直堆疊MCP方法往往會(huì)導(dǎo)致導(dǎo)線干擾問題和導(dǎo)線與芯片之間短路問題,而新的移位堆疊MCP方法可以很好地避免這些問題。這種新的堆疊方法可以減小上層芯片和下層芯片之間的間隙,更容易滿足客戶對(duì)厚度的要求。

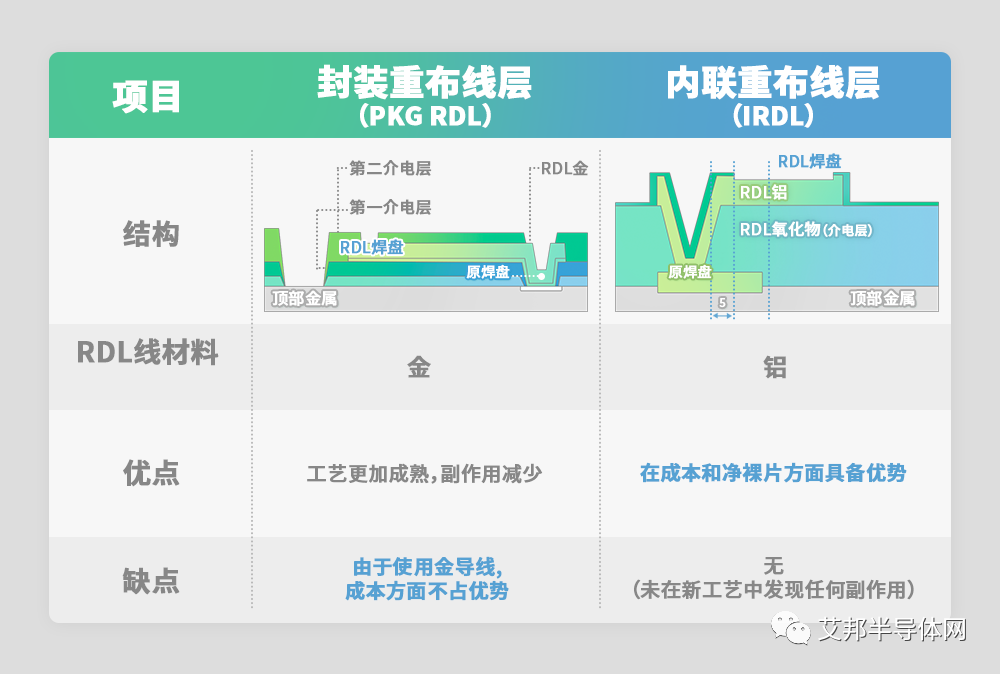

現(xiàn)有封裝重布線層(RDL)技術(shù)與內(nèi)聯(lián)重布線層(IRDL)技術(shù)的比較

封裝重布線層(PKG RDL)技術(shù)和內(nèi)聯(lián)重布線層(IRDL)技術(shù)之間的主要區(qū)別在于結(jié)構(gòu)形成方法,所以接下來,我們需要更加深入地了解內(nèi)聯(lián)重布線層(IRDL)技術(shù)的優(yōu)勢。

圖3.封裝重布線層(PKG RDL)技術(shù)與內(nèi)聯(lián)重布線層(IRDL)技術(shù)的比較 封裝重布線層(PKG RDL)的結(jié)構(gòu)形成方法大致分為兩個(gè)過程:FAB輸入和FAB輸出。

FAB輸入過程是在僅打開焊盤的狀態(tài)下,用絕緣材料覆蓋頂部金屬。然后,在FAB輸出過程中,使用第一介電層將重布線層線與晶圓頂部的絕緣材料分開,并使用金作為導(dǎo)線。之后,使用第二介電層覆蓋導(dǎo)線頂部。

另一方面,內(nèi)聯(lián)重布線層(IRDL)方法使用絕緣材料覆蓋頂部金屬并形成過孔(VIA)以打開焊盤。

然后,使用鋁作為導(dǎo)線,這就是與封裝重布線層(PKG RDL)方法的不同之處。最后,在頂部涂上絕緣材料。

內(nèi)聯(lián)重布線層(IRDL)方法與封裝重布線層(PKG RDL)方法的目的相同,均旨在重新放置焊盤。但是,隨著FAB內(nèi)部流程的改進(jìn),內(nèi)聯(lián)重布線層(IRDL)技術(shù)在重布線層(RDL)技術(shù)的基礎(chǔ)上擁有三項(xiàng)優(yōu)勢:

? 首先,由于電路可以放置在焊盤下方,因此凈裸片的性能得以改善;

? 其次,使用鋁代替金可以將整個(gè)工藝的成本降低高達(dá)30%;

? 最后,電路設(shè)計(jì)人員可以借助重布線層(RDL)技術(shù)來增強(qiáng)電源網(wǎng)格2*,由此提升芯片性能。

較小的芯片可將電路置于焊盤下方,從而提升凈裸片的性能

當(dāng)使用現(xiàn)行封裝重布線層(PKG RDL)結(jié)構(gòu)時(shí),由于頂部的金屬過薄(小于1um),因此在探測和鍵合期間經(jīng)常會(huì)發(fā)生許多與焊盤相關(guān)的問題。

使用內(nèi)聯(lián)重布線層(IRDL)結(jié)構(gòu)時(shí),頂部金屬的厚度可以達(dá)到近10um的水平,足以承受探測和鍵合過程中產(chǎn)生的應(yīng)力,使得電路可以放置在焊盤下方。這樣的結(jié)構(gòu)可以縮小芯片尺寸,由此改善凈裸片的性能。

使用內(nèi)聯(lián)重布線層(IRDL)技術(shù)提升配電網(wǎng)絡(luò)(PDN)性能

使用內(nèi)聯(lián)重布線層(IRDL)技術(shù)的增強(qiáng)型電源網(wǎng)格可以提升配電網(wǎng)絡(luò)(power distribution network,簡稱 PDN)性能,更好地改進(jìn)芯片性能。

如果不借助內(nèi)聯(lián)重布線層(IRDL),則只能使用芯片現(xiàn)有的金屬布線來提升配電網(wǎng)絡(luò)性能,但是這樣的做法會(huì)導(dǎo)致遠(yuǎn)離焊盤的區(qū)域出現(xiàn)配電網(wǎng)絡(luò)性能下降的問題。這種方法對(duì)于配電網(wǎng)絡(luò)性能的提升作用非常有限。

另一方面,在使用內(nèi)聯(lián)重布線層(IRDL)時(shí),重布線層(RDL)的特性決定著傳遞的電阻值較低,配電網(wǎng)絡(luò)性能由此得到大幅提升。因此,可以通過使用內(nèi)聯(lián)重布線層(IRDL)技術(shù)的方法來提升芯片的性能。

內(nèi)聯(lián)重布線層(IRDL)技術(shù):未來設(shè)備的先驅(qū)

內(nèi)聯(lián)重布線(IRDL)層技術(shù)能夠降低流程成本,可以在不損害現(xiàn)有芯片架構(gòu)的前提下,將IO焊盤重新放置到封裝所需的位置。

內(nèi)聯(lián)重布線層(IRDL)技術(shù)有助于企業(yè)更好地適應(yīng)移動(dòng)設(shè)備的未來發(fā)展方向——更輕更薄的產(chǎn)品。這項(xiàng)元件技術(shù)的誕生對(duì)于整個(gè)行業(yè)來說有著至關(guān)重要的意義,因?yàn)樗梢钥s小芯片尺寸,增強(qiáng)芯片性能,推動(dòng)凈裸片的發(fā)展。

1*MCP:多芯片封裝技術(shù)是一種將兩個(gè)以上的半導(dǎo)體芯片堆疊到一個(gè)封裝中,在增加容量和提升性能的同時(shí),減少占用空間的技術(shù)。

這項(xiàng)技術(shù)主要用于智能手機(jī)和平板電腦等輕薄便攜設(shè)備。借助內(nèi)聯(lián)重布線層(IRDL)技術(shù),企業(yè)可以在多芯片封裝過程中制造出更輕薄的芯片。

2*電源網(wǎng)格(Power Mesh):由多金屬層上的電線組成的網(wǎng)絡(luò)。

審核編輯:劉清

-

PKG

+關(guān)注

關(guān)注

0文章

5瀏覽量

8498 -

Via

+關(guān)注

關(guān)注

0文章

44瀏覽量

19232 -

FAB

+關(guān)注

關(guān)注

1文章

29瀏覽量

9856 -

PDN

+關(guān)注

關(guān)注

0文章

83瀏覽量

22703 -

MCP

+關(guān)注

關(guān)注

0文章

254瀏覽量

13900

原文標(biāo)題:內(nèi)聯(lián)重布線層(IRDL)技術(shù)推動(dòng)芯片革命

文章出處:【微信號(hào):wc_ysj,微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TIMx簡介及主要功能

電池管理系統(tǒng)的主要功能包括哪些

網(wǎng)卡實(shí)現(xiàn)的主要功能是什么

TMF框架是什么?其主要功能有哪些

mac層的主要功能介紹

內(nèi)聯(lián)重布線層(IRDL)及其主要功能簡介

內(nèi)聯(lián)重布線層(IRDL)及其主要功能簡介

評(píng)論