IC前后端:高扇出的危害

1、什么是高扇出?

高扇出指的是一個邏輯單元驅動的邏輯單元過多。常見于寄存器驅動過多的組合邏輯單元。至于驅動多少邏輯單元算過多,需要根據工藝,后端實現情況以及芯片本身類型來決定。

一般來說如果驅動邏輯大于10K以上,算是比較多的了。

2、高扇出有哪些危害?

危害1:驅動能力下降,時序緊張

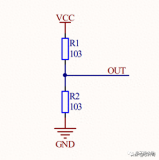

扇出過高也就是也就意味了負載電容過大,電路原理基礎告訴咱們,負載電容越大,充放電速度越慢,電平跳變所需要的時間增加,即驅動能力下降,時序更加緊張。面對高扇出的情況,后端工具通常會通過插入buffer增加驅動能力,然后插入buff又會增加延時,造成時序緊張。

危害2:不利于布局布線,會增加走線延時

高扇出的情況通常意味著負載end_point分布在block的各個位置。而驅動的start_point需要放置在相對應的中心位置,這就意味到start_point到end_points的走線延時較大,一旦時序緊張,后端工具需要花費很多時間去優化,玩玩結果還不理想。

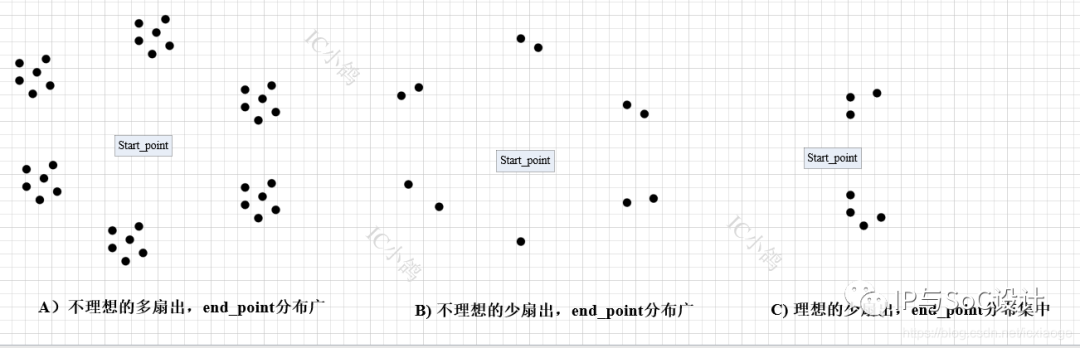

如下圖所示:黑色點為end_point

A圖所示,扇出高并且end_point很分散,在高扇出情況中很常見,后端工具實現花費時間長,并且很難優化,走線延時比較大,時序比較緊張。

B圖所示:扇出不高但是end_point很分散,后端工具實現花費時間教長,優化有難度,走線延時比較大,時序比較緊張。

C圖所示, 扇出不高并且end_point集中,是理想情況,后端工具實現簡單,走線延時比較小。

1、RAM讀寫沖突返回值

在使用底層RAM IP的時候,以1R1W的ram為例,我們需要考慮 某個地址同時發生讀寫操作的時候(俗稱讀寫沖突),RAM IP輸出的data_out是什么值,不同的廠家IP會不一樣,同一個廠家的不同ram也有可能不一樣。例如:發生讀寫沖突時,有些ram會輸出老值,有些ram會輸出新值,有些ram輸出不確定的值

2、從設計角度考慮RAM讀寫沖突返回值

從嚴謹的設計角度看,應該從方案設計角度避免此問題。在verilog實現中,ram就不允許發生同時讀寫同一個地址的情況,采用外部邏輯進行讀寫沖突保護。原因如下:

不同ram IP在讀寫沖突時,讀寫沖突返回值不一樣,容易出錯。

不同項目使用的工藝不一樣,從而導致ram ip讀寫沖突返回值不一致,不利于代碼復用。

IC設計RAM相關:ECC校驗原理基礎

1、ECC校驗基礎

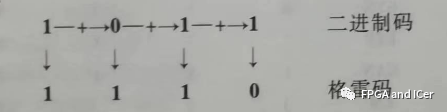

Ram的ECC校驗通常基于海明碼編碼原理實現,使用海明碼編碼需要額外的bit位存儲校驗位,ECC校驗僅能糾正1bit的,無法糾正2bit以及以上數據錯誤,能發現部分多bit位錯誤的情況。

2、RAM ECC校驗實現原理

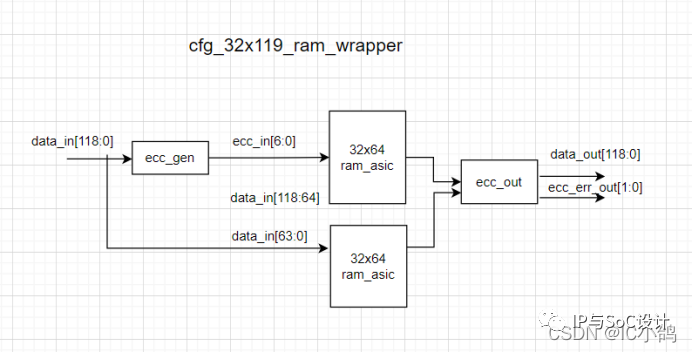

如圖所示為1r1w的ram為例,cfg_32x119_ram_wrapper為verilog代碼直接調用層次的ram_wrapper,表示了一個深度為32,數據位寬為119bit的ram。ram_asic.v為真實的ram IP。其中119bit的數據位寬緊張ECC計算需要7bit的校驗位,因此物理IP最少需要126bit的ram IP。通常memory產生工具會更具時鐘頻率,深度位寬等因素對ram進行切分,因此本例中,使用了2個32x64的ram ip。

在data_in寫入ram_asic模塊之前,會經過ecc_gen模塊,產生7bit的ecc校驗位,隨著數據一同寫入ram_asic,其中data_in[63:0]寫入第一個ram_asic,{2’b0,ecc_in[6:0],data_in[118:64]}寫入第二個ram_asic。從ram_asic讀出的數據會經過ecc_out模塊經過ecc校驗,輸出校驗后的data_out[118:0]和2bit的ecc_err_out告警。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

50936瀏覽量

424681 -

IC設計

+關注

關注

38文章

1297瀏覽量

104083 -

RAM

+關注

關注

8文章

1369瀏覽量

114765 -

ECC

+關注

關注

0文章

97瀏覽量

20585 -

邏輯單元

+關注

關注

0文章

25瀏覽量

5131

原文標題:IC設計知識點:高扇出的危害、RAM相關

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IC設計知識點:高扇出的危害、RAM相關

IC設計知識點:高扇出的危害、RAM相關

評論