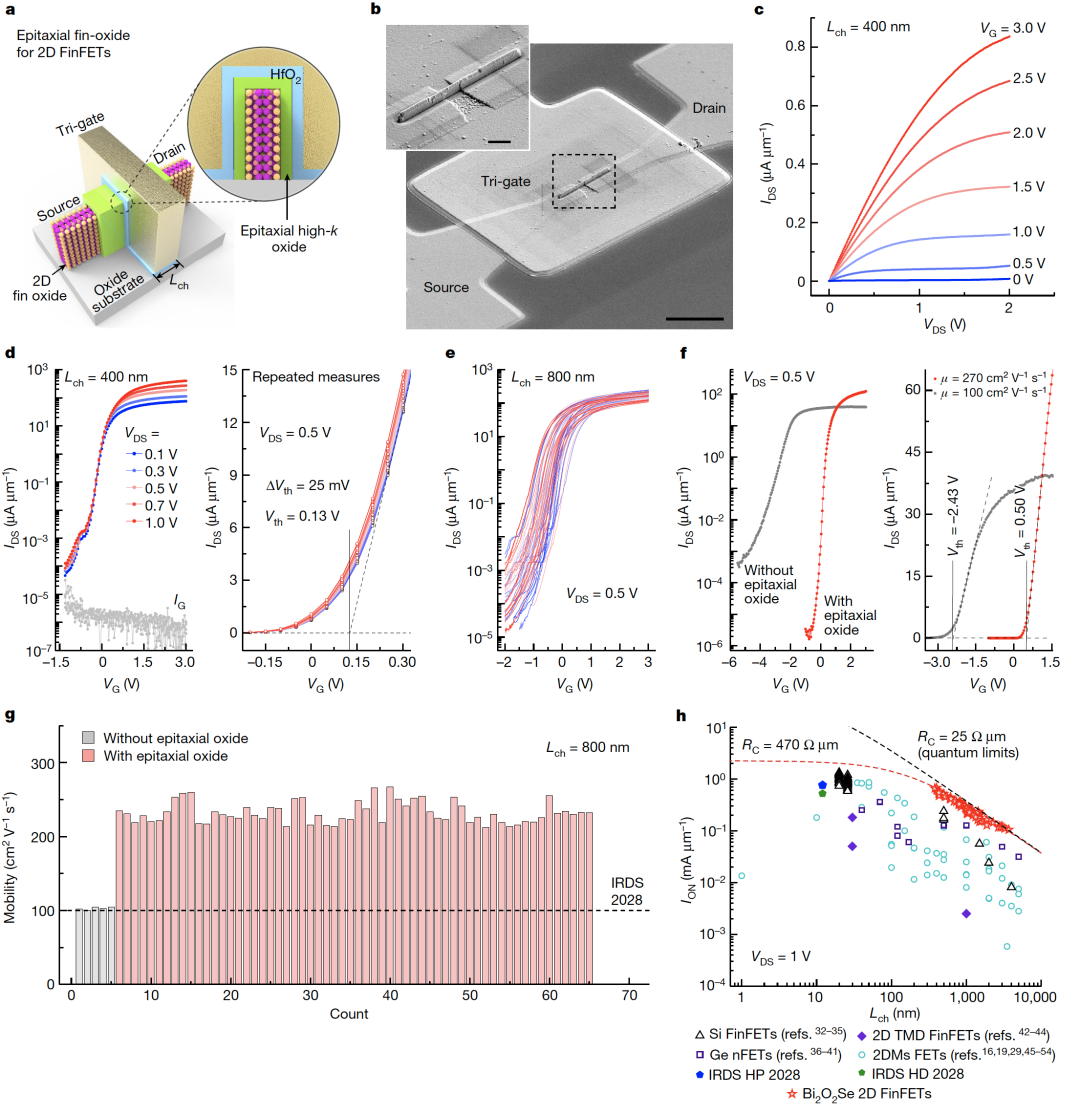

2023年3月22日,北京大學彭海琳教授課題組在《自然》(Nature)期刊上發表題為“2D fin field-effect transistors integrated with epitaxial high-κ gate oxide”的研究論文。該研究報道了一種全新二維半導體垂直鰭片/高介電自氧化物外延集成架構(2D fin/oxide Bi2O2Se/Bi2SeO5),并研制了高性能二維鰭式場效應晶體管(2D FinFET)。二維半導體鰭片/自氧化物外延異質結構具有原子級平整界面和超薄的鰭片厚度(可達一個單胞厚度,~1.2 nm),并實現了晶圓級單一定向陣列制備以及定點、高密度生長。基于Bi2O2Se/Bi2SeO5外延異質結的二維鰭式場效應晶體管具有高達270 cm2/Vs的電子遷移率、極低的關態電流(~1 pA/μm)和很高的開/關態電流比(108),溝道長度為400 nm時開態電流密度高達830 μA/μm,滿足國際器件與系統路線圖(IRDS)的2028年低功耗器件目標要求。該原創性工作突破了后摩爾時代高速低功耗芯片的關鍵新材料與新架構三維異質集成瓶頸,為開發突破硅基晶體管極限的未來芯片技術帶來新機遇。論文通訊作者是彭海琳教授,并列第一作者是譚聰偉、于夢詩、唐浚川、高嘯寅。

研究背景

晶體管作為芯片的核心元器件,通過尺寸微縮、材料多功能集成和架構優化等方式,不斷提高芯片集成度,進而提升能效和算力。摩爾定律的推動下,目前傳統硅基芯片已成功迭代至5 nm制程節點。隨著集成電路制程向亞3納米技術節點邁進,芯片尺寸微縮逼近硅基材料物理極限,短溝道效應和熱效應日趨顯著,新材料、新架構和新器件的探索與研究迫在眉睫。

一代制程,一代材料,一代架構。集成電路過去70多年發展中,高遷移率應變硅的應用、高介電常數(κ)氧化物與半導體溝道的異質集成、垂直鰭片架構的開發都為推動現代芯片產業發展做出了劃時代的貢獻。后摩爾時代,高遷移率二維半導體因其表面無懸掛鍵、原子級厚度和高遷移率等特性,可實現出色的柵控和高驅動電流,抑制短溝道效應,因此被作為“后硅”延續時代晶體管尺寸微縮的重要材料之一。垂直鰭片(Fin)架構通過增加溝道柵控面積,協同高κ氧化物與鰭片溝道異質集成,大大增強器件柵控能力,抑制短溝道效應,并降低亞閾值漏電流,進一步突破芯片算力、能效和集成瓶頸。以垂直鰭片(Fin)硅基溝道架構和三柵極圍繞結構的鰭式場效應晶體管(FinFET)技術在2011年商業化量產于22 nm制程工藝,主導了現代晶體管微縮制程工藝,也是當前最先進的商用5 nm制程集成電路的主流溝道架構。

工藝技術節點進入亞3 nm以后,垂直鰭片溝道架構的新器件開發仍備受關注,人們正在考慮制造基于垂直鰭式結構開發垂直圍柵器件(VGAA)或垂直傳輸場效應晶體管(VTFET),以滿足“后摩爾時代”芯片的更高集成度、高性能和低功耗發展要求,世界著名集成電路制造龍頭公司IBM和三星已進行相關研發。由此,實現全新架構高遷移率二維層狀半導體垂直鰭片/高介電(κ)氧化物異質結的異質集成,開發二維鰭式場效應晶體管(2D FinFET)及二維圍柵器件(2D GAA)等新架構器件,有望突破傳統硅基半導體亞5 nm厚度量子限域效應的材料限制,將讓芯片迭代進入一個嶄新的時代,被認為是向下一代晶體管邁進的一個里程碑,屬于世界科技前沿的熱點和新興領域。然而,全新架構二維垂直鰭片/高κ氧化物的三維異質集成一直是尚未解決的難題,尚屬于空白,亟待突破。

近年來,北京大學彭海琳教授課題組主要從事二維材料物理化學與表界面調控研究,致力于解決新型高遷移率二維材料(金屬硫氧族材料、石墨烯等)的表界面生長控制及結構與性能調控中具有挑戰性的國際前沿科學問題,創制了全新二維半導體芯片材料Bi2O2Se,受到國內外同行的廣泛關注和追蹤,開啟了二維半導體Bi2O2Se的研究序幕(Nature Nanotechnol.2017, 12, 530;Acc. Mater. Res.2021, 2, 842.),并開發了二維半導體Bi2O2Se的超薄高κ自然氧化物柵介質Bi2SeO5及高性能二維晶體管(Nature Electron.2020, 3, 473;Nature Electron.2022, 5, 643;Nature Mater.2023)。

研究內容與圖文

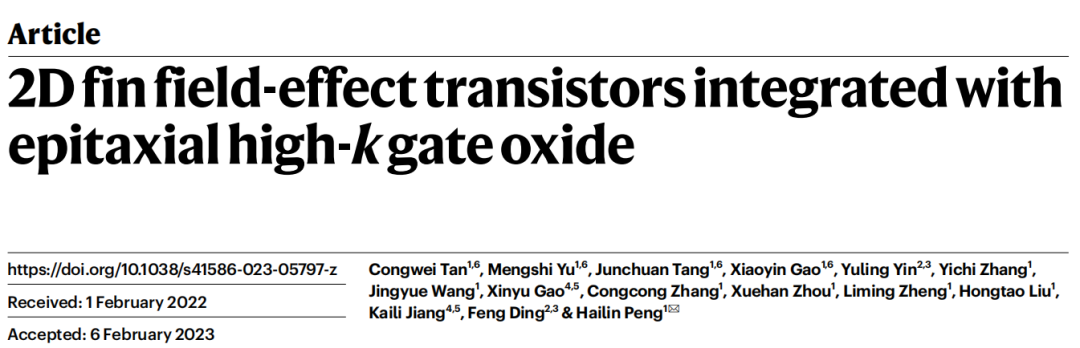

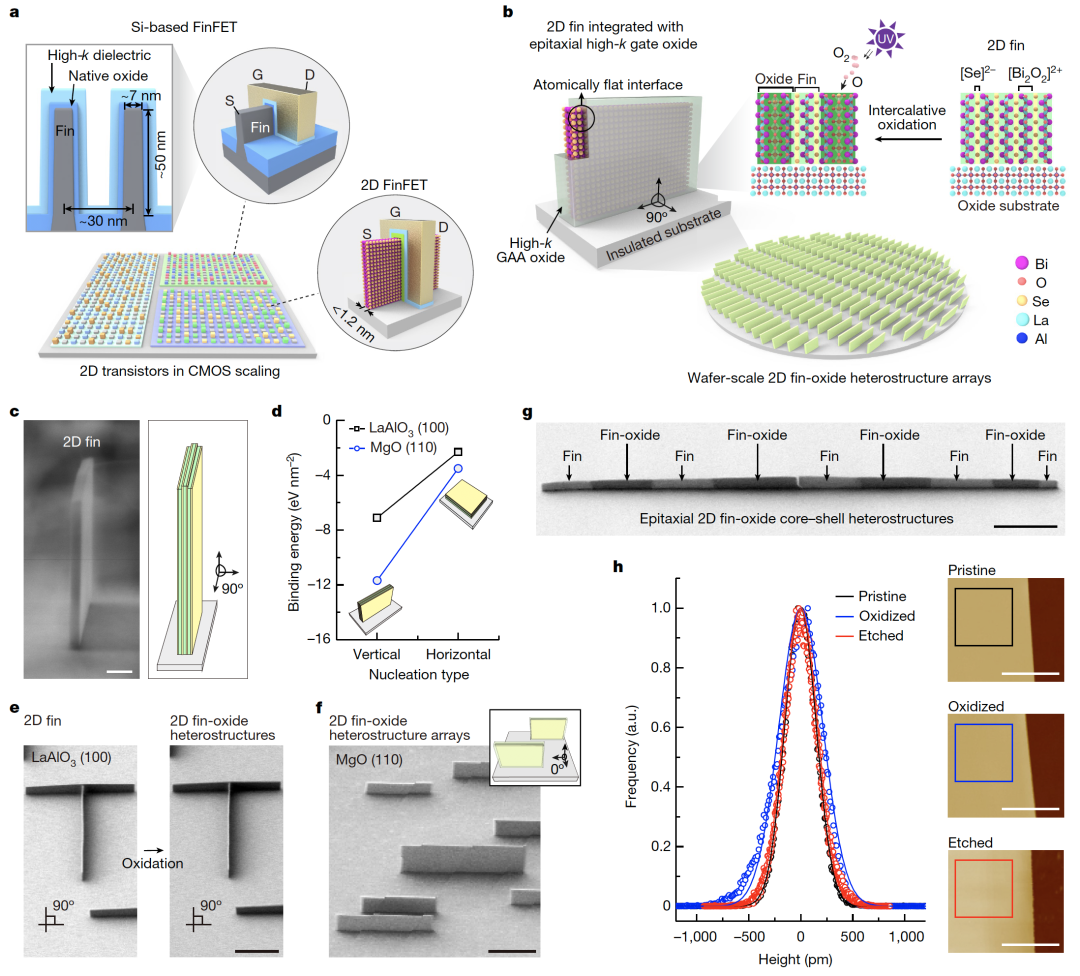

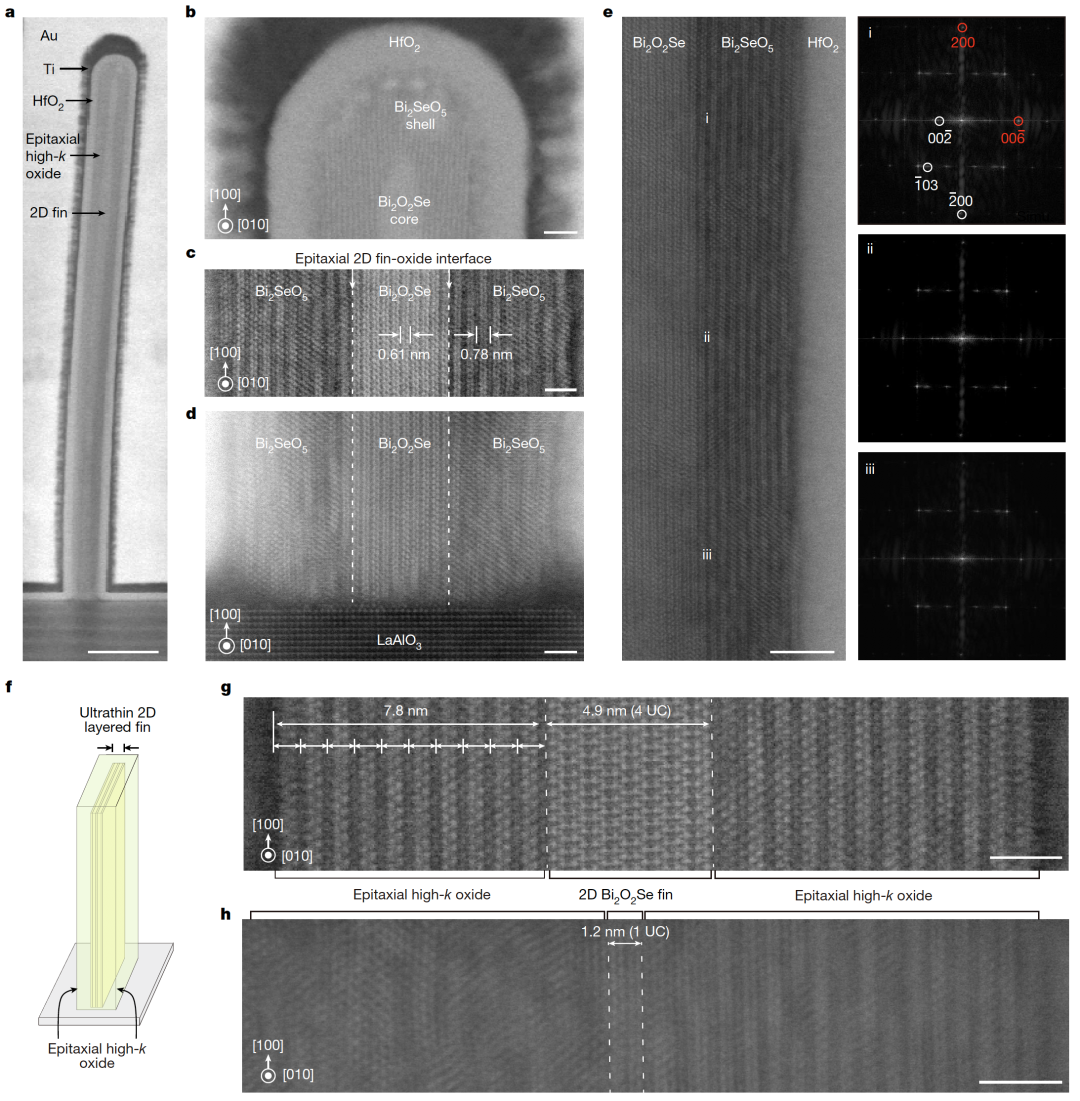

針對全新三維架構中二維溝道材料與介電質集成這一科學難題和實際應用需求,最近,北京大學彭海琳教授課題組獨辟蹊徑,基于自主研發的新型二維鉍基材料體系,實現了自支撐高遷移率二維半導體Bi2O2Se垂直鰭片的精準合成。同時,結合可控氧化手段,實現了晶圓級二維Bi2O2Se垂直鰭片/高κ自氧化物Bi2SeO5的異質集成。值得強調的是,二維Bi2O2Se可被逐層可控插層氧化減薄至1個單胞厚度(1.2納米),并與高κ自氧化物Bi2SeO5形成原子級平整、晶格匹配的高質量半導體/介電層界面。結合微納加工及刻蝕技術,精確控制異質架構的成核過程,實現了單一取向的二維垂直鰭片/高κ自氧化物異質結陣列的定點和定向外延。并在此基礎上首次實現了溝道厚度約6納米的高性能二維垂直鰭式晶體管(2D FinFET)的研制。二維FinFET在遷移率(270 cm2/Vs)、關態電流(1 pA/μm)和開關比(108)等性能滿足業界高性能低功耗器件要求的同時,相對于商用Si、Ge及過渡金屬硫化物等溝道材料,在開態電流密度方面展現出二維FinFET電子學的優勢。

圖1:二維層狀半導體鰭式陣列與高κ全環繞氧化物柵介質集成。

圖2:二維層狀半導體鰭片/氧化物外延異質結的結構表征。

圖3:定向二維鰭片/氧化物異質結陣列的精確集成。

圖4:二維鰭片/氧化物異質結制備的二維FinFET電學性能。

該項研究成果實現了“從0到1”的創新突破,首次創制了一類全新架構的高遷移率二維半導體垂直鰭片/高κ自氧化物異質結,并在國際上率先研制了高性能二維鰭式場效應晶體管(2D FinFET),在二維材料表界面生長控制、低維材料結構與性能調控、新原理器件開發、新架構器件三維異質集成、高算力低功耗集成電路芯片等領域具有開拓性意義。該研究成果得到國家自然科學基金委、科技部、北京分子科學國家研究中心、騰訊基金會、北京大學博雅博士后、北京分子科學國家研究中心博士后項目(BMS Junior Fellow)等機構和項目的資助,并得到了北京大學化學與分子工程學院分子材料與納米加工實驗室(MMNL)儀器平臺的支持。

審核編輯 :李倩

-

半導體

+關注

關注

334文章

27305瀏覽量

218161 -

元器件

+關注

關注

112文章

4713瀏覽量

92221 -

場效應晶體管

+關注

關注

6文章

363瀏覽量

19495

原文標題:Nature:從0到1!北京大學彭海琳教授課題組報道外延高κ柵介質集成型二維鰭式晶體管

文章出處:【微信號:DT-Semiconductor,微信公眾號:DT半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

金屬氧化物和柔性石墨烯MOS的區別

半導體研究所在量子點異質外延技術上取得重大突破

二維材料 ALD 的晶圓級集成變化

帶有集成金屬氧化物半導體場效應晶體管(MOSFET) 的非同步降壓穩壓器數據表

帶有集成金屬氧化物半導體場效應晶體管 (MOSFET) 的非同步降壓穩壓器TPS5403數據表

帶有集成金屬氧化物半導體場效應晶體管TPS65270數據表

帶有集成金屬氧化物半導體場效應晶體管 (MOSFET) 的非同步降壓穩壓器TPS5405數據表

自助還書機如何集成(選配)二維碼掃描模塊?

上海合晶掛牌上市,深耕半導體硅外延片領域

半導體襯底和外延有什么區別?

半導體硅外延片制造商上海合晶上市

簡單認識功率金屬-氧化物-半導體場效應管

全新二維半導體垂直鰭片/高介電自氧化物外延集成架構

全新二維半導體垂直鰭片/高介電自氧化物外延集成架構

評論