1 運行平臺

硬件:CRD500數(shù)字信號處理板

系統(tǒng):win7/64;win7/32;win10/64;win11/64

軟件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指標

功能:

1)可產(chǎn)生基帶碼元數(shù)據(jù)

2)基帶數(shù)據(jù)的成型濾波器電路

3)產(chǎn)生PSK調(diào)制數(shù)據(jù)

4)完成PSK解調(diào)(載波提取,相干解調(diào))

性能:

調(diào)制端:

1)系統(tǒng)時鐘:50MHz

2)基帶數(shù)據(jù)速率:390.625kbps

3)基帶成型濾波器成型系數(shù):0.8

4) 載波頻率:390.625kHz

解調(diào)端:

1)采樣頻率:3.125MHz

2)解調(diào)方式:Costas環(huán)提取載波,相干解調(diào)

3 程序結(jié)構(gòu)框圖說明

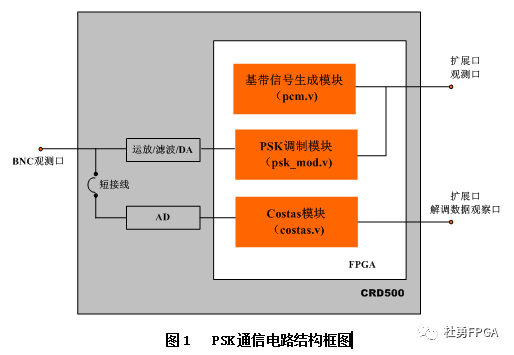

Psk調(diào)制解調(diào)電路程序主要由基帶信號生成模塊(pcm.v)、Psk調(diào)制模塊(psk_mod.v)、Costas模塊(Costas.v)組成。

基帶信號生成模塊(pcm.v)產(chǎn)生碼率為390.625kbps的基帶數(shù)據(jù),送給CRD500擴展口觀測的同時,送給PSK調(diào)制模塊;PSK調(diào)制模塊完成PSK信號調(diào)制,先對PCM基帶數(shù)據(jù)進行成型濾波,控制傳輸頻帶,再與390.625kHz的載波進行相乘,完成PSK調(diào)制;PSK調(diào)制數(shù)據(jù)經(jīng)CRD500板上的DA、濾波、運放模塊送BNC測試口的同時,經(jīng)板上短接線回至AD通道,經(jīng)AD采樣后回送至FPGA,由Costas模塊完成相干載波提取的同時完成數(shù)據(jù)解調(diào);解調(diào)后的數(shù)據(jù)送至CRD500的擴展口用于示波器觀測。

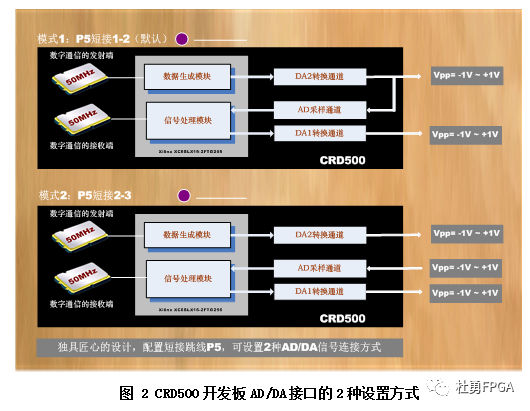

CRD500板上AD/DA接口有多種設置方式,如圖2所示。

本次工程實例采用圖2中的模式1連接方式。如果采用圖2中的第2種模式,則需要采用雙頭BNC線將AD接口與DA接口連接起來。

4 測試說明

在測試過程中可以發(fā)現(xiàn),上電后下載程序,輸入信號及本地載波信號能夠快速完成同步,數(shù)據(jù)解調(diào)正常。當按下key1鍵,使得costas環(huán)路無輸入信號,則載波無法同步,無法解調(diào)正確,松開key1鍵后兩路波形又自動完成同步且解調(diào)正確。

但如長時間按下key1鍵,偶爾會出現(xiàn)即使松開key1鍵后,兩路信號仍不同步且解調(diào)不正確的情況,這是由于在環(huán)路沒有輸入信號時,始終處于搜索狀態(tài),環(huán)路可能出現(xiàn)“死循環(huán)”或“跑飛”的現(xiàn)象,這時只要按下復位鍵,則兩路信號又會迅速同步,完成正常的解調(diào)。

本電路僅提供驗證環(huán)路在上電或復位后完成同步鎖定及解調(diào)的功能驗證,不提供防止環(huán)路“跑飛”的功能程序,請用戶自行完成防“跑飛”的功能程序。

審核編輯:劉清

-

濾波器

+關(guān)注

關(guān)注

161文章

7924瀏覽量

179587 -

示波器

+關(guān)注

關(guān)注

113文章

6342瀏覽量

186609 -

PSK

+關(guān)注

關(guān)注

1文章

27瀏覽量

21071 -

BNC接頭

+關(guān)注

關(guān)注

0文章

13瀏覽量

7509

原文標題:PSK調(diào)制解調(diào)(Quartus/Verilog/CRD500)

文章出處:【微信號:杜勇FPGA,微信公眾號:杜勇FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

PSK調(diào)制解調(diào)知識簡析

PSK調(diào)制解調(diào)知識簡析

評論