在之前關(guān)于提高數(shù)據(jù)采集(DAQ)性能以實(shí)現(xiàn)電網(wǎng)保護(hù)、控制和監(jiān)測設(shè)備的博文中,我闡述了連接多個模數(shù)轉(zhuǎn)換器(ADCs)的必要性,以及如何使用單個Sitara?處理器中的可編程實(shí)時單元和工業(yè)通信子系統(tǒng)(PRU-ICSS)和使用多個高性能、可同步的sigma-delta ADCs來提高DAQ性能和測量精度。

在此篇博文中,將闡述如何通過使用電源模塊來產(chǎn)生多個供電電壓的方式來增強(qiáng)DAQ性能,包括5-V、3.3-V、2.5-V和 1.8-V電源導(dǎo)軌。

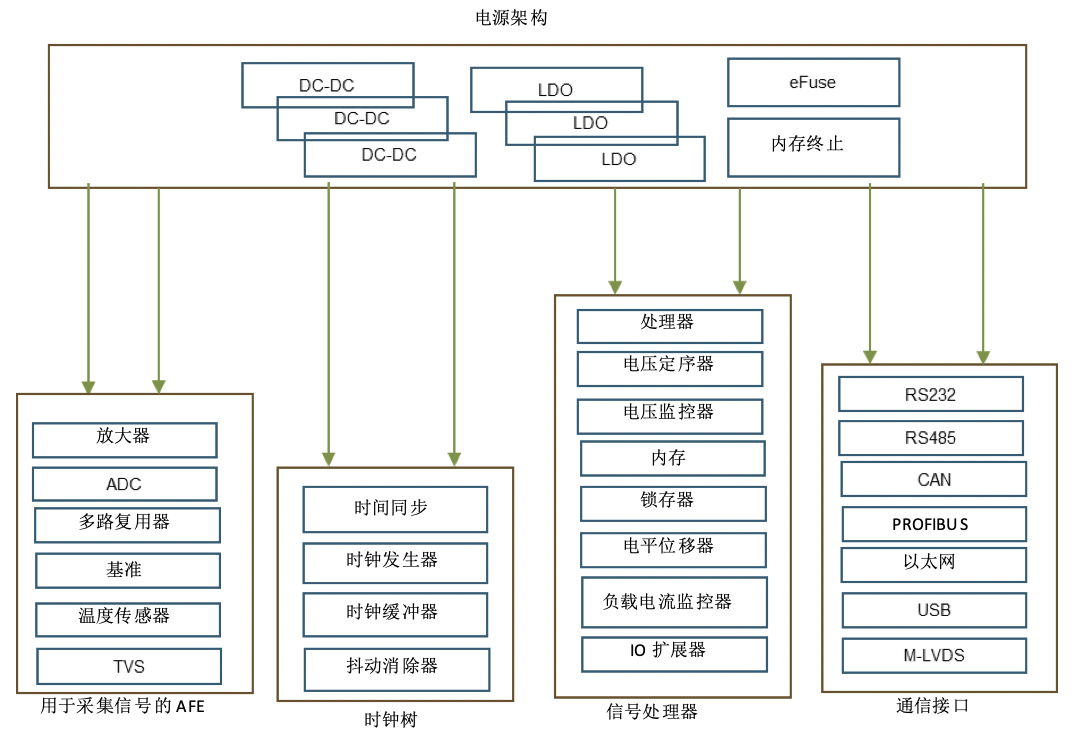

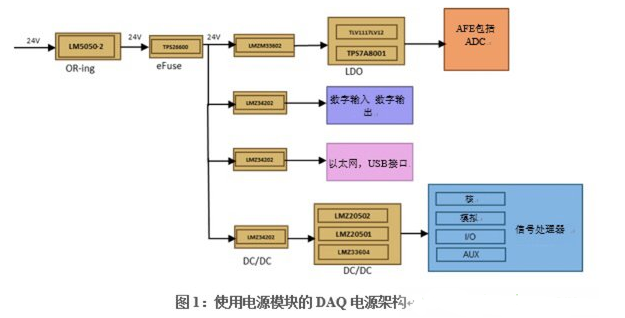

圖1顯示了一個帶有通常配置子系統(tǒng)的DAQ,以及其中發(fā)現(xiàn)/使用的設(shè)備或集成電路(IC)。每個子系統(tǒng)都有不同的電壓水平和負(fù)載電流要求。DAQ的電源架構(gòu)由多個DC/DC轉(zhuǎn)換器、低壓差穩(wěn)定器(LDO)、用于生成和監(jiān)控各種電源導(dǎo)軌的雙數(shù)據(jù)速率終端穩(wěn)壓器、定序器和監(jiān)控器以及一個防止輸入過載的eFuse。

圖1:包括電源架構(gòu)在內(nèi)的DAQ子系統(tǒng)

DAQ電源架構(gòu)設(shè)計方法

選擇合適的電源架構(gòu)取決于DAQ性能要求,包括效率、印刷電路板(PCB)空間、嚴(yán)格的輸出調(diào)節(jié)、負(fù)載瞬態(tài)響應(yīng)和成本。您可以使用各種DC/DC轉(zhuǎn)換器和LDO的組合從背板電壓中獲得所需的電源導(dǎo)軌。

分立電源實(shí)現(xiàn)需要電源設(shè)計專業(yè)知識。分立電源實(shí)現(xiàn)需使用一個外部電感器、開關(guān)和其他外部組件。DC/DC轉(zhuǎn)換器會占用更多板空間、效率低且熱性能差。由于缺乏防止誤用的保護(hù)(輸出過載、輸入電壓過高),以及組件故障導(dǎo)致的壽命縮短,分立電源也容易發(fā)生故障。實(shí)現(xiàn)DAQ電源架構(gòu)的另一種方法是使用集成電源模塊。

使用TI電源模塊的優(yōu)勢

DC/DC降壓性電源模塊將同步開關(guān)穩(wěn)壓器、電感器、場效應(yīng)晶體管(FETs)、補(bǔ)償和其他無源組件集成到單一封裝中。通過仔細(xì)選擇包括電感器在內(nèi)的板載組件,電源模塊在寬電壓輸入和溫度范圍內(nèi)的性能變化最小。在電源模塊內(nèi)集成組件簡化了設(shè)計流程,最大限度地減少了占地面積,提高了可靠性,且縮短了設(shè)計/鑒定過程,從而加快了產(chǎn)品上市速度。

電源模塊因具有充分表征的電氣/熱性能而變得越來越流行。它們可以在大范圍的開關(guān)頻率內(nèi)運(yùn)行,從而可以使用更小的組件,而且組件占地面積<15 mm2,高度<2.0 mm。非隔離電源模塊結(jié)構(gòu)緊湊、效率高,還可提供高負(fù)載電流。

電源模塊對DAQ性能的影響

使用電源模塊具有多種優(yōu)勢,但對DAQ性能影響最大的兩個因素是電磁干擾(EMI)降低和降低的輸出紋波。為了達(dá)到EMI要求和輸出紋波性能,電源設(shè)計師通常會進(jìn)行多塊板的修改。封裝選擇和布局優(yōu)化是減輕EMI和確保輸出紋波較低的其他重要考慮因素。

EMI

依照國際無線電干擾特別委員會(CISPR)11或CISPR 22,滿足EMI要求且留有足夠裕度,對于任何終端設(shè)備的認(rèn)證都很重要。為了減輕EMI,電源模塊采用了各種技術(shù)來優(yōu)化關(guān)鍵回路面積,從而產(chǎn)生較小的電流變化率(di/dt)回路面積。使用屏蔽式電感器進(jìn)一步降低EMI。

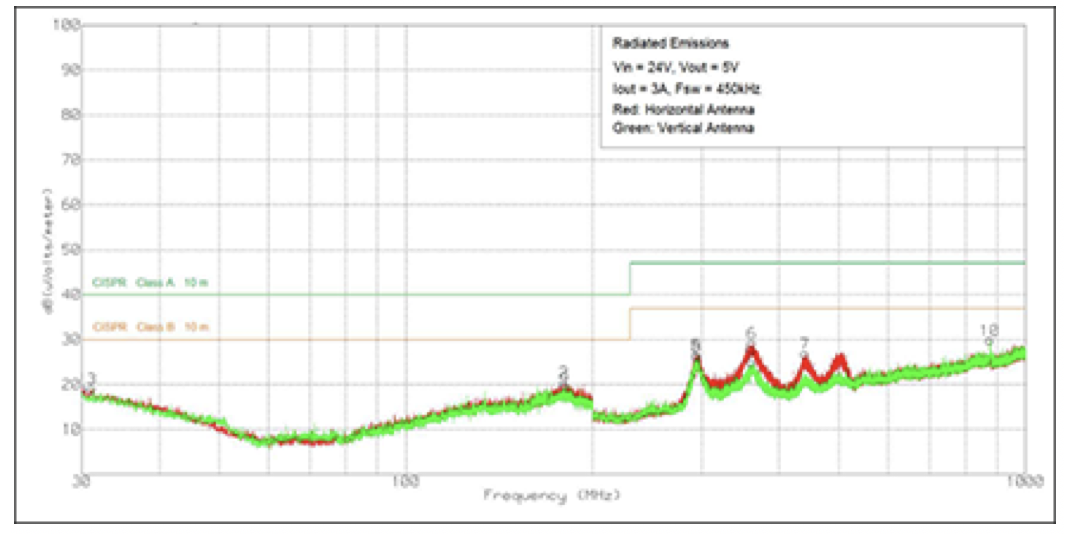

圖2顯示了具有3-A負(fù)載的TI LMZM33603電源模塊的輻射發(fā)射圖。該模塊的輻射發(fā)射低于CISPR的等級A和等級B,因此在認(rèn)證時很容易滿足測試要求。

圖2:LMZM33603的輻射發(fā)射(5V輸出,3A負(fù)載)

為了解電源模塊如何優(yōu)化關(guān)鍵回路面積,讓我們來探究一下組件布局和封裝選擇。

降壓變換器在輸入端產(chǎn)生具有高di/dt的脈動紋波電流。在沒有輸入電容器的情況下,紋波電流由上部電源供給,而循環(huán)紋波電流會導(dǎo)致傳導(dǎo)和輻射EMI的增加。

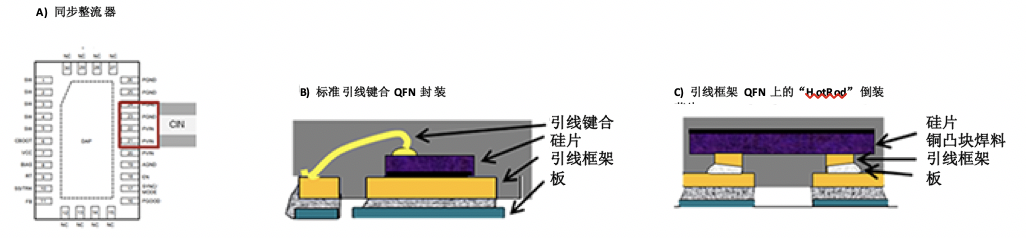

同步開關(guān)DC/DC穩(wěn)壓器在封裝內(nèi)集成了兩個FET,這使得更容易優(yōu)化關(guān)鍵路徑的面積。因集成了兩個FET,所以只有輸入電容器CIN需要進(jìn)行合理的放置。輸入電容器最大限度地減少了輸入電壓紋波,抑制了輸入電壓尖峰,且為設(shè)備提供了穩(wěn)定的系統(tǒng)軌道,從而確保了更低的EMI。CIN放置的簡易取決于封裝技術(shù)和引腳分配。務(wù)必使VIN和PGND引腳彼此靠近。在TI的電源模塊中,我們建議將電容器CIN放置在離VIN和PGND最近的位置,以最大限度地減少關(guān)鍵路徑的面積,如圖3所示。一個小型、低值的電容器Ci被放置在TI的電源模塊內(nèi)部。除了CIN電容器選擇和優(yōu)化關(guān)鍵路徑布局之外,以下討論的電源模塊消息的選擇也有助于提高性能。

四面扁平無管腳(QFN)封裝無外部管腳。管腳長度的不足使得CIN的放置位置更靠近VIN和PGND管腳,從而進(jìn)一步減少了關(guān)鍵路徑的面積。QFN IC封裝內(nèi)部通過細(xì)銅線或金線使得芯片焊盤與管腳外合,增加了寄生電感。

為了進(jìn)一步減小關(guān)鍵路徑的面積,我們的HotRod?技術(shù)完全取代了接合線。翻轉(zhuǎn)芯片,使其有源側(cè)朝下,將銅凸塊沉積在芯片焊盤上并直接焊接到引線框架上。使用銅凸塊代替接合線可以降低串聯(lián)電阻,進(jìn)一步縮小封裝尺寸,并使得CIN更接近VIN和PGND引腳。圖3顯示了QFN和HotRod?封裝。

圖3:A.QFN封裝電容器放置,B.QFN引線鍵合和 C. HotRod?封裝

輸出紋波

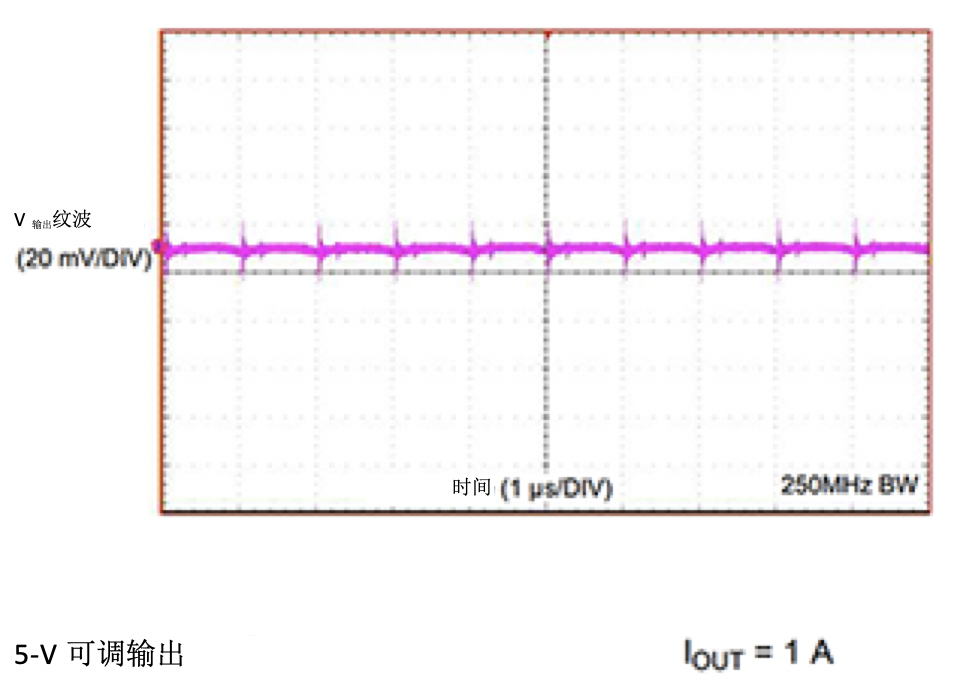

同步降壓DC/DC轉(zhuǎn)換器的輸出級在滿足目標(biāo)紋波電流、輸出紋波電壓和輸出電壓過沖等要求方面起著重要作用。電源模塊的輸出紋波取決于組件選擇、布局和負(fù)載。在我們的電源模塊中,選擇具有低雜散電容和布局優(yōu)化(緊密布局)的電感器,可以確保開關(guān)管腳的最小紋波耦合到輸出管腳VOUT,從而減少DC電壓輸出上的紋波。圖4顯示了電源模塊的紋波(小于5-mV),這使得可以在不改變性能的情況下連接到敏感的模擬電路。

圖4:電源模塊輸出紋波

結(jié)論

TI的電源模塊具有可簡化系統(tǒng)設(shè)計的多種優(yōu)勢,包括:

最小的外部組件。

小尺和高功率密度。

更低的輻射EMI。

更低的操作溫度。

更高的效率和輸出精度。

更快的負(fù)載瞬態(tài)響應(yīng)。

低輸出紋波。

提高的負(fù)載和輸入調(diào)節(jié)。

使用內(nèi)部電感器可以減少磁選工作,并通過屏蔽輻射來提高性能。此外,電源模塊包含廣泛、成熟的保護(hù)機(jī)制,并且需要進(jìn)行更嚴(yán)格的測試(測試次數(shù)比起典型的最終用戶計劃和測試的內(nèi)容要多)。雖然這篇博文只關(guān)注了與提高DAQ性能相關(guān)的優(yōu)勢,但在另一篇博文中,Akshay將介紹使用電源模塊的其他優(yōu)勢。

審核編輯:郭婷

-

電源

+關(guān)注

關(guān)注

184文章

17705瀏覽量

249965 -

集成電路

+關(guān)注

關(guān)注

5387文章

11530瀏覽量

361647 -

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8694瀏覽量

147091 -

ldo

+關(guān)注

關(guān)注

35文章

1940瀏覽量

153310

發(fā)布評論請先 登錄

相關(guān)推薦

非隔離DC/DC電源模塊如何幫助提高DAQ性能

BOSHIDA DC電源模塊的可持續(xù)發(fā)展與環(huán)境保護(hù) DC電源模塊是一種常見的工業(yè)電源設(shè)備

使用DC/DC電源模塊增強(qiáng)電網(wǎng)保護(hù),控制和監(jiān)控設(shè)備的DAQ性能

DC電源模塊短路保護(hù)的機(jī)制

DC電源模塊過壓保護(hù)功能介紹

重要的保護(hù):DC電源模塊短路保護(hù)

DC電源模塊的特點(diǎn)及應(yīng)用案例分享

DC電源模塊的功率調(diào)節(jié)和保護(hù)功能介紹

提升電子設(shè)備性能的秘密:優(yōu)質(zhì)DC電源模塊

使用DC/DC電源模塊增強(qiáng)電網(wǎng)保護(hù),控制和監(jiān)控設(shè)備的DAQ性能

使用DC/DC電源模塊增強(qiáng)電網(wǎng)保護(hù),控制和監(jiān)控設(shè)備的DAQ性能

評論