芯粒(Chiplet)的迷你聯(lián)盟正在整個(gè)行業(yè)中興起,這是由于在緊迫的市場(chǎng)窗口中增加定制化需求以及在硅中得到驗(yàn)證的硬化 IP 組合的推動(dòng)。

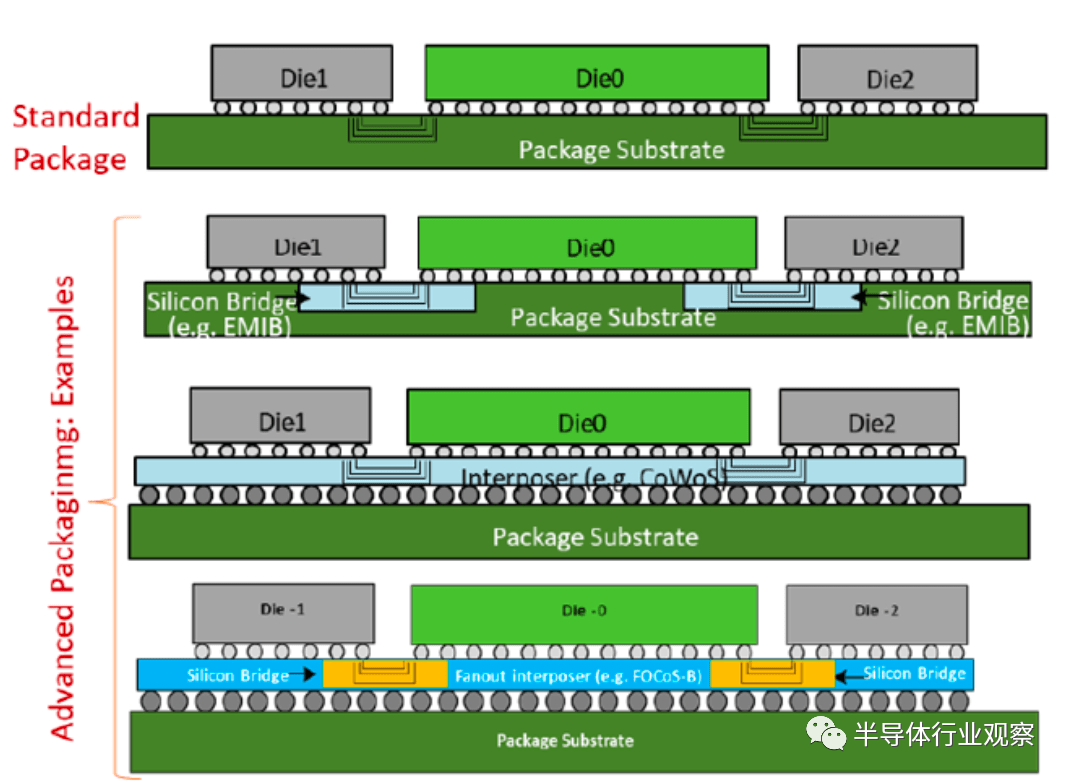

這些松散的合作伙伴關(guān)系正在努力為高度特定的應(yīng)用和終端市場(chǎng)開發(fā)類似樂高積木的集成模型。但它們都是從小規(guī)模開始的,因?yàn)槭聦?shí)證明,很難為可以在各種用例中工作的芯粒創(chuàng)建商業(yè)市場(chǎng)。使用標(biāo)準(zhǔn)化方案連接芯粒是一回事,例如通用芯粒互連高速 (UCIe),或使用英特爾或三星開發(fā)的橋接器。期望它們?cè)诓煌?jì)算負(fù)載和操作條件下的異構(gòu)設(shè)備中工作是另一回事。

圖 1:UCIe 開放芯粒生態(tài)系統(tǒng)

了解不同的芯粒如何相互交互,以及它們?cè)诓煌美碌男袨榉绞剑茈y預(yù)測(cè)。即使使用最好的仿真工具,也沒有足夠的數(shù)據(jù),而且對(duì)于許多應(yīng)用來說可能永遠(yuǎn)如此。但是,除非這些芯粒在其他組件和不同用例的背景下得到充分表征,否則可能會(huì)出現(xiàn)涉及熱管理、各種類型的噪聲、不同的壓力和不一致的老化等問題,所有這些都會(huì)影響現(xiàn)場(chǎng)的可靠性。

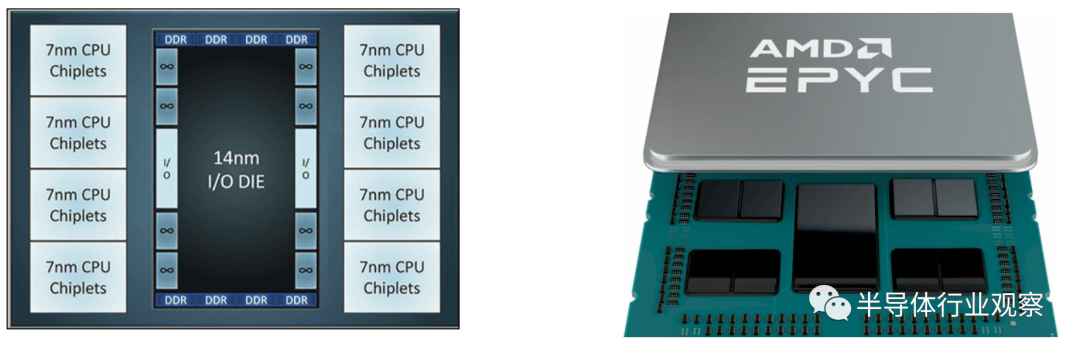

另一方面,芯粒已被證明在受控情況下工作得非常好。十年來,AMD 和 ASE 一直在芯粒和圖形子系統(tǒng)方面進(jìn)行合作。Marvell從 2016 年開始使用芯粒。Intel Foundry Services 正在為基于芯粒的數(shù)據(jù)中心客戶定制系統(tǒng)。

圖 2:AMD 的 EPYC 架構(gòu)集成了不同的工藝技術(shù)

然而,所有這些公司都依賴內(nèi)部采購的芯粒來創(chuàng)建本質(zhì)上是分解的 SoC,他們可以完全控制系統(tǒng)。現(xiàn)在的挑戰(zhàn)是開始開發(fā)芯粒和適合芯粒的架構(gòu),這些架構(gòu)可以在任何供應(yīng)商的設(shè)備上進(jìn)行商業(yè)銷售。

“在某些方面,我們正處于一個(gè)新時(shí)代,”日月光集團(tuán)研究員兼高級(jí)技術(shù)顧問 Bill Chen 說。“優(yōu)化是一種選擇,允許這些選擇對(duì)我們來說很重要。我們也處在一個(gè)開放共享的時(shí)代。芯粒、SiP、異構(gòu)集成,我們從最困難的領(lǐng)域開始,也就是高性能計(jì)算。有兩個(gè)原因。一是這是最需要它的市場(chǎng)部門。其次,這是開發(fā)這些產(chǎn)品的地方,也是解決這些問題的技術(shù)所在。然后我們可以轉(zhuǎn)向通信和其他市場(chǎng),例如可穿戴設(shè)備和醫(yī)療應(yīng)用。”

這就是不同供應(yīng)商開發(fā)的商業(yè)芯粒將適合的地方。但正如處于這一轉(zhuǎn)變前沿的公司將證明的那樣,從不同供應(yīng)商采購芯粒增加了一系列全新的挑戰(zhàn)。即使這個(gè)想法在理論上是有意義的,它也從未實(shí)現(xiàn)過。

小型組織(Small consortia)是真正進(jìn)步的最初跡象。晶圓廠、封裝廠和大型芯片制造商正在與具有深厚領(lǐng)域?qū)I(yè)知識(shí)的合作伙伴合作,使用各種安排來確保各種基本組件協(xié)同工作并可以根據(jù)上下文進(jìn)行表征。桌面上有許多不同的方法,從少數(shù)合作伙伴到基礎(chǔ)更廣泛的基礎(chǔ)設(shè)施,例如連接結(jié)構(gòu)或標(biāo)準(zhǔn)加上嚴(yán)格的設(shè)計(jì)規(guī)則。但對(duì)于所有相關(guān)人員來說,這是一個(gè)謹(jǐn)慎的、邊學(xué)邊做的過程。

“三星電子正在構(gòu)建自己的生態(tài)系統(tǒng),”三星電子知識(shí)產(chǎn)權(quán)和生態(tài)系統(tǒng)營(yíng)銷總監(jiān) Kevin Yee 說。“即便如此,我們也學(xué)到了很多我們沒有想過的事情。從技術(shù)角度來看,chiplet 已經(jīng)存在并得到了驗(yàn)證。但目前,它們都是垂直整合的。因此,芯粒作為一種解決方案存在并且正在發(fā)揮作用。現(xiàn)在的挑戰(zhàn)是芯粒作為市場(chǎng)或業(yè)務(wù)。這就是每個(gè)人都在努力的方向,并且可能會(huì)有一個(gè)臨時(shí)步驟。每個(gè)人都將首先開始構(gòu)建自己的微生態(tài)系統(tǒng),以確保其正常運(yùn)行。所以一家公司會(huì)做一個(gè) I/O 芯片,一個(gè)會(huì)做互連,一個(gè)會(huì)做數(shù)據(jù)芯片。您將確定如何構(gòu)建它以及如何構(gòu)建可行的東西。但最重要的是,您可以在 6 個(gè)不同的計(jì)算芯片或 10 個(gè)不同的 I/O 芯片之間進(jìn)行選擇,選擇您的內(nèi)存芯片,然后將它們放在一起。在那之前,我們還有很長(zhǎng)的路要走。”

同樣,專注于先進(jìn)封裝和芯粒設(shè)計(jì)的 Palo Alto Electron (PAe) 正在率先成立自己的芯粒聯(lián)盟,其中包括 Promex Industries(系統(tǒng)集成)、Thrace Systems(功耗分析)、Palo Alto Electron(先進(jìn)封裝和芯粒設(shè)計(jì)) )、iTest(可靠性和故障分析)、Hyperion(系統(tǒng)級(jí)設(shè)計(jì)、互連和高級(jí)封裝)和 Anemoi Software(熱求解器)。

“這是一個(gè)最低限度的可行生態(tài)系統(tǒng),所有這些公司都在美國(guó),”PAe 首席執(zhí)行官 Jawad Nasrulla 說。“我們說,‘好吧,我們將尋找解決特定技術(shù)問題的小型企業(yè)和創(chuàng)新型初創(chuàng)公司。’ 例如,Anemoi Software 專注于芯粒的熱建模。功率/熱能是進(jìn)行設(shè)計(jì)的關(guān)鍵支持技術(shù)。Palo Alto Electron 擁有構(gòu)建 IC 的經(jīng)驗(yàn),在過去的七年中,我們一直在使用芯粒來做這件事。這些公司中的每一個(gè)都是某個(gè)領(lǐng)域的專家。現(xiàn)在我們需要學(xué)習(xí)如何與彼此合作。”

Promex Industries的首席執(zhí)行官 Dick Otte對(duì)此表示贊同。“這些作品中的每一件都是多管齊下的。每個(gè)人都有一種能力,但每個(gè)人都擁有不到所有可能能力的 100%。所以真正的問題是,當(dāng)我們有工作在這里滾動(dòng)時(shí),會(huì)有多少?我們需要多長(zhǎng)時(shí)間去尋找一些支持或附加功能?到目前為止,這還不是問題。”

正在創(chuàng)建的一些芯粒本身就是模塊或微型系統(tǒng),而不是像特定 I/O 這樣的獨(dú)立 IP,至少已經(jīng)完成了一些集成工作。但隨著商業(yè)芯粒市場(chǎng)的發(fā)展,可能會(huì)有更多針對(duì)特定工作或功能的芯粒,而不是完整的子系統(tǒng)。這可以讓客戶在 chiplet 架構(gòu)中添加可編程性和更多可定制性,而無需更改整體架構(gòu),這類似于英特爾和 Marvell 所走的道路。

“如果你看看小型、中型和大型汽車,每一種都需要完全不同數(shù)量的電子設(shè)備,” Fraunhofer IIS自適應(yīng)系統(tǒng)部工程高效電子部門負(fù)責(zé)人 Andy Heinig 說。“芯粒讓你變得更加靈活。但在未來,您可能能夠?qū)⑿玖=M合在一起以創(chuàng)建更大的芯粒。你可以用這種方式配置你的電子設(shè)備,幾乎就像積木一樣,以獲得你對(duì)汽車的確切需求。”

這需要時(shí)間來發(fā)展。目前,許多 chiplet 制造商正在更高層次上解決這個(gè)問題。

“芯粒被分解成相對(duì)較大的塊,”Promex 的 Otte 說。“這就像芯片設(shè)計(jì)師設(shè)計(jì)了單個(gè)芯片,然后有人必須將所有這些整合在一起并進(jìn)行高級(jí)設(shè)計(jì),不僅要集成芯粒,還要集成您正在使用的任何互連、基板或中介層技術(shù)。第三部分是這個(gè)組裝服務(wù),這是我們的角色。如果這被證明是一個(gè)非常成功的模式,并且我們能夠?yàn)榭蛻籼峁┵|(zhì)量和良好的經(jīng)濟(jì)效益,那么它就有可能像滾雪球一樣滾雪球并成為一項(xiàng)主要活動(dòng),我們將陷入更困難的問題,我們有一個(gè)許多項(xiàng)目在不同的州進(jìn)行。這意味著不同種類的協(xié)調(diào)。現(xiàn)在的問題是尋找客戶。稍后,將是零件的交付。”

01 重新思考老問題

多年來,整個(gè)芯片行業(yè)的普遍共識(shí)是,業(yè)務(wù)關(guān)系將是 chiplet 市場(chǎng)運(yùn)作的一大障礙。然而,正如這些小型組織的努力所表明的那樣,也存在許多技術(shù)挑戰(zhàn)。雖然這些組織通常會(huì)選擇一個(gè)“總承包商”來監(jiān)督設(shè)計(jì)到制造流程的各個(gè)方面,但已經(jīng)涉及很多步驟,隨著芯粒變得更有針對(duì)性和功能更窄,還會(huì)有更多步驟。

“當(dāng)你做芯粒時(shí),心態(tài)必須改變,”Yee 說。“很多人仍然認(rèn)為這就像構(gòu)建 SoC。你現(xiàn)在真的在構(gòu)建一個(gè)完整的系統(tǒng)。我怎么跟它說話?如何配置計(jì)算芯片?我必須有哪些邊帶信號(hào)?需要考慮固件。您是否設(shè)置為使用該固件并啟動(dòng)他們的計(jì)算芯片?現(xiàn)在有很多系統(tǒng)級(jí)的討論涉及人們以前沒有真正考慮過的問題。”

即使選擇正確的封裝也是一個(gè)挑戰(zhàn)。“你有這么多不同的口味,” Synopsys的 IP 產(chǎn)品線高級(jí)組總監(jiān) Michael Posner 說。“你會(huì)想,‘哦,你應(yīng)該能夠?qū)⒚恳粋€(gè)都放在一個(gè)盒子里,也許可以想出一個(gè)適用于所有這些的單一 IP,但事實(shí)并非如此。你有不同的凸點(diǎn)間距、不同的性能和功率、不同的寄生效應(yīng)和電源完整性問題。因此,不像我們傳統(tǒng)上為 IP 做的那樣,每個(gè)節(jié)點(diǎn)都有一個(gè)過孔,可能是南北或東西方向,我們最終有一個(gè)用于高級(jí),一個(gè)用于標(biāo)準(zhǔn),一個(gè)用于 RDL,因?yàn)榧夹g(shù)的變化。我們需要在整個(gè)生態(tài)系統(tǒng)中開發(fā)的 IP 數(shù)量呈爆炸式增長(zhǎng),目前還沒有明確的領(lǐng)導(dǎo)者。”

02 一些舊的東西,一些新的東西

當(dāng)然,并非所有這些都是新的。使用先進(jìn)封裝的 OSAT 和代工廠至少解決了一些挑戰(zhàn),例如如何處理芯粒、如何確保這些芯片是KGD,以及各種互連方案,例如混合鍵合或微凸塊。在 2.5D 實(shí)現(xiàn)中,HBM主要用作可與許多不同配置配合使用的芯粒。

“三星的封裝技術(shù)在為三星代工廠提供完整解決方案方面具有顯著優(yōu)勢(shì),”Yee 說。“該團(tuán)隊(duì)從其在內(nèi)存封裝方面的領(lǐng)導(dǎo)地位中學(xué)到的東西可以應(yīng)用于代工。HBM 是存儲(chǔ)器領(lǐng)導(dǎo)地位的一個(gè)很好的例子,封裝中的多芯片使代工芯粒成為可能。當(dāng)我們轉(zhuǎn)向芯粒時(shí),您無法將制程和設(shè)計(jì)與封裝分開。他們將齊頭并進(jìn)。當(dāng)人們想到芯粒時(shí),他們假設(shè)您將能夠直接運(yùn)行一個(gè)到另一個(gè)的連接。一般來說,這會(huì)奏效。實(shí)際上,如何路由慢跑或偏移?你有多少保證金?通過我們的測(cè)試車輛,我們正在進(jìn)行測(cè)試以確定實(shí)際的路由路徑,以確保高信號(hào)質(zhì)量。”

還有一些行之有效的連接芯粒的方法,例如 UCIe、線束 (BoW)、硅中介層、橋接器,甚至混合鍵合。將來,這些方法中的一種以上可能會(huì)用于復(fù)雜的設(shè)計(jì),從而為更多創(chuàng)新打開大門。

例如,Eliyan 是一家開發(fā)芯粒互連的初創(chuàng)公司,它專注于通過在芯粒的兩側(cè)構(gòu)建物理互連層 (PHY) 來消除 UCIe 兼容設(shè)計(jì)中的中介層。“這消除了制造、熱管理的任何復(fù)雜性,并使我們能夠儲(chǔ)存我們從舊的 MCM(多芯片模塊)時(shí)代學(xué)到的所有東西,”該公司聯(lián)合創(chuàng)始人兼業(yè)務(wù)主管 Patrick Soheili 說。“我們計(jì)劃以我們的技術(shù)為基礎(chǔ)構(gòu)建一堆芯粒。所以我們會(huì)在一端使用我們的技術(shù),在另一端使用一些其他東西,并將兩個(gè)、三個(gè)或四個(gè)東西連接在一起。也許它們是 HBM 設(shè)備,也許它們是其他 I/O 控制器。”

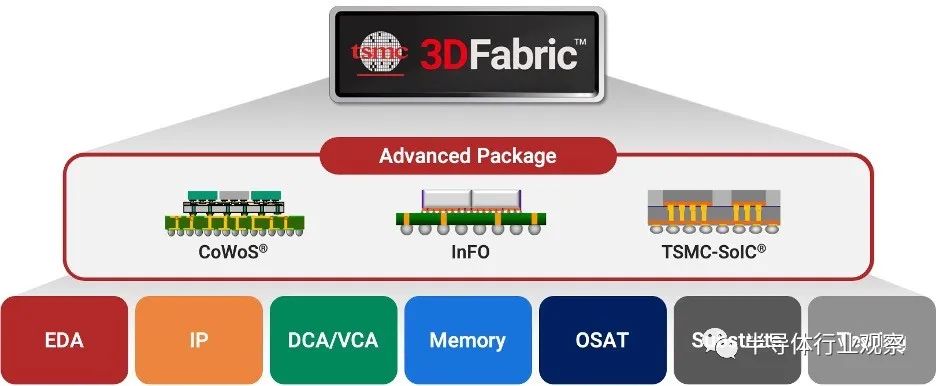

將設(shè)備連接在一起的可能方案的數(shù)量正在迅速增長(zhǎng)。去年秋天,臺(tái)積電推出了 3D Fabric Alliance,以在 3D 封裝中連接不同的層和設(shè)備。“我們擁有 EDA、IP 和設(shè)計(jì)服務(wù),我們還在增加內(nèi)存合作伙伴、幫助我們組裝這些設(shè)備的 OSAT 以及在 3D 中變得極其重要的基板,”臺(tái)積電的總監(jiān) Dan Kochpatcharin 說。設(shè)計(jì)基礎(chǔ)設(shè)施管理部。“這些設(shè)備可以有 10 厘米高,基板可以有 20 層或更多層。所以我們需要確保我們將他們的路線圖與我們的路線圖對(duì)齊,以便我們可以與他們進(jìn)行交互,也許會(huì)有不同的材料一起工作。然后你必須考慮測(cè)試整個(gè)系統(tǒng),這并不容易。所以我們正在與 Advantest 和 Teradyne 合作,以及 EDA 供應(yīng)商。IP 在測(cè)試中很重要,因?yàn)槲覀冃枰槍?duì)可靠性進(jìn)行設(shè)計(jì)。”

圖 3:TSMC 的 3DFabric 生態(tài)系統(tǒng)模型

而這只是出現(xiàn)的一些通用集成方案的開始。在這個(gè)市場(chǎng)被整理出來之前還會(huì)有更多的東西,并且會(huì)有越來越多的證據(jù)表明什么有效,什么無效,以及一些從未被考慮過的新問題。例如,芯粒的不均勻老化會(huì)導(dǎo)致各種以前從未解決過的可靠性問題,特別是在預(yù)計(jì)設(shè)備可以多年保持功能的市場(chǎng)中。因此,隨著芯粒和封裝經(jīng)濟(jì)的發(fā)展,一個(gè)領(lǐng)域的成本節(jié)省可能會(huì)被另一個(gè)領(lǐng)域的成本增加所抵消,而隨著芯粒模型的發(fā)展,客戶今天支付的成本可能會(huì)變得不那么有吸引力。

Amkor Technology高級(jí)工程師 Nathan Whitchurch 表示:“我們看到越來越多的客戶決定接受 TIM(熱界面材料,只是為了讓他們的設(shè)備能夠正常工作)的成本。”那是行不通的。過去奇特的東西變得越來越不那么奇特了,比如燒結(jié)銀類別,你最終會(huì)在蓋子和芯片之間形成非常堅(jiān)硬、高導(dǎo)熱性的銀合金基體。另一種會(huì)更軟”

03 結(jié)論

芯粒是合乎邏輯的下一步,因?yàn)閷?duì)于大多數(shù)芯片制造商來說,將所有東西縮小并塞進(jìn)單個(gè) SoC 的成本變得不經(jīng)濟(jì)。這讓業(yè)界很多人都在考慮下一步,并且能夠至少標(biāo)準(zhǔn)化軟件包中的某些組件以創(chuàng)建定制解決方案是實(shí)現(xiàn)大規(guī)模定制的合乎邏輯的方法。

如果這種方法成功,它可能會(huì)改變?cè)O(shè)備進(jìn)入市場(chǎng)的方式,同時(shí)允許以低得多的價(jià)格進(jìn)行更多定制。因此,新架構(gòu)的巨大性能提升將在更多的利基市場(chǎng)中出現(xiàn),而無需從頭開發(fā) ASIC 或 SoC 的沉重代價(jià)。如果可以將一些自定義芯粒添加到架構(gòu)中,那么適用于 80% 市場(chǎng)的產(chǎn)品可能仍會(huì)對(duì)其他 20% 的市場(chǎng)產(chǎn)生巨大好處。但是有很多細(xì)節(jié)需要先解決,芯片行業(yè)正在弄清楚這些細(xì)節(jié)。這些小型聯(lián)盟是找出問題所在、可以標(biāo)準(zhǔn)化的內(nèi)容以及領(lǐng)域?qū)I(yè)知識(shí)將在此過程中扮演什么角色的第一步。

審核編輯 :李倩

-

amd

+關(guān)注

關(guān)注

25文章

5466瀏覽量

134107 -

芯片行業(yè)

+關(guān)注

關(guān)注

1文章

28瀏覽量

7880 -

chiplet

+關(guān)注

關(guān)注

6文章

431瀏覽量

12587

原文標(biāo)題:Chiplet的通用,遙遙無期

文章出處:【微信號(hào):算力基建,微信公眾號(hào):算力基建】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Cadence推出基于Arm的系統(tǒng)Chiplet

Chiplet技術(shù)有哪些優(yōu)勢(shì)

2035年Chiplet市場(chǎng)規(guī)模將超4110億美元

IMEC組建汽車Chiplet聯(lián)盟

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺(tái)

創(chuàng)新型Chiplet異構(gòu)集成模式,為不同場(chǎng)景提供低成本、高靈活解決方案

蘿卜出租,在AI的服務(wù)中被AI取代

自動(dòng)駕駛雷達(dá)15W高導(dǎo)熱絕緣片

自動(dòng)駕駛激光雷達(dá)及非硅15W高導(dǎo)熱絕緣氮化硼材料介紹

Chiplet是否也走上了集成競(jìng)賽的道路?

什么是Chiplet技術(shù)?

Chiplet技術(shù)對(duì)英特爾和臺(tái)積電有哪些影響呢?

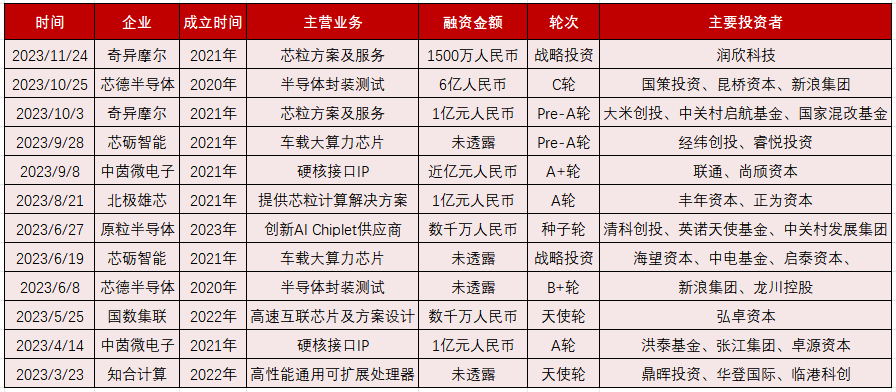

2023年Chiplet發(fā)展進(jìn)入新階段,半導(dǎo)體封測(cè)、IP企業(yè)多次融資

Chiplet的通用,遙遙無期

Chiplet的通用,遙遙無期

評(píng)論