本章節主要介紹一些簡單的時序約束的概念,主要包括:

四種時序路徑

時序路徑的約束語句

輸入轉換時間與電容輸出負載模型

時序約束文件的簡單編寫

關鍵詞:create_clock、 set_clock_uncertainty、 set_clock_latency、 set_clock_transition、 set_input_delay、 set_ouput_delay、 remove_input_delay、 report_clock、set_load、 set_input_ transition、 set_driving_cell

該章節在 DC 綜合流程中的位置如下。

4 種時序路徑

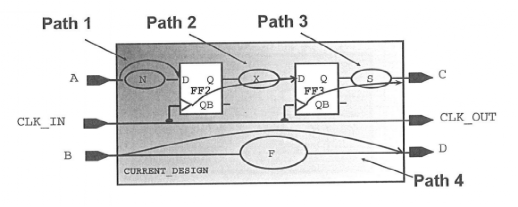

DC 進行時序分析時,都是基于同步時鐘下的設計。 假設數據都在時鐘上升沿到來 (launch) 或輸出,則 DC 會將設計分割成 4 種時序路徑,如下圖所示:

Path1 指輸入到寄存器的時序路徑 (Input-to-Reg Path)

Path2 指寄存器到寄存器的時序路徑 (Reg-to-Reg Path)

Path3 指寄存器到輸出的時序路徑 (Reg-to-Output Path)

Path4 指輸入到輸出的時序路徑 (Input-to-Output Path)

這些路徑的起點和終點必須是固定的類型,說明如下:

起點必須是非時鐘的輸入端 (input port other than a clock port),或觸發器 (寄存器) 的時鐘端。

終點必須是非時鐘的輸出端 (output port other than a clock port),或時序元件的非時鐘輸入端 (例如觸發器的 D 端)。

正常的靜態時序分析 (Static Timing Analysis, STA) 主要包括 3 個步驟:

1> 將設計分割成多個時序路徑

2> 計算每條時序路徑的延時

3> 時序路徑和數據到達時間 (arrival times) 做對比,判斷時序約束是否滿足 (meet)

Reg-to-Reg Path 約束

時序約束時,時鐘的下降沿只有在雙邊沿時鐘設計中才會起作用。 所以一般設計的時序約束都與時鐘上升沿相關。

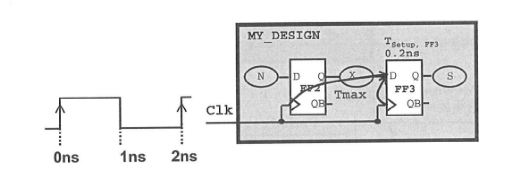

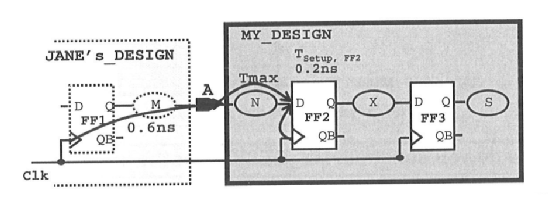

假設一個含有 Reg-to-Reg Path 的設計示意圖如下:

此設計中,時鐘周期 2ns,setup 為 0.2ns,則 FF2 的 clock 端到 FF3 的 D 端的最大延遲為:

Tmax = 2ns-0.2ns = 1.8ns

那么最簡單的時鐘約束可以編寫為:

create_clock [get_ports Clk] -name sys_clk \\

-period 2 -waveform "0 1"

create_clock : DC Memory 中創建 clock 的命令 ;

[get_ports Clk] : 為創建的 clock 指定對應設計中的源 clock,源 clock 不一定是頂層模塊中的 clock ,也可以是子模塊中的 clock ;

-name sys_clk : 將創建的 clock 命名為 sys_clk,可以省略 ;

-period 2 : 指定創建的 clock 周期為 2ns ;

-waveform "0 1" : 表示時鐘上升沿時刻為 0ns、下降沿時刻為 1ns,以此循環,間接指定了占空比。 此選項也可以省略,則創建的時鐘默認占空比為 50% 。

clock 模型

關于時鐘的基本概念,歡迎參考《Verilog 教程高級篇》中《5.2 時鐘簡介》一節。

時鐘樹綜合 (Clock Tree Synthesis, CTS) 一般發生在 DC 之后的布局布線階段。 DC 階段不進行時鐘樹綜合,不允許插入緩沖單元 (buffer)。 此時時鐘網絡認為是理想的,且具有無限驅動能力。

例如上述創建的 clock 模型中,時鐘特性如下:

上升沿、下降沿轉換時間為 0

時鐘偏移為 0

時鐘延遲為 0

但是還是建議在 DC 階段對 clock 進行建模,估算時鐘的各種特性,也為布局布線時的時鐘樹綜合留有時間裕量。 時鐘特性的建模主要包括:時鐘偏移、時鐘延遲與時鐘轉換時間的估算模擬。

時鐘偏移建模

時鐘偏移模型通過設置時鐘的不確定度來描述。 時鐘的不確定度參數,也包含了時鐘抖動 (jitter)、裕量 (margin) 等參數信息。

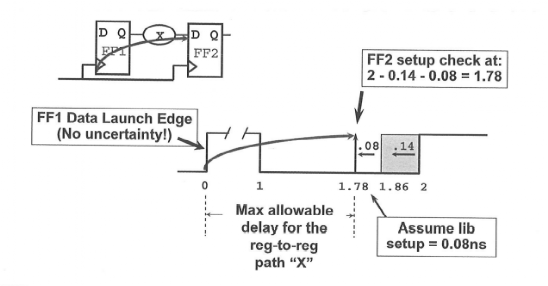

假設某個設計示意圖如下,時鐘偏移量為 0.14ns,建立時間為 0.08ns,則時鐘不確定度的設置描述如下:

create_clock [get_ports Clk] -name sys_clk -period 2

# -setup 0.14 表示時鐘偏移設置為 0.14

set_clock_uncertainty -setup 0.14 [get_clocks sys_clk]

FF1 到 FF2 的最大延遲,即 FF2 的建立時間的檢查時刻為:

2 - 0.14 - 0.08 = 1.78ns

設置時鐘不確定度時,也可以指定不同的時鐘域 (clock domain) :

set_clock_uncertainty -setup 0.14 \\

-from [get_clocks clk1] -to [get_clock clk2]

時鐘延遲建模

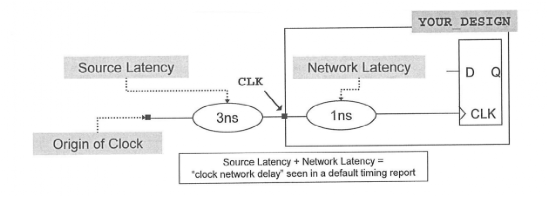

時鐘延遲模型分為 2 種:時鐘網絡延遲 (network latency) 與時鐘源延遲 (source latency)。

時鐘網路延遲模型定義了從 clock port 或 pin 端 (create_clock 時指定的點) 到寄存器 clock 端的延遲。 時鐘源延遲定義了實際時鐘原點 (clock origin) 到 clock port 或 pin 端的延遲。 示意圖如下:

如上圖所示,假設時鐘周期為 10ns,source latency 為 3ns,network latency 為 1ns,則時鐘延遲的設置描述如下:

create_clock -period 10 [get_ports CLK]

# -source 指設定 source latency,不指定時設置 network latency

set_clock_latency -source -max 3 [get_clocks CLK]

set_clock_latency -max 1 [get_clocks CLK]

set_clock_latency 命令表示設置時鐘的 latency 屬性,指定 -source 選項時表示設置 source latency,不指定時表示設置 network latency。 -max 表示指定延遲最大值,當然也可以使用 -min 表示指定時鐘延遲最小值。

布局布線階段,時鐘樹綜合之后的具有一定實際延遲的時鐘稱為 propagated clock。 DC 階段不進行 CTS,所以需要設置 network latency 。 布局布線階段的 CTS 之后,時鐘樹具有實際的 latency,此時設置 network latency 的語句要改成:

# 布局布線時,network latency 需要設置實際的 propagated clock

# set_clock_latency -max 1 [get_clocks CLK]

set_propagated_clock [get_ports CLK]

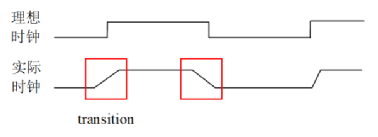

時鐘轉換時間建模

時鐘從上升沿跳變到下降沿,或者從下降沿跳變到上升沿時,并不是"直上直下" 的完成電平跳變,而是 "斜坡式" 需要一個過渡時間完成電平跳變。 這個過渡時間稱之為時鐘的轉換時間 (transition),示意圖如下。

假設某一設計中時鐘的轉換時間最大值為 0.1ns,則 clock transition 的設置語句描述如下:

set_clock_transition -max 0.1 [get_clocks CLK]

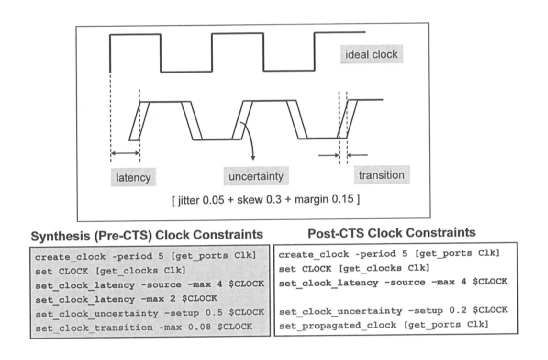

時鐘模型小結

下圖顯示了時鐘不確定度、時鐘延遲、時鐘轉換時間的示意圖,以及在 DC 和布局布線階段的設置差異性。

uncertainty、latency 以及 transition 等時鐘特性影響的是時序路徑的長度。 latency 作用于所有的時序路徑,所以時序分析時會產生一種“抵消”的效果,不影響時序分析結果 (下一節介紹)。

工程設計時,往往使用 uncertainty 與 margin (時間裕量) 來進行時鐘建模,避免繁瑣的設置,也能為布局布線時的 CTS 留有一定的時長調節范圍。

例如,帶有 margin 和 uncertainty 的時鐘模型描述如下:

set UNCERTAINTY 0.3

# 留有 30% 的裕量,作用在時鐘周期上

set MARGIN 0.3

set PERIOD 10

create_clock [get_ports CLK] -period [expr $PERIOD*(1-$MARGIN)]

# 時鐘模型只設置不確定度參數

set_clock_uncertainty -setup $UNCERTAINTY [get_clocks CLK]

-

寄存器

+關注

關注

31文章

5397瀏覽量

122648 -

約束

+關注

關注

0文章

82瀏覽量

12875 -

時序約束

+關注

關注

1文章

117瀏覽量

13569 -

時序路徑

+關注

關注

0文章

12瀏覽量

1434 -

同步時鐘

+關注

關注

0文章

59瀏覽量

3386

發布評論請先 登錄

相關推薦

VIVADO時序約束及STA基礎

FPGA時序約束的基礎知識

FPGA主時鐘約束詳解 Vivado添加時序約束方法

FPGA時序約束之衍生時鐘約束和時鐘分組約束

時序約束的相關知識(二)

評論