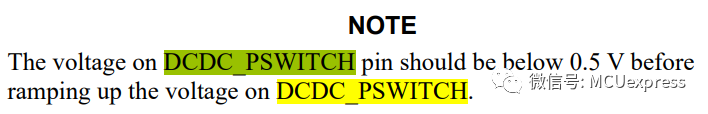

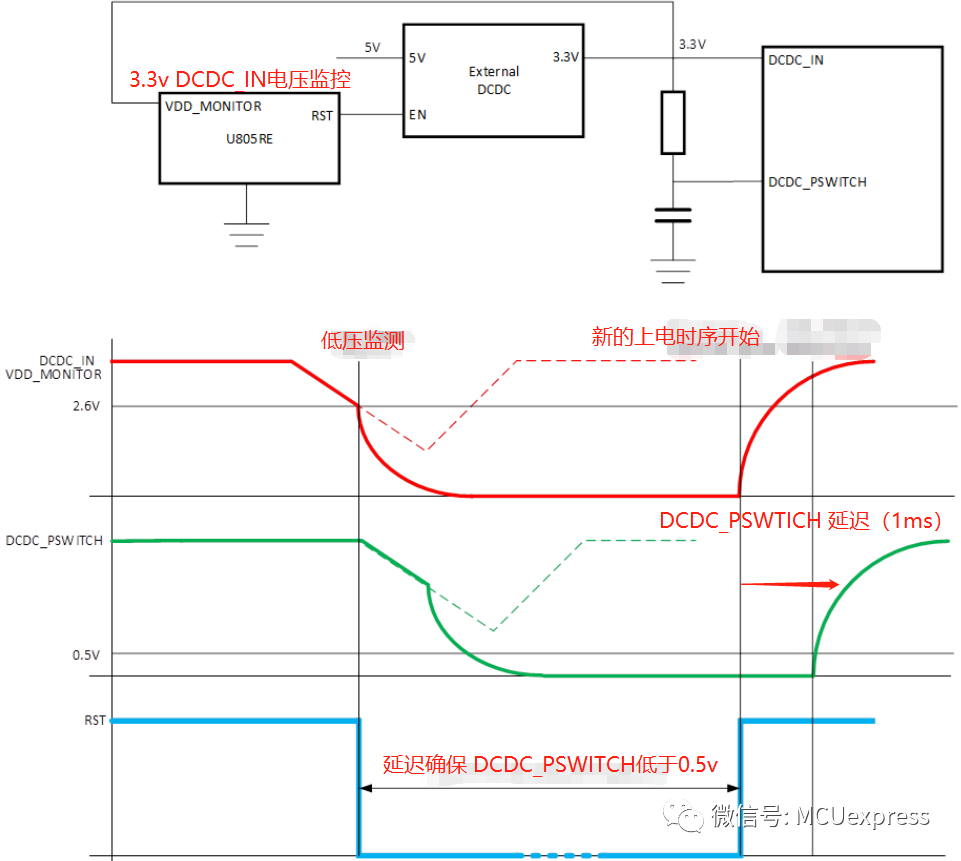

在 DCDC_PSWITCH引腳電壓向上提升的過程中,DCDC_PSWITCH引腳上之前的電壓應低于 0.5 V。無論是上電復位,還是 SNVS低功耗喚醒復位情況下都應該保證這點。當主電源復位足夠快時,DCDC_PSWITCH將不會延遲所需的最小1ms,從而導致DCDC_OUT無法正確打開。

記錄一次在 SNVS低功耗模式下,外部主機端串口或者 CAN總線以1ms-100ms的間隔不間斷的發送讓 MIMXRT1170進入睡眠指令,MIMXRT1170收到后立刻進入 SNVS模式,進入SNVS模式后VDD_SOC_IN和DCDC_PSWITCH引腳電壓跌落到0V,Wakeup 引腳被上拉到高電平,此時需通過Wakeup腳執行下降沿操作喚醒系統。

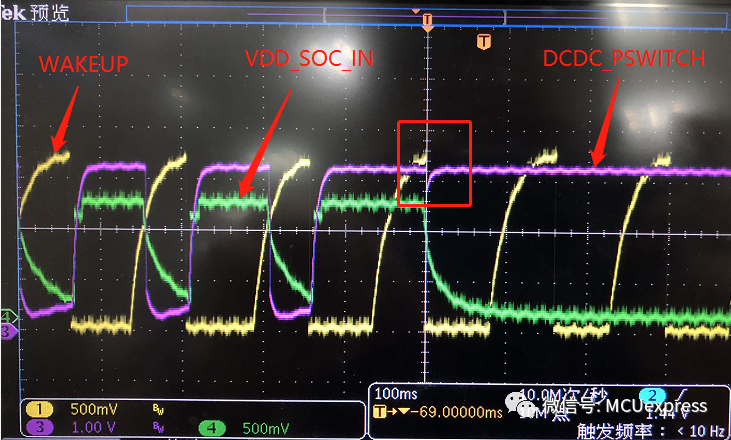

在 Wakeup引腳(黃色線)下降沿喚醒后,正常情況是 DCDC_PSWTICH由低電平到高的變化,VDD_SOC內核電壓輸出穩定的 1.1v電壓。如下是一次啟動異常的波形,發現DCDC_PSWITCH(紫色線)的電壓沒有降低到 0.5v以下,然后就迅速被拉升到3.3v。此時綠色線的 VDD_SOC_IN引腳電壓并沒有拉升到 1.1v,而是一直維持低電平,這種情況下無論怎么按復位鍵都不能正常啟動系統,需對系統重新拔電上電才可重新啟動。

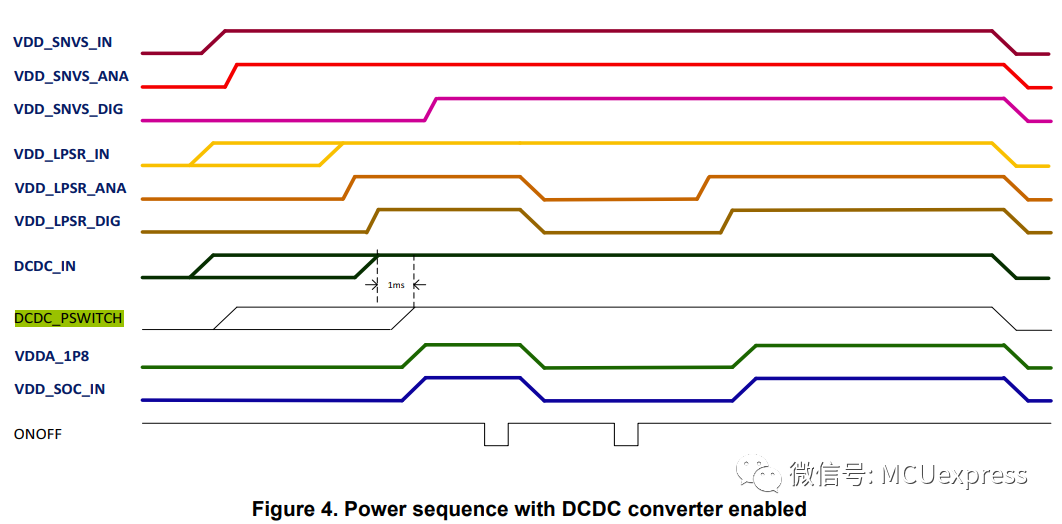

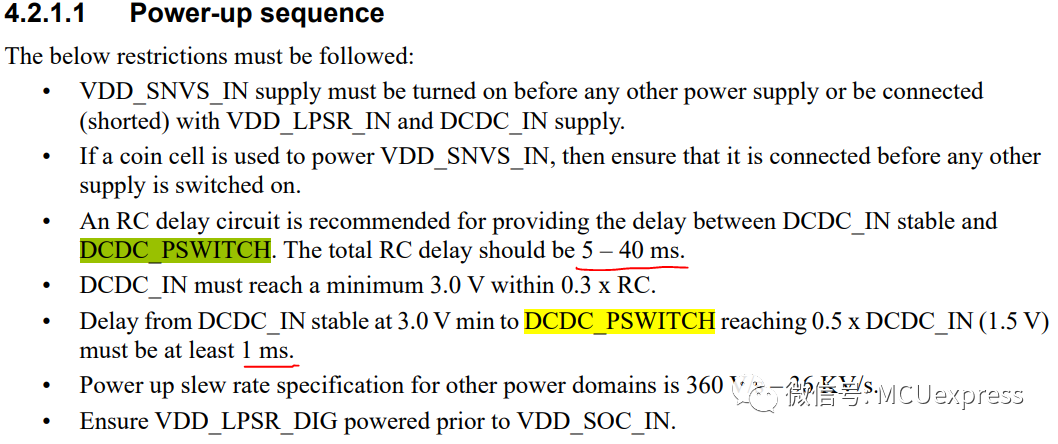

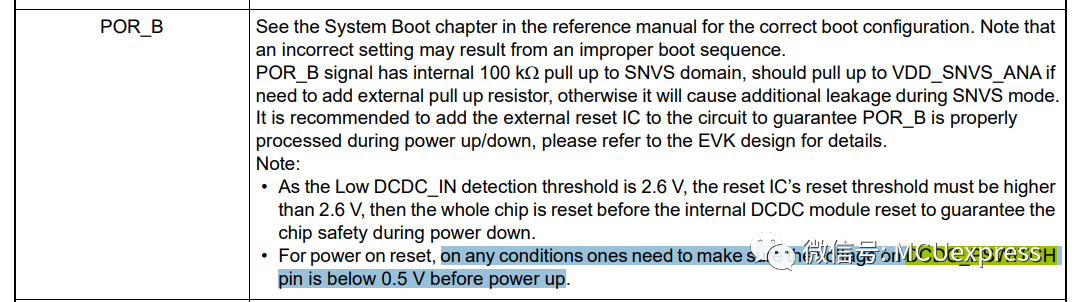

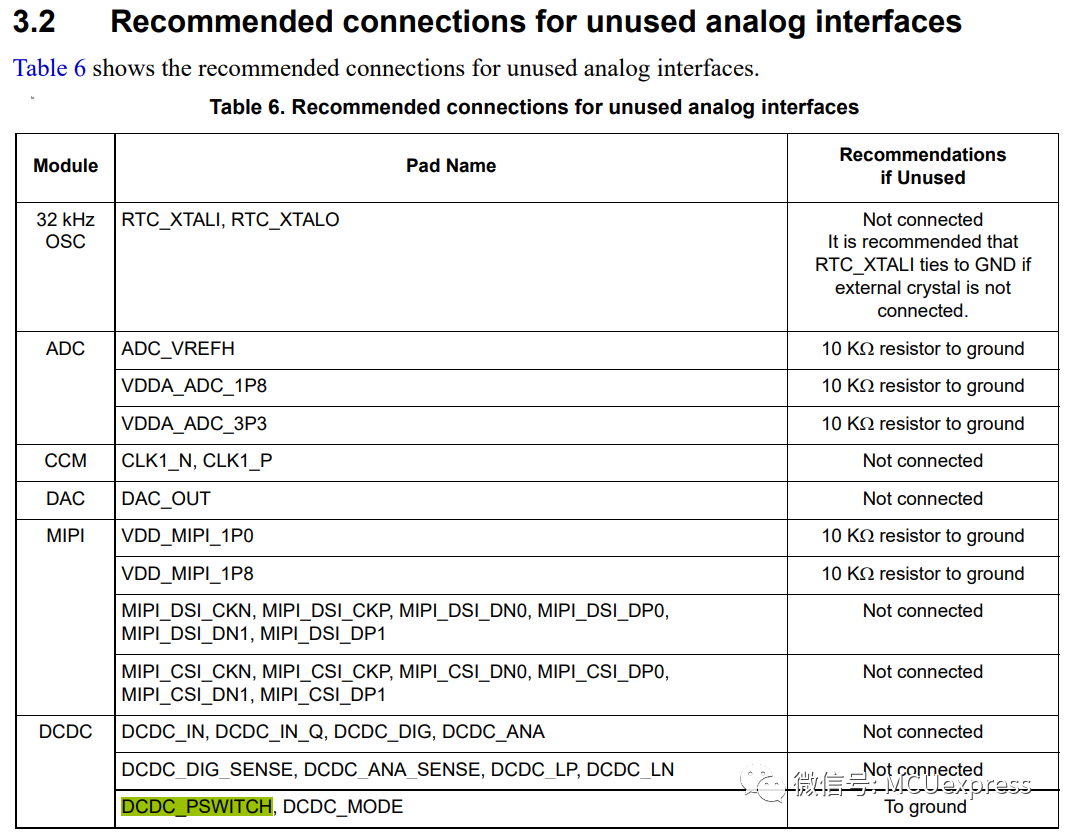

針對內部 DCDC使能的場景,手冊中特別重要的幾點提示:

????

????

要啟用 DCDC功能,請在 DCDC_IN上升沿后至少延遲1ms后再讓DCDC_PSWITCH生效。

從DCDC的設計這塊要求來看,只需要確保DCDC_PSWITCH電壓低于0.5V,而沒有要求DCDC_IN 一定跌落到0.5V。

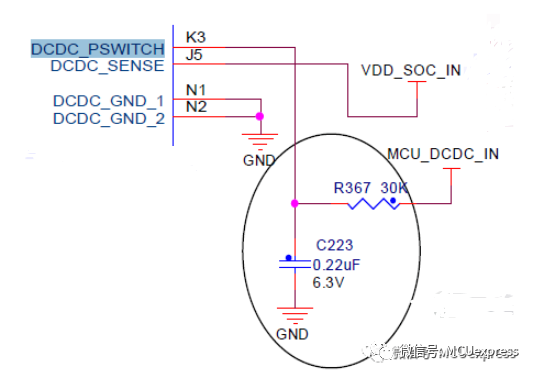

官方開發板 EVK上面的RC時間是30kohm x 0.22uF = 6.6ms。

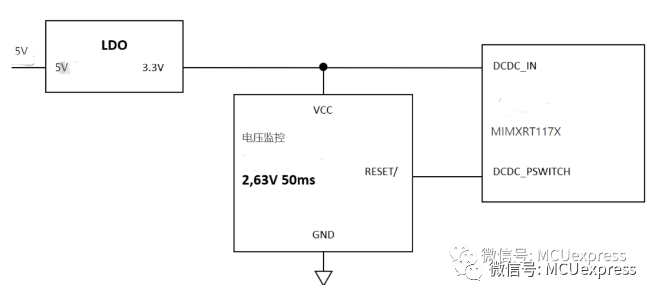

解決方案:電壓監測是解決這一問題的合適方案。使用具有延遲復位輸出的電壓監測電路(例如UM805RE)。該電路監測主MIMXRT117X 3.3V電源電壓(外部5V至3.3V DCDC)。

當輸出電壓降至2.63V以下(器件UM805RE)時,它會產生一個復位信號(它將復位輸出拉低),用于特定的延遲(必須將該延遲視為足以釋放 DCDC_PSWITCH兩端的電容電荷,這意味著在該延遲時間內,DCDC_PSWITCH處的電壓必須低于0.5V)。

該電壓監測的復位輸出連接到外部 DCDC的使能輸入,這意味著在整個復位延遲間隔期間,DCDC 3.3V輸出被禁用。在此間隔期間,必須實現 DCDC_PSWITCH 低于0.5V。

那么直接使用如下電壓復位監測芯片直接控制 DCDC_PSWITCH引腳是否可以呢?

這個只執行了單一功能:每當 VCC電源電壓降至預設閾值以下時,它們就會復位信號,并在 VCC上升至復位閾值以上后將其保持有效至少幾毫秒。不推薦電壓監測直接控制 DCDC_PSWITCH,因為必須遵守上電順序。DCDC_PSWITCH延遲的總 RC應為5-40ms。電壓監測的復位應為電源的啟用信號,因此當發生這種情況時,這將給電容足夠的時間在上電啟動之前放電。

還有一種電路是旁路 DCDC的使用辦法,使用 NXP推薦的外部電源 PMIC,PF5020對應 MIMXRT1170的電源供電芯片,這樣就可以旁路內部的 DCDC電路,推薦的接法如下。

審核編輯:劉清

-

soc

+關注

關注

38文章

4163瀏覽量

218173 -

DCDC

+關注

關注

29文章

814瀏覽量

71263 -

低電平

+關注

關注

1文章

115瀏覽量

13269 -

VDD

+關注

關注

1文章

311瀏覽量

33191

原文標題:MIMXRT1170 上電DCDC_PSWTICH啟動異常波形分析

文章出處:【微信號:嵌入式 MCU,微信公眾號:嵌入式 MCU】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MIMXRT1170上電DCDC_PSWTICH啟動波形異常

MIMXRT1170上電DCDC_PSWTICH啟動波形異常

評論