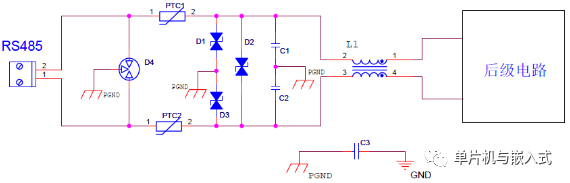

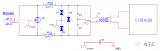

上圖是RS485接口防雷電路,接口電路設計概述:

RS485用于設備與計算機或其它設備之間通訊,在產品應用中其走線多與電源、功率信號等混合在一起,存在EMC隱患。

本方案從EMC原理上,進行了相關的抑制干擾和抗敏感度的設計,從設計層次解決EMC問題。

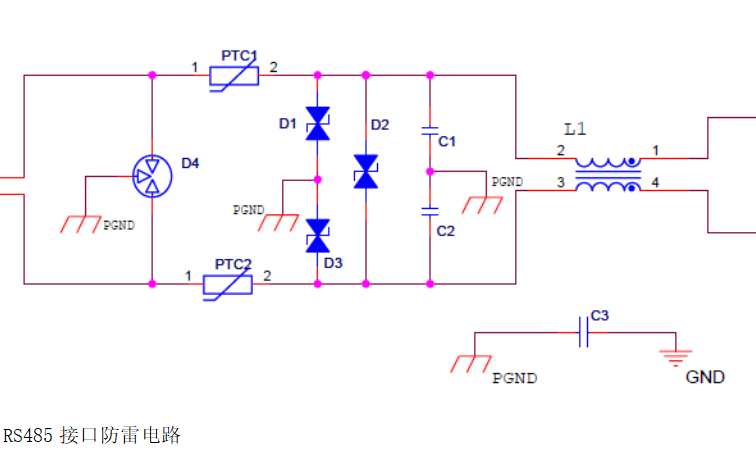

電路EMC設計說明

電路濾波設計要點

L1為共模電感,共模電感能夠對衰減共模干擾,對單板內部的干擾以及外部的干擾都能抑制,能提高產品的抗干擾能力,同時也能減小通過429信號線對外的輻射,共模電感阻抗選擇范圍為120Ω/100MHz ~2200Ω/100MHz,典型值選取1000Ω/100MHz。

C1、C2為濾波電容,給干擾提供低阻抗的回流路徑,能有效減小對外的共模電流以同時對外界干擾能夠濾波;電容容值選取范圍為22PF~1000pF,典型值選取100pF;若信號線對金屬外殼有絕緣耐壓要求,那么差分線對地的兩個濾波電容需要考慮耐壓。

當電路上有多個節點時要考慮降低或去掉濾波電容的值。C3為接口地和數字地之間的跨接電容,典型取值為1000pF, C3容值可根據測試情況進行調整。

電路防雷設計要點

為了達到IEC61000-4-5或GB17626.5標準,共模6KV,差模2KV的防雷測試要求,D4為三端氣體放電管組成第一級防護電路,用于抑制線路上的共模以及差模浪涌干擾,防止干擾通過信號線影響下一級電路

氣體放電管標稱電壓VBRW要求大于13V,峰值電流IPP要求大于等于143A

峰值功率WPP要求大于等于1859W

PTC1、PTC2為熱敏電阻組成第二級防護電路,典型取值為10Ω/2W

為保證氣體放電管能順利的導通,泄放大能量必須增加此電阻進行分壓,確保大部分能量通過氣體放電管走掉

D1~D3為TSS管(半導體放電管)組成第三級防護電路,TSS管標稱電壓VBRW要求大于8V,峰值電流IPP要求大于等于143A;峰值功率WPP要求大于等于1144W

接口電路設計備注

如果設備為金屬外殼,同時單板可以獨立的劃分出接口地,那么金屬外殼與接口地直接電氣連接,且單板地與接口地通過1000pF電容相連。

如果設備為非金屬外殼,那么接口地PGND與單板數字地GND直接電氣連接。

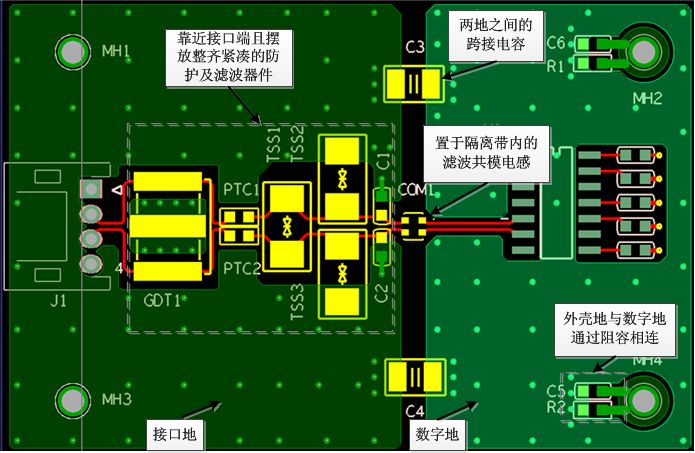

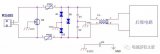

RS485接口電路布局

上圖是RS485接口濾波及防護電路布局。

方案特點:

防護器件及濾波器件要靠近接口位置處擺放且要求擺放緊湊整齊,按照先防護后濾波的規則,走線時要盡量避免走線曲折的情況

共模電感與跨接電容要置于隔離帶中

方案分析:

接口及接口濾波防護電路周邊不能走線且不能放置高速或敏感的器件

隔離帶下面投影層要做掏空處理,禁止走線

RS485接口電路分地設計

方案特點:

為了抑制內部單板噪聲通過RS485接口向外傳導輻射,也為了增強單板對外部干擾的抗擾能力,在RS485接口處增加濾波器件進行抑制,以濾波器件位置大小為界,劃分出接口地

隔離帶中可以選擇性的增加電容作為兩者地之間的連接,電容C4、C5取值建議為1000pF,信號線上串聯共模電感CM與電容濾波,并與接口地并聯GDT和TVS管進行防護

且所有防護器件都靠近接口放置,共模電感CM置于隔離帶內,具體布局如上圖

方案分析:

當接口與單板存在相容性較差或不相容的電路時,需要在接口與單板之間進行“分地”處理,即根據不同的端口電壓、電平信號和傳輸速率來分別設置地線。“分地”,可以防止不相容電路的回流信號的疊加,防止公共地線阻抗耦合

“分地”現象會導致回流信號跨越隔離帶時阻抗變大,從而引起極大的EMC風險,因此在隔離帶間通過電容來給信號提供回流路徑

編輯:黃飛

-

濾波器

+關注

關注

161文章

7795瀏覽量

177996 -

emc

+關注

關注

170文章

3914瀏覽量

183123 -

485接口

+關注

關注

0文章

11瀏覽量

1985

原文標題:搞定485接口EMC電路設計

文章出處:【微信號:單片機與嵌入式,微信公眾號:單片機與嵌入式】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

rs485接口EMC電路設計方案(防雷/濾波及防護電路原理圖)

【EMC家園】EMC整改難?你得先學會設計

EMC分析設計層次的講解

EMC測試從連接器、電纜開始

EMC光靠理論無法完全解決

RS485的接口EMC電路設計方案和防雷與濾波及防護電路原理圖資料合集

如何從設計層次解決EMC問題?

如何從設計層次解決EMC問題?

評論