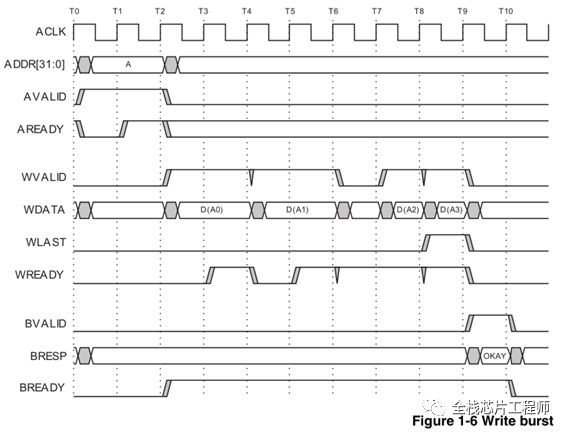

生成的IIP代碼用AMBA VIP進行仿真,發現突發寫應答不符合協議,按照協議,突發寫只需要在寫完成后,回復一個應答信號即可。

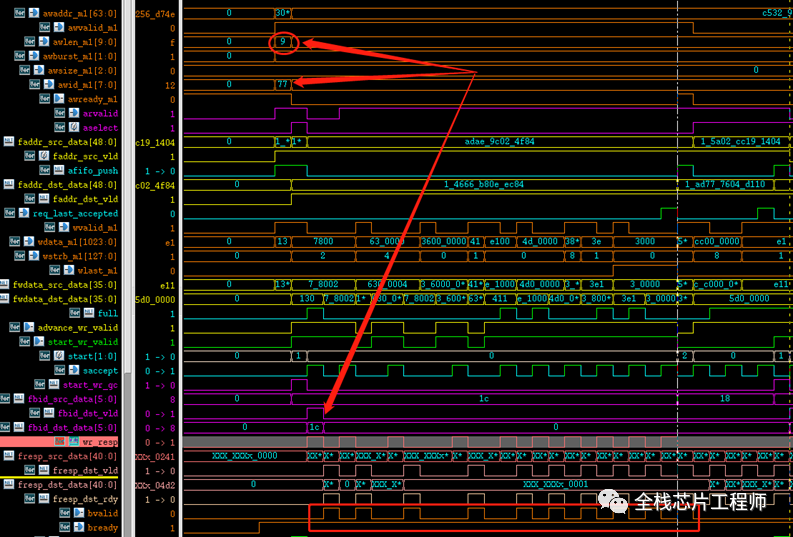

而波形是burst每個寫操作響應通道都在應答,且只有第一個應答有正確的ID。

可以看到仿真波形是burst寫期間,寫通道一直在回復bvalid,而且只有第一個回復的ID是正確的,原因是每寫一次resp_fifo就會把bid_fifo的值給清掉。

我們應該改成最后一次寫wlast時,才清掉bid_fifo并同時給一次resp信號即可。

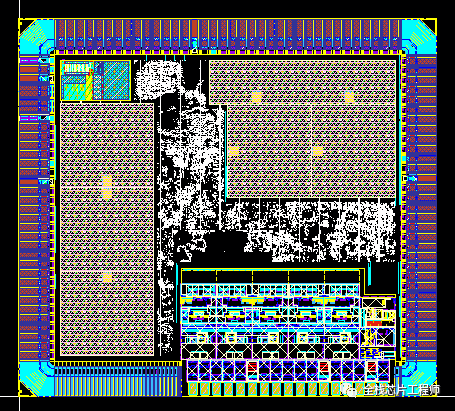

實戰ISP圖像算法效果

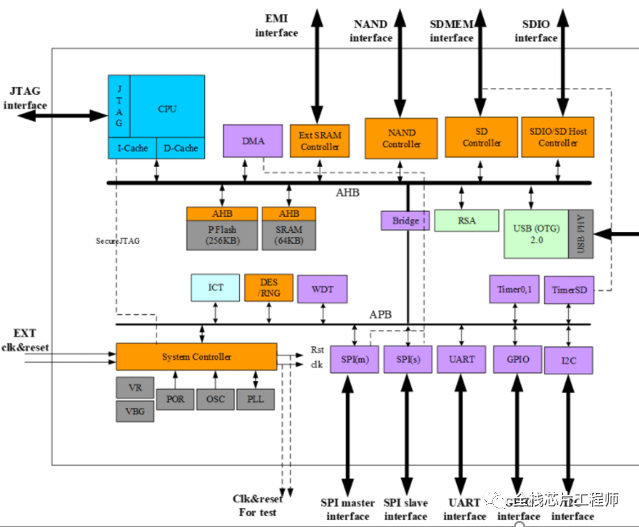

以項目驅動的方式介紹MCU芯片全流程設計的方法;

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FIFO芯片

+關注

關注

0文章

10瀏覽量

8803 -

AMBA

+關注

關注

0文章

68瀏覽量

14981 -

axi協議

+關注

關注

0文章

8瀏覽量

2129

原文標題:AXI IIP突發寫的bug定位

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

玩轉Zynq連載3——AXI總線協議介紹1

● 基于特定地址進行的突發傳輸●通過獨立的讀和寫通道實現低成本直接內存訪問(DMA)●支持無序數據傳輸●提供多級寄存器鎖存的支持,實現更好的時序收斂 1.1 AXI版本介紹AXI協議是

發表于 05-06 16:55

Vivado中AXI互連的突發模式

我一直在使用精簡版的AXI接口,但我需要使用突發模式來加快傳輸速度。我不太了解如何更改界面,有人可以告訴我如何在Vivado中更改我的IP以使用突發模式嗎?非常感激

發表于 04-15 07:21

高級可擴展接口(AXI)簡介

主機和從機用于交換信息。優先級仲裁器確定當前哪個主機使用該總線,而中央解碼器執行從機選擇。突發執行操作可能需要花費多個總線周期才能完成。每個突發傳輸都包括一個地址和控制階段,隨后是一個數據階段。 AXI

發表于 09-28 10:14

ARM系列 -- AXI協議資料匯總(一)

。 2、AXI通道之間的關系前面說到AXI的五個通道是獨立的,但通道間必須保持一定的約定關系:寫回復必須在一次寫事務的最后一個寫數據之后讀數據必須在接收到讀地址信號之后通道間握手必須滿

發表于 04-08 09:34

AXI接口協議詳解

4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允許最大256輪的數據突發傳輸;AXI

發表于 04-08 10:45

看看Axi4寫通道decoder的設計

讀寫分離的設計在Axi4總線中,讀和寫通道是完全相互獨立,互不干擾。故而無論是在設計Decoder還是Arbiter時,均可以采用讀寫分離的方式。如前文所述,SpinalHDL在基于Axi4總線

發表于 08-03 14:27

AXI 總線和引腳的介紹

1、AXI 總線通道,總線和引腳的介紹 AXI接口具有五個獨立的通道: (1)寫地址通道(AW):write address channel (2)寫數據通道( W): write d

發表于 01-05 08:13

?1w次閱讀

AXI-4 Lite接口協議仿真波形解析

AXI-4 Lite可以看作是AXI-4 Memory Mapped的子集,從下面的示例圖中就可見一斑。最直接的體現是AXI-4 Lite的突發長度是固定值1。

高級可擴展接口(AXI)簡介

主機和從機用于交換信息。優先級仲裁器確定當前哪個主機使用該總線,而中央解碼器執行從機選擇。突發執行操作可能需要花費多個總線周期才能完成。每個突發傳輸都包括一個地址和控制階段,隨后是一個數據階段。AXI

關于AXI BRAM控制器的相關內容

所有與axis主設備的通信都是通過一個5通道的axis接口進行的。所有寫操作都在AXI總線的寫地址通道(AW)上啟動,該通道指定了寫事務的類型和相應的地址信息。

AXI3與AXI4寫響應的依賴區別?

上面兩圖的區別是相比AXI3,AXI4協議需要確認AWVALID、AWREADY握手完成才能回復BVALID。為什么呢?

AXI IIP突發寫的bug定位如何解決?

AXI IIP突發寫的bug定位如何解決?

評論