介紹 :

引導過程是任何 SoC 在復位解除后進行各種設備配置(調整位、設備安全設置、引導向量位置)和內存初始化(如 FLASH/SRAM/GRAM)的過程。在引導過程中,各種模塊/外設(如時鐘控制器或安全處理模塊和其他主/從)根據 SoC 架構和客戶應用進行初始化。在多核 SoC 中,首先主要核心(也稱為引導核心)在引導過程中啟動,然后輔助核心由軟件啟用。

引導過程從上電復位 (POR)開始,硬件復位邏輯強制 ARM 內核(Cortex M 系列)從片上引導 ROM 開始執行。引導 ROM 代碼使用給定的引導選擇選項以及各種 FUSE/straps 和 GPIO 設置的狀態來確定 SOC 的引導流程行為。

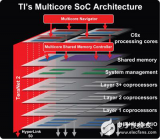

什么是多核 SoC:

多核 SoC 有多個處理器,每個處理器都有自己的特定應用。

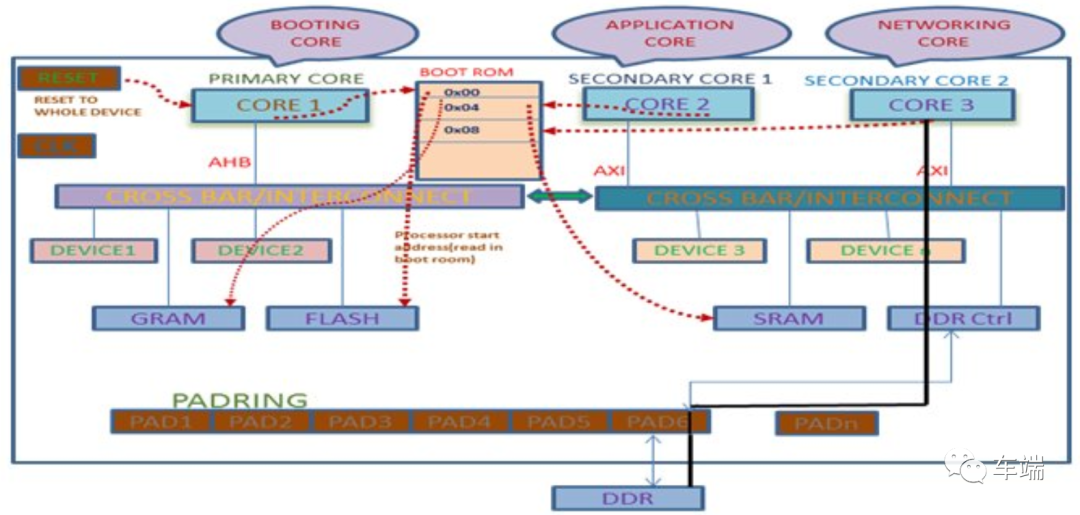

在網絡/汽車應用等復雜 SoC 中,大多數行業 SoC 將主內核(啟動內核)、應用程序/系統內核、網絡內核集成在單個芯片上,以處理來自不同外設(主/從)的各種數據。主內核是任何處理啟動和最大功能的 SoC 的核心,但對于大流量數據(以太網/TDM)和高頻(CSI-2,QSPI)應用程序,我們需要有特定的應用程序內核,如 CORTEX-A 內核來處理數據.

圖 1:多核 SoC 的架構

多核 SoC 的引導流程:

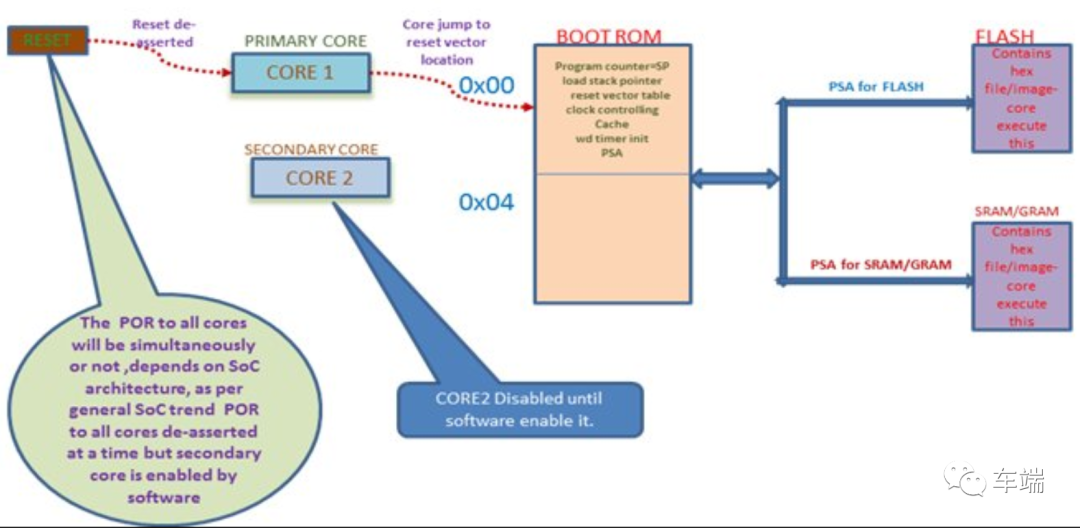

當設備獲得 POR 時,主內核跳轉到復位向量位置。復位向量是映射到 ROM 起始地址(也稱為引導 ROM)的位置,內核將在 POR 后從此處開始執行。ARM 處理器(如 Cortex-M 系列)使用位于 0x00000000 的復位向量。該決定是通過配置輸入信號做出的,因此在不同的 SoC 之間可能會有所不同。

一旦主核心(如 ARM Coretx-M)脫離復位,它將從內存地址位置 0x00000000 開始執行。主內核加載程序計數器并從地址 0xSP 開始執行(主內核堆棧指針,在 0xSP 位置的 ROM 內部,它將加載堆棧指針),這指示內核加載其重置處理程序(堆棧指針,向量表)和讀取處理器Start Address(PSA)獲取應用程序引導地址并跳轉到該位置。

在PSA中,hex 文件或映像由引導加載程序加載。該地址可以是 SRAM/GRAM 或 FLASH。

CORE 將執行來自 PSA 的 Image/.hex,它可能會按照引導加載程序的指示加載到 SRAM/GRAM 或 FLASH。

將 Image/.hex 加載到內存(FLASH/SRAM/GRAM)中是由引導加載程序完成的。該加載程序可以內置在 BOOT ROM 中,也可以是外部加載程序。

在 SoC 驗證中,hex 文件/圖像是由 .c 文件(模式)通過編譯器 -> 匯編程序 -> 鏈接器 ->.ELF->.HEX 生成的。

圖 2:多核 SoC 中主核的啟動順序

主內核已經啟動并準備好移除其余部分以重置其他外設以及輔助內核,因為默認情況下輔助內核被禁用,由軟件啟用。

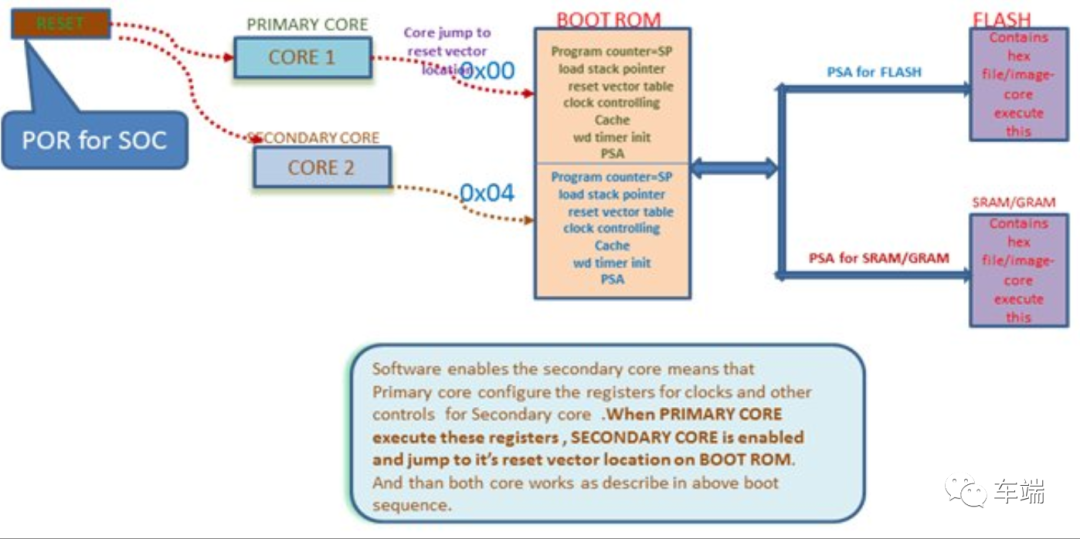

一旦軟件決定啟用輔助內核,相應的寄存器(取決于 SoC 架構,啟用輔助內核和時鐘控制寄存器)需要使用主內核進行編程。一旦啟用輔助內核,這將開始從復位中獲取數據向量位置(這與主核的復位向量位置不同,主核的復位向量位置是 0x00000000,而次級核的復位向量位置可以是 0x00000004)。

實際上,輔助核心也從 0x00000000 啟動,并且通過使用虛擬化概念(從 0x00000000 到 0x00000004 的內存映射)或總線探測概念,它必須將 0x00000000 地址映射到 0x00000004 并從該地址獲取第一條指令。

現在輔助內核加載程序計數器并從地址 0xSP(輔助內核堆棧指針)開始執行,它指示內核加載其重置處理程序(堆棧指針、向量表)并讀取 PSA 以獲取應用程序引導地址并跳轉到該位置。

圖 3:多核 SoC 中輔助內核的啟動順序

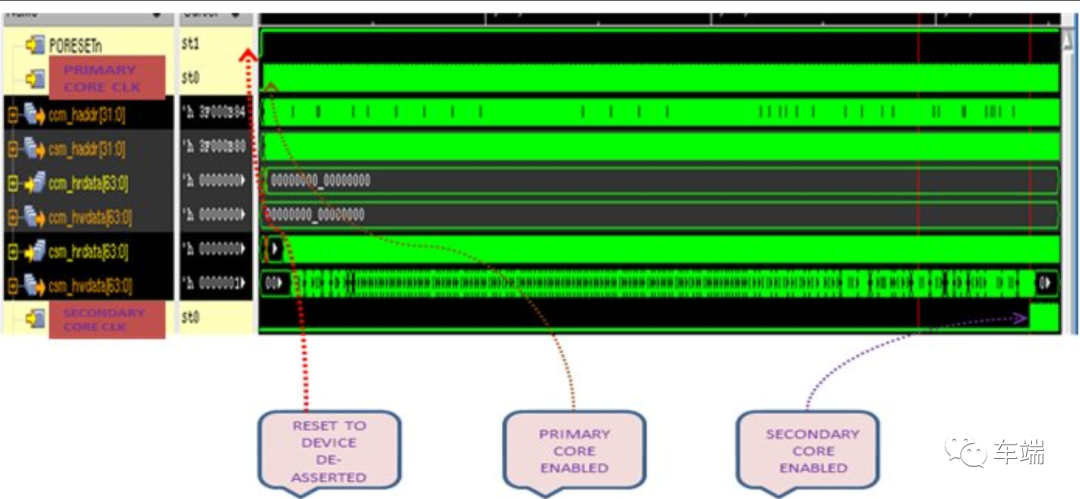

圖 4:啟用多核

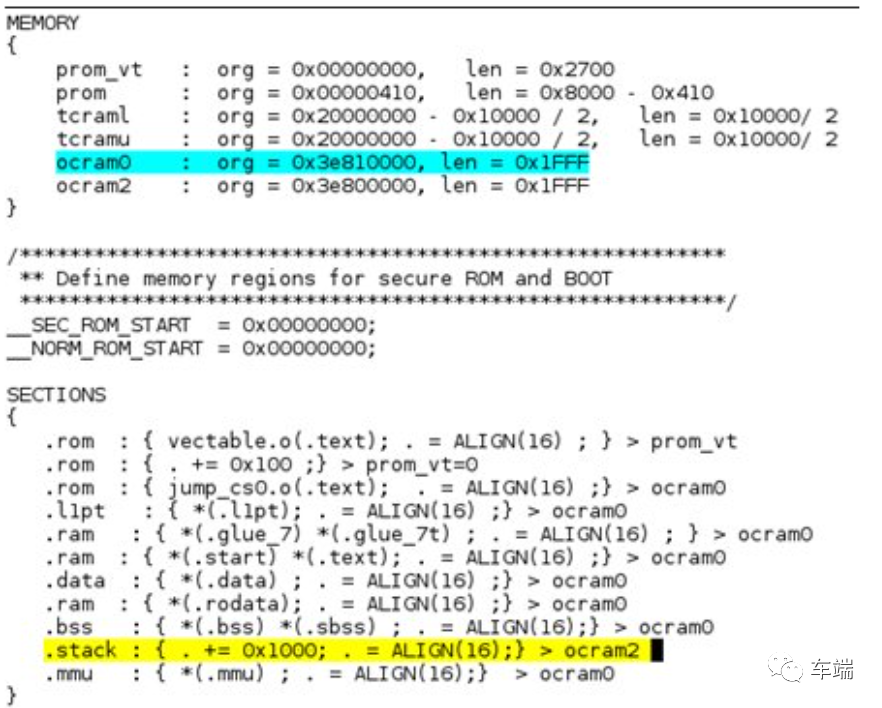

初級核心和次級核心有單獨的 Image/.hex。Image/.hex 應該為所有核心存儲不同的內存位置(即 GRAM/SRAM/FLASH)。這表明 PSA 對于所有內核都是不同的。此設置是 SoC 架構的一部分,由所有內核的鏈接器文件決定。例如,告訴 Image/.hex 文件地址和起始地址的鏈接器文件將是 PSA 。

例如:根據鏈接器文件生成的圖像/十六進制開始和結束地址。

CORE1-0X3E800000-0X3E80FFFF

CORE2-0X3E810000-0X3E81FFFF

CORE3- …..

什么是引導加載程序:

根據 SoC 架構和實現,引導加載程序可以是引導 ROM 的一部分或在引導 ROM 之外。引導加載程序是根據 Fuse/straps 配置將圖像/十六進制加載到內存中的程序。Boot loader 是一個程序,它具有所有外設和引導接口的數據結構。引導加載程序是高度特定于內核和電路板的。引導加載程序將在 POR 到 SoC 時執行。

Bootrom的職責:

執行必要的初始化,包括對 PLL、時鐘、堆棧、中斷設置、看門狗定時器等進行編程。

啟用不同的一級緩存。

根據 Fuses/Straps 引腳值配置 I/O 元件和引腳多路復用。

將閃存控制器初始化為默認設置。

從閃存(NOR、NAND)、外部存儲器、SD/MMC、USB 或 UART 加載用戶代碼。引導順序和選項由保險絲/帶針設置。

ROM 的特點包括:

支持從各種啟動設備啟動

串行下載器支持(USB、Flex CAN 和 UART 等)

主引導數據(初始接口的配置數據)

從低功耗模式喚醒

喚醒二級核心

Boot ROM 可以支持以下引導設備:

閃光

標清/多媒體卡

QuadSPI

串行 ROM 設備(通過 I2C 和 SPI 接口)

PCI/USB/UART等

重置向量表或重置處理程序:

處理器復位后,它將在異常向量表中的復位向量位置(地址 0x00000000)開始執行。

重置處理程序代碼滿足以下目的。

在多核架構中,將所有次核置于睡眠/禁用狀態

異常向量的初始化

內存/緩存/TLB 初始化

堆棧和處理器模式寄存器初始化

對 IO 設備執行必要的初始化并啟用中斷

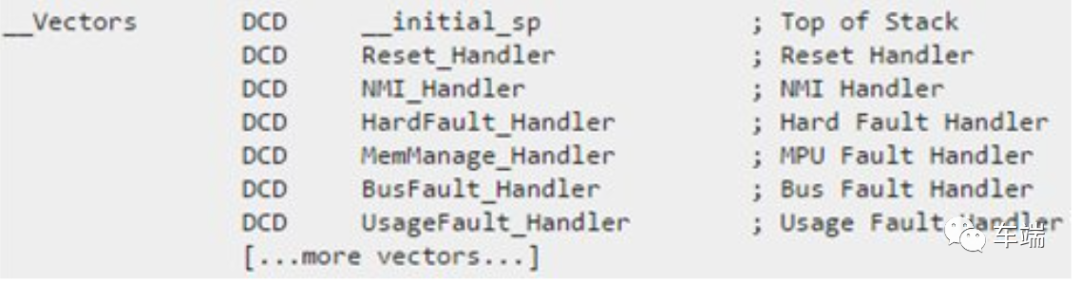

ARM M 系列內核的典型向量表:

引導順序中的挑戰和問題:

以下是與引導順序相關的主要挑戰和問題。

1. 核心之間的同步:在 SoC 設計中是否有啟動時存在多少個核心的信息?哪個核心是初級核心?

如果所有內核同時退出復位狀態,它們通常都從同一個復位向量開始執行。然后引導代碼讀取集群 ID 以確定哪個核心是主要核心。主要核心執行初始化,然后向次要核心發出一切準備就緒的信號。另一種方法是在主核進行初始化時將輔助核保持在復位狀態。該方法需要硬件支持來協調復位。CP15: MPIDR Multiprocessor Affinity Register 提供了多核系統中的識別機制。

2. 堆棧設置問題:通常,在單核系統中,啟動堆棧被初始化以跳轉到BootROM。稍后,系統堆棧被初始化,整個系統都使用該堆棧。當支持多核系統時,一種方法可能是讓每個內核重復臨時和系統堆棧操作。然而,更好的方法是將一個主內核設置為所有內核的系統堆棧。這將減少輔助核心上的初始化代碼。

3. 在地址零或復位向量處啟動一個帶有未初始化內存的處理器:

在復位時,處理器總是從地址為零的復位向量位置啟動。

對于地址為零的未初始化內存(例如,未編程的閃存或未初始化的 GRAM/SRAM),處理器將從地址 0x0 讀取虛假的初始主堆棧指針值,并從該地址讀取虛假的代碼入口點,可能包含非法指令集狀態位 [0] 中的說明符(ESPR.T 位)。

處理器可能會立即鎖定,或者可能會執行一些虛假的操作碼,但在后一種情況下,鎖定仍然是可能的結果。

4. 多個內核在同一復位向量共享同一引導 ROM:

多個核心在地址 0x0 處共享相同的引導 ROM 并不常見,因為這意味著多個核心將使用相同的初始主堆棧指針 (MSP) 地址啟動,這將導致堆棧損壞(包括 NMI 或任何故障異常)。

在 SoC 的啟動序列中處理挑戰的戰略方法:

為克服上述問題,必須相應地更新多核 SoC 中所有內核的鏈接器文件。每個內核都有單獨的鏈接器。典型的鏈接器文件包含有關 Image/hex 中地址的信息,即要生成的 Hex/image 文件的起始地址和范圍,還有堆棧相關信息。鏈接器文件設置取決于 SoC 架構。

ARM 鏈接器文件如下所示:

必須控制初級核心和次級核心的初始化順序,以免堆棧損壞。因此,首先必須初始化主要核心(保持其他核心處于重置/暫停狀態),而不是其他核心。

結論:

VLSI 芯片設計行業正朝著集成多個內核的單芯片中越來越復雜的設計邁進。多核啟動順序有助于理解,SoC 的實際工作方式以及 POR 斷言后 SoC 喚醒的順序是什么。在此paper,我們已經討論了基于ARM的SoC中的多核啟動順序以及相關描述

引導 ROM、引導加載程序、使用鏈接器文件生成圖像/十六進制、引導選項(從 SPI/SDIO/PCI 等不同設備引導)。還談到了從各種存儲器(SRAM/GRAM/FLASH)形成的多核引導。除此之外,還討論了在初始級別的多核引導期間面臨的挑戰和面臨的問題以及處理這些問題/挑戰的方法。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19259瀏覽量

229657 -

ARM

+關注

關注

134文章

9087瀏覽量

367398 -

控制器

+關注

關注

112文章

16334瀏覽量

177815 -

FlaSh

+關注

關注

10文章

1633瀏覽量

147948 -

soc

+關注

關注

38文章

4163瀏覽量

218169

原文標題:基于ARM的多核SoC的啟動方法

文章出處:【微信號:談思實驗室,微信公眾號:談思實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

以全新的多核SoC架構進行LTE開發

消費電子助力SoC發展,多核技術是焦點

創龍帶您解密TI、Xilinx異構多核SoC處理器核間通訊

TI推出多核SoC顯著簡化通信基礎局端設備的設計

TI推出最新多核SoC架構,實現5倍性能提升

基于TI最新多核DSP SoC架構的解析

KeyStone多核SoC工具套件

66AK2L06多核DSP+ARM KeyStone II片上系統(SoC)數據表

66AK2Hxx多核DSP+ARM? KeyStone II片上系統(SoC)數據表

66AK2E0x多核DSP+ARM KeyStone II片上系統(SoC)數據表

什么是多核SoC?基于ARM的多核SoC的啟動方法介紹

什么是多核SoC?基于ARM的多核SoC的啟動方法介紹

評論