在嵌入式系統中,板上通信接口是指用于將各種集成電路與其他外圍設備交互連接的通信通路或總線,以下內容為常用板上通信接口。

I2C總線

I2C總線是一種同步、雙向、半雙工的兩線式串行接口總線,這里,半雙工的含義是指在任意給定的時刻,只有一個方向上是可以通信的。I2C總線由兩條總線組成:串行時鐘線SCL和串行數據線SDA。

SCL線:

負責產生同步時鐘脈沖。

SDA線:

負責在設備間傳輸串行數據。I2C總線是共享的總線系統,因此可以將多個I2C設備連接到該系統上,連接到I2C總線上的設備既可以用作主設備,也可以用作從設備。

主設備負責控制通信,通過對數據傳輸進行初始化/終止化,來發送數據并產生所需的同步時鐘脈沖。從設備則是等待來自主設備的命令,并響應命令接收,主設備和從設備都可以作為發送設備或接收設備。

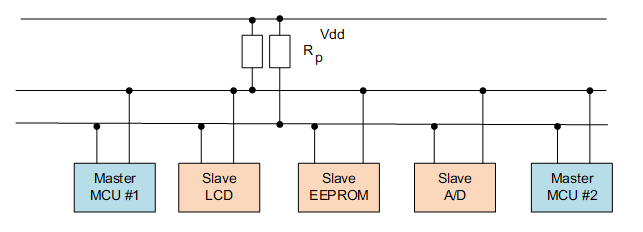

無論主設備是作為發送設備還是接收設備,同步時鐘信號都只能由主設備產生。在相同的總線上,I2C支持多個主設備的同時存在,下圖顯示了I2C總線上主設備和從設備的連接關系。

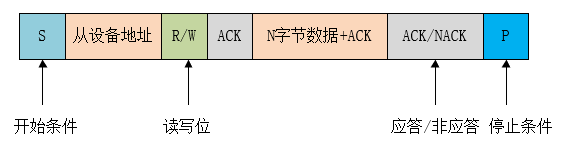

當總線空閑時,SDA 和SCL 都處于高電平狀態,當主機要和某個從機通訊時,會先發送一個開始條件,然后發送從機地址和讀寫控制位,接下來傳輸數據(主機發送或者接收數據),數據傳輸結束時主機會發送停止條件,傳輸的每個字節為8 位,高位在前,低位在后。

開始條件:

SCL 為高電平時,主機將SDA 拉低,表示數據傳輸即將開始。

從機地址:

主機發送的第一個字節為從機地址,高7 位為地址,最低位為R/W 讀寫控制位,1 表示讀操作,0 表示寫操作。一般從機地址有7 位地址模式和10 位地址模式兩種,如果是10 位地址模式,第一個字節的頭7 位是11110XX 的組合,其中最后兩位(XX)是10 位地址的兩個最高位,第二個字節為10 位從機地址的剩下8 位,如下圖所示:

應答信號:

每傳輸完成一個字節的數據,接收方就需要回復一個ACK,寫數據時由從機發送ACK,讀數據時由主機發送ACK,當主機讀到最后一個字節數據時,可發送NACK然后跟停止條件。

數據:

從機地址發送完后可能會發送一些指令,依從機而定,然后開始傳輸數據,由主機或者從機發送,每個數據為8 位,數據的字節數沒有限制。

重復開始條件:

在一次通信過程中,主機可能需要和不同的從機傳輸數據或者需要切換讀寫操作時,主機可以再發送一個開始條件。

停止條件:

在SDA 為低電平時,主機將SCL 拉高并保持高電平,然后在將SDA 拉高,表示傳輸結束。

SPI總線

SPI總線是同步、雙向、全雙工的4線式串行接口總線,SPI是由“單個主設備+多個從設備”構成的系統。需要說明的是:在系統中,只要任意時刻只有一個主設備是處于激活狀態的,就可以存在多個SPI主設備。常運用于EEPROM、FLASH、實時時鐘、AD轉換器、數字信號處理器和數字信號解碼器之間實現通信。為了實現通信,SPI共有4條信號線,分別是:

主設備出、從設備入

(Master Out Slave In,MOSI):由主設備向從設備傳輸數據的信號線,也稱為從設備輸入(Slave Input/Slave Data In,SI/SDI)。

主設備入、從設備出

(Master In Slave Out,MISO):由從設備向主設備傳輸數據的信號線,也稱為從設備輸出(Slave Output/Slave Data Out,SO/SDO)。

串行時鐘

(Serial Clock,SCLK):傳輸時鐘信號的信號線。

從設備選擇

(Slave Select,SS):用于選擇從設備的信號線,低電平有效。

SPI使用方法:

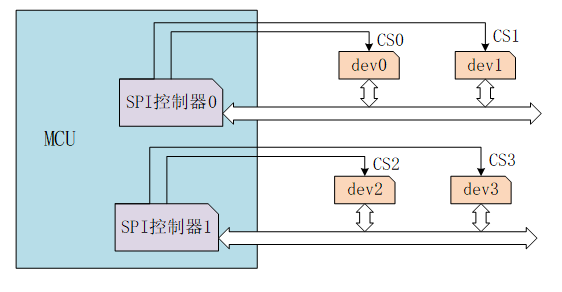

上圖所示芯片有2 個SPI 控制器,SPI 控制器對應SPI 主設備,每個SPI 控制器可以連接多個SPI從設備。掛載在同一個SPI 控制器上的從設備共享3 個信號引腳:SCK、MISO、MOSI,但每個從設備的CS 引腳是獨立的.

主設備通過控制CS 引腳對從設備進行片選,一般為低電平有效,任何時刻,一個SPI 主設備上只有一個CS 引腳處于有效狀態,與該有效CS 引腳連接的從設備此時可以與主設備通信。所以,SPI通信方式可以使用“一主多從”的結構進行通信,每個連接到總線上的器件都有唯一的地址,主設備啟動數據傳輸并產生時鐘信號,從設備被主設備尋址,同一時刻只允許有一個主設備。

從設備的時鐘由主設備通過SCLK 提供,MOSI、MISO 則基于此脈沖完成數據傳輸。SPI 的工作時序模式由CPOL和CPHA之間的相位關系決定,CPOL 表示時鐘信號的初始電平的狀態,CPOL 為0 表示時鐘信號初始狀態為低電平,為1 表示時鐘信號的初始電平是高電平。

CPHA 表示在哪個時鐘沿采樣數據,CPHA 為0 表示在首個時鐘變化沿采樣數據,而CPHA 為1 則表示在第二個時鐘變化沿采樣數據。根據CPOL 和CPHA 的不同組合共有4 種工作時序模式:CPOL=0,CPHA=0、CPOL=0,CPHA=1、CPOL=1,CPHA=0、CPOL=1,CPHA=1。

UART通用異步收發傳輸器,UART 作為異步串口通信協議的一種,工作原理是將傳輸數據的每個字符一位接一位地傳輸,在應用程序開發過程中使用頻率較高的數據總線。

基于UART的數據傳輸是異步形式的串行數據傳輸,基于UART的串行數據傳輸不需要使用時鐘信號來同步傳輸的發送端和接收端,而是依賴于發送設備和接收設備之間預定義的配置。

對于發送設備和接收設備來說,兩者的串行通信配置(波特率、單位字的位數、奇偶校驗、起始位數與結束位、流量控制)應該設置為完全相同。通過在數據流中插入特定的比特序列,可以指示通信的開始與結束,當發送一個字節數據的時候,需要在比特流的開頭加上起始位,并在比特流的末尾加上結束位,數據字節的最低位緊接在起始位之后。

UART 串口的特點是將數據一位一位地順序傳送,只要2 根傳輸線就可以實現雙向通信,一根線發送數據的同時用另一根線接收數據。UART 串口通信有幾個重要的參數,分別是波特率、起始位、數據位、停止位和奇偶檢驗位,對于兩個使用UART 串口通信的端口,這些參數必須匹配,否則通

起始位:

表示數據傳輸的開始,電平邏輯為“0” 。

數據位:

可能值有5、6、7、8、9,表示傳輸這幾個bit 位數據。一般取值為8,因為一個ASCII 字符值為8 位。

奇偶校驗位:

用于接收方對接收到的數據進行校驗,校驗“1” 的位數為偶數(偶校驗) 或奇數(奇校驗),以此來校驗數據傳送的正確性,使用時不需要此位也可以。

停止位:

表示一幀數據的結束。電平邏輯為“1”。

波特率:

串口通信時的速率,它用單位時間內傳輸的二進制代碼的有效位(bit) 數來表示,其單位為每秒比特數bit/s(bps),常見的波特率值有4800、9600、14400、38400、115200 等,數值越大數據傳輸的越快,波特率為115200 表示每秒鐘傳輸115200 位數據。

1-Wire接口

1-Wire接口是由Maxim Dallas半導體公司開發的異步半雙工通信協議,也稱為Dallas 1-Wire?協議,其中,按照主-從通信模型,只使用單條信號線DQ實現通信。1-Wire總線的一個重要特征在于,該總線允許在信號線上傳輸能量,1-Wire接口支持在總線上連接單個主設備以及一個或多個從設備。

并行接口

板上并行接口通常用于系統與外圍設備之間的通信,其中,外圍設備通過存儲器映射到系統的主控端。

只要嵌入式系統的主控處理器/控制器含有并行總線,支持并行總線的設備就可以直接連接到該總線系統上。外圍設備與主控端之間具有控制信號接口,可以控制并行總線上的數據通信,這里,通信的控制信號包括讀/寫信號和設備選擇信號。

一般說來,外圍設備具有設備選擇線,只有當主控處理器選通該線的時候,該設備才是有效的。數據傳輸的方向可以是從主控端到外圍設備,也可以是從外圍設備到主控端,這是通過讀和寫控制信號線進行控制的,只有主控處理器能夠控制讀控制信號和寫控制信號。

一般說來,外圍設備通過存儲器映射到主控處理器,從而可以訪問分配的地址范圍,此時,設備需要使用地址譯碼電路來產生芯片選擇信號。當處理器選擇的地址位于設備指定范圍內的時候,譯碼電路對芯片選擇線進行觸發,從而激活設備。

然后,處理器可以使能相應的控制線(分別是RD與WD),從而由設備讀出數據,或者是向設備寫入數據。為了實現并行通信,系統需要嚴格遵循時序規范。前面已經提到過,并行通信是由主控處理器啟動的。如果某外圍設備想要對通信進行初始化,那么可以向處理器發出中斷,告知相關信息。

為了實現上述功能,設備的中斷線需要連接到處理器的中斷線上,并且主控處理器需要觸發相應的中斷。需要說明的是,主控處理器的數據總線寬度決定了并行接口的寬度,可以是4位、8位、16位、32位、64位等,設備支持的總線寬度應該與主控處理器完全相同。

-

集成電路

+關注

關注

5387文章

11530瀏覽量

361636 -

嵌入式系統

+關注

關注

41文章

3587瀏覽量

129436 -

通信接口

+關注

關注

3文章

237瀏覽量

30980

發布評論請先 登錄

相關推薦

幾種常用單片機之間的通信方式

幾種常用單片機之間的通信方式

通信接口有哪些_幾種常見的通信接口

嵌入式開發中常用的幾種通信接口總結

常用的幾種通信接口解析

常用的幾種通信接口解析

評論