除了SPI這種串行接口比較受存儲器設計廠商的歡迎,還有比如由samsung和toshiba設計的Toggle NAND Interface,也被稱為 Asynchronous DDR NAND Interface ( DDR:double data rate ,之所以設計成Asynchronous是因為最開始傳統(tǒng)的存儲器用的就是異步設計方法),雖然數(shù)據(jù)的傳輸速率得到了大大提升(使用DDR設計方法),但是確保數(shù)據(jù)準確性的設計卻較為復雜。

另外一種比較受歡迎的接口就是由Cypress設計的 ONFI(Open NAND Flash Interface) NAND Interface, 據(jù)說現(xiàn)在的4.1版本已經(jīng)能夠達到1200MBps的傳輸速率了。而且使用的是NV-DDR3的1.2V電壓標準,使得功耗也得到了改進。以上兩種接口不是本篇文章討論的重點,就暫且介紹到這里,感興趣的朋友們可以在網(wǎng)上自行搜索更詳細的資料了解學習,我們還是回到SPI接口上來。

下面我們就來講講為什么芯片常選用SPI作為與存儲器互聯(lián)的接口,也就是說SPI相較于其他接口有什么優(yōu)勢。

最主要的一個原因也是目前業(yè)界使用的大部分存儲器( Serial NAND FLASH )使用的都是SPI接口,比如WINBOND家的,MICRON家的和GIGADEVICE家的,好像有種被綁架的感覺。。。

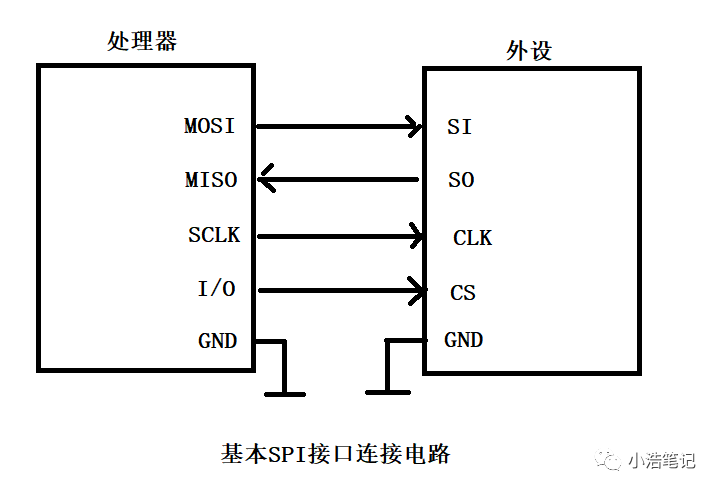

一般在SPI接口的數(shù)據(jù)端還會設計一個FIFO(數(shù)據(jù)寬度一般為8bit)來控制數(shù)據(jù)能夠穩(wěn)定被接收到,因此,SPI由一個緩沖區(qū)組成,該緩沖區(qū)通過 DMA (直接存儲器訪問)或CPU可尋址緩沖區(qū)與系統(tǒng)接口。時鐘邏輯從內(nèi)部系統(tǒng)時鐘獲得時鐘,并可針對所需的速度進行編程。引腳控制邏輯提供輸出驅動和延遲設置。可以有各種控制和狀態(tài)寄存器為器件提供可編程性。

除此之外在物理實現(xiàn)的過程中會在接口產(chǎn)生一個延遲(正常情況不會超過兩個時鐘周期)。所以如果在full-duplex mode下,當slave已經(jīng)將所需的數(shù)據(jù)都發(fā)送出去(發(fā)送的數(shù)據(jù)多少需要提前由master發(fā)出的指令決定),但是master還是會多產(chǎn)生幾個時鐘周期的SCLK和CS信號,這個時候就會采集到幾個沒有意義的數(shù)據(jù)線上的信號(signal low)。這個時候就需要系統(tǒng)軟件識別出多余的信號然后將它們從有效數(shù)據(jù)中剔除出去。

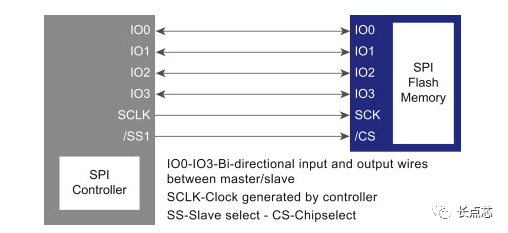

目前除了最開始介紹的傳統(tǒng)四線數(shù)據(jù)線的SPI接口,為了進一步增大接口的數(shù)據(jù)傳輸速率,已經(jīng)發(fā)展成了具有多個數(shù)據(jù)傳輸pin口的接口,比如說dual,quad SPI。

多個數(shù)據(jù)傳輸pin口

結語

SPI作為一個芯片常見的片外接口,適用于許多目前業(yè)界流行的Serial存儲器設備,這些Serial NAND Flash一般作為儲存芯片boot code的存儲設備。有許多的優(yōu)勢所在,而相比于并行接口,改進后的串行接口目前也有較高的數(shù)據(jù)吞吐率以及成本較低的優(yōu)勢,無論是在工藝上還是功耗上。

-

存儲器

+關注

關注

38文章

7557瀏覽量

164940 -

SPI

+關注

關注

17文章

1731瀏覽量

92894 -

串行接口

+關注

關注

3文章

332瀏覽量

42835

發(fā)布評論請先 登錄

相關推薦

SPI接口的基本原理

用SPI接口擴展外部Flash存儲器

Cyclone IV 器件中的外部存儲器接口

詳解多功能雙接口存儲器方案

基于DSP的存儲器接口寬度調節(jié)設計

AXI內(nèi)部存儲器接口的功能

利用C8051F020的SPI接口擴展大容量數(shù)據(jù)存儲器

信號完整性的價值:存儲器接口設計

SPI接口在存儲器接口上的應用

SPI接口在存儲器接口上的應用

評論