1

1.名詞解釋

UART:

全稱 Universal Asynchronous Receiver/Transmitter,中文可譯為通用異步收發(fā)器。

2.歷史由來

UART的發(fā)明是由于貝爾自己需要將一個電傳打印機(Teletype)連接到一個PDP-1,需要將并行信號轉(zhuǎn)換為串行信號。貝爾于是設(shè)計了一個使用大約50個獨立部件的電路。這個想法被證明是受歡迎的。當(dāng)時西部數(shù)據(jù)公司(Western Digital)是一家制造計算機芯片的小公司,它設(shè)計了單芯片版的UART。

3.應(yīng)用場景

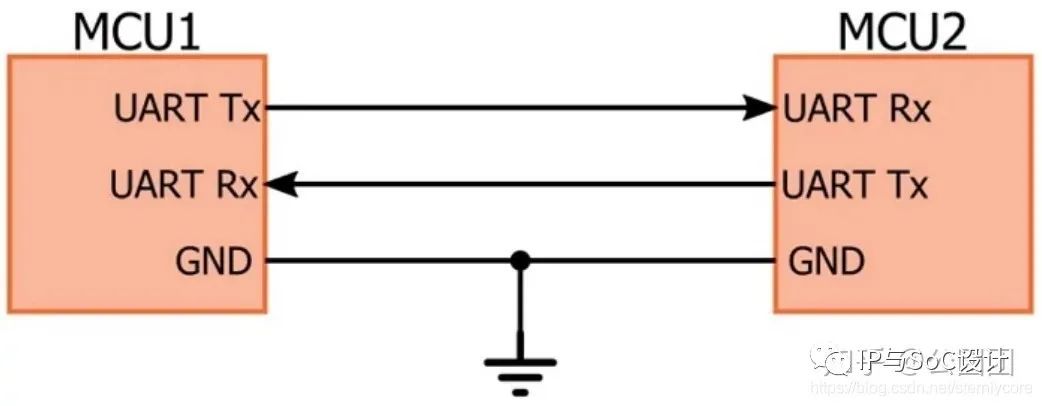

UART當(dāng)前常用于MCU的低速互聯(lián),最少僅需要兩根信號連接(TXD和RXD),信號支持TTL電平,RS232電平或者RS422電平。UART為全雙工異步通信協(xié)議,最高支持115200bps的波特率(常用波特率為9600bps)。

4.協(xié)議解析

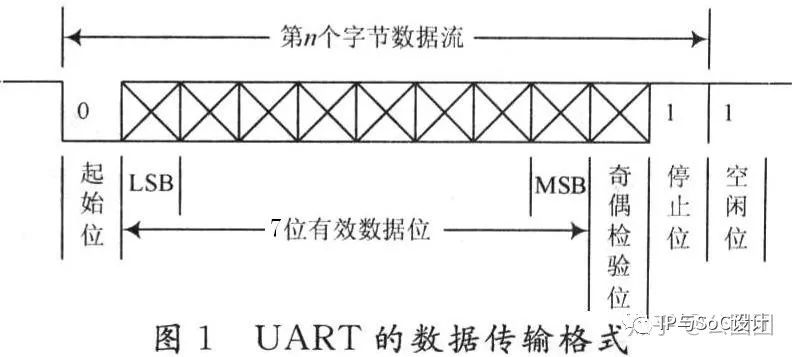

UART定義了一種串行傳輸協(xié)議,單次可傳輸一個字符,包含5到8bit有效數(shù)據(jù)(常采用7bit數(shù)據(jù),ASCII)。

UART的一個字符除了包含有效數(shù)據(jù)位外,還包含起始位1bit,奇偶校驗位1bit和停止位1bit(也支持1.5bit或者2bit配置)。UART一次傳輸最多8bit有效數(shù)據(jù)而不是更多的原因是其設(shè)計標(biāo)準(zhǔn)收發(fā)兩端的頻率誤差在10%以內(nèi),當(dāng)收到的數(shù)據(jù)為8bit時誤差控制在1bit內(nèi),保證了數(shù)據(jù)的采樣不會出錯。

5. 協(xié)議實現(xiàn)

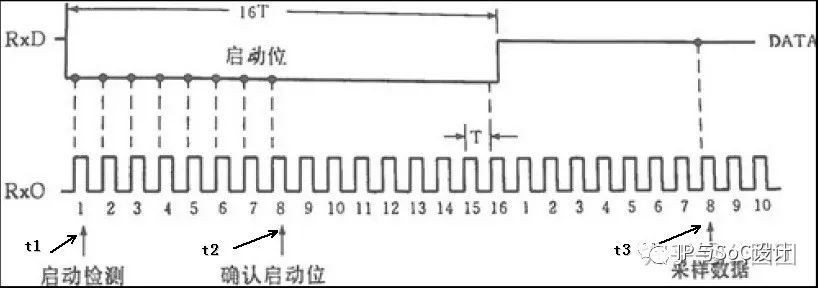

UART接收使用高頻時鐘進(jìn)行采樣,在最早的8086芯片中為兼顧速度和穩(wěn)定性,常采用波特率的16倍時鐘進(jìn)行采樣。當(dāng)主時鐘頻率確定時,IC實現(xiàn)中可以通過設(shè)定波特率寄存器N實現(xiàn)任意波特率。

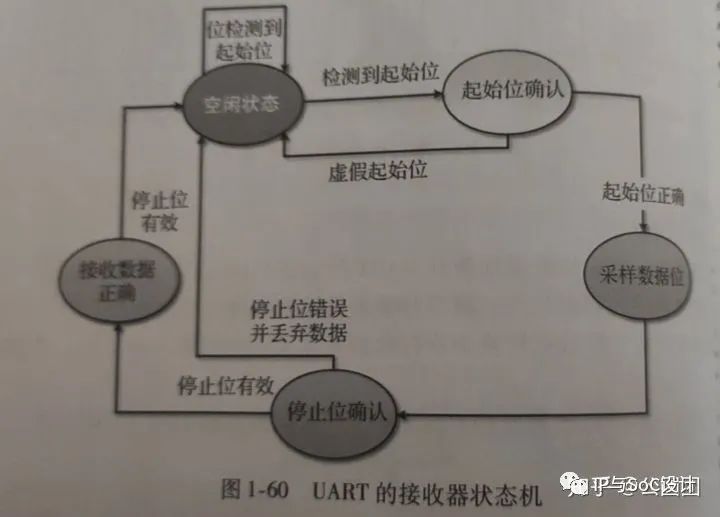

一個典型的UART接收器的狀態(tài)機設(shè)計如圖所示,在空閑狀態(tài)時接收機通過監(jiān)測接收信號從1變0,確定接收的起始位。為消除通信線路噪聲的影響,只有連續(xù)接收到N/2個0后才認(rèn)為這是一個真正的起始位,并開始在最佳采樣點(N/2時刻)采樣數(shù)據(jù)位。

6. 流程控制

UART的流控包括硬件流控和軟件流控兩種。

硬件流控基于RS232的兩個信號接口RTS(數(shù)據(jù)發(fā)送請求)和CTS(數(shù)據(jù)發(fā)送允許),一端設(shè)備的RTS與另一端設(shè)備的CTS相連。RTS與CTS均為低電平有效,數(shù)據(jù)接收設(shè)備通過置低RTS接口通知發(fā)送設(shè)備的CTS接口,發(fā)送設(shè)備可以發(fā)送數(shù)據(jù)。

軟件流控通過帶內(nèi)傳輸XOFF和XON信號,控制發(fā)送的起停。數(shù)據(jù)接收設(shè)備通過發(fā)送XOFF通知數(shù)據(jù)發(fā)送設(shè)備停止發(fā)送數(shù)據(jù)。數(shù)據(jù)接收設(shè)備通過發(fā)送XON通知發(fā)送設(shè)備繼續(xù)發(fā)送數(shù)據(jù)。

2

SPI

1.名詞解釋

SPI 全稱 Serial Peripheral Interface,中文譯為串行外圍設(shè)備接口。

2.歷史由來

最早是由Motorola(摩托羅拉)公司開發(fā)的全雙工同步串行總線,常用于微控制器與外設(shè)之間的連接比如SD卡,液晶屏等外設(shè)。SPI沒有統(tǒng)一的協(xié)議規(guī)范,但由于其廣泛的使用,根據(jù)實際使用中大家通用的習(xí)慣形成了一個類似行規(guī)的標(biāo)準(zhǔn),具體的應(yīng)用需要實際參考特定器件手冊。

3.應(yīng)用場景

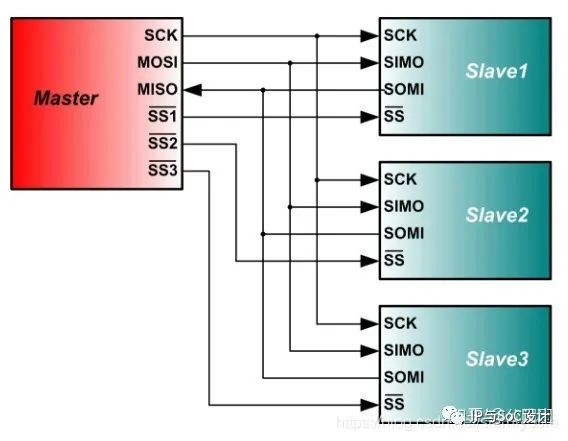

SPI用于在單個主控制器和一個或多個從設(shè)備之間交換數(shù)據(jù),譬如MCU與EEPROM、FLASH、AD轉(zhuǎn)換器的連接。SPI的兩端中提供時鐘的為Master,接收時鐘的為Slave。SPI最少采用四線連接,SCLK,SS,MOSI,MISO。SPI按幀進(jìn)行數(shù)據(jù)交換,支持的字長不限于8bit,可根據(jù)應(yīng)用特點靈活選擇消息字長。SPI是源同步時鐘協(xié)議,支持100MHz以上的高速時鐘。

4.協(xié)議解析

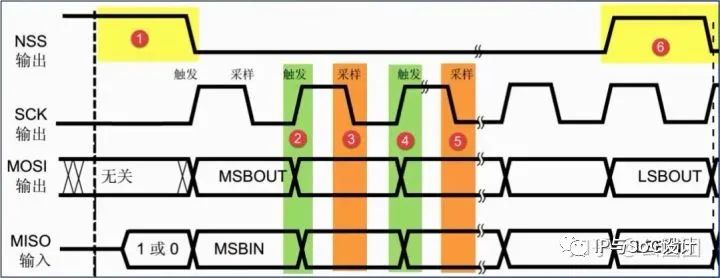

NSS電平由高變低,則產(chǎn)生起始信號;NSS電平由低變高,則產(chǎn)生停止信號。從機檢測到自己的NSS線電平被置低,則開始與主機進(jìn)行通訊;反之,檢測到NSS電平被拉高,則停止通訊。

MOSI和MISO線在SCK的每個時鐘周期傳輸一位數(shù)據(jù),開發(fā)者可以自行設(shè)置MSB或LSB先行,不過需要保證兩個通訊設(shè)備都使用同樣的協(xié)定。

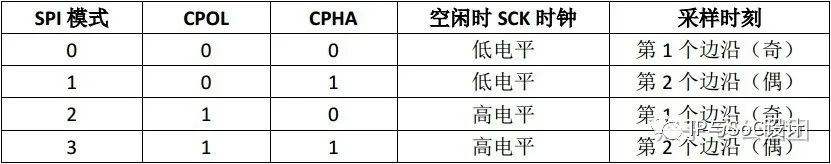

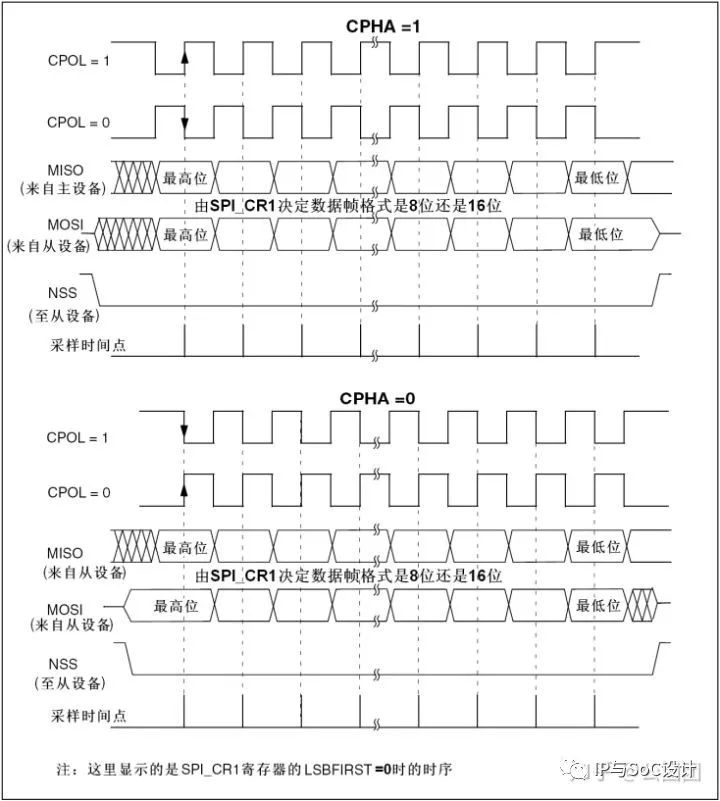

根據(jù)SCK空閑狀態(tài)的電平(CPOL)和數(shù)據(jù)采樣時刻(CPHA)的不同,SPI有四種通訊模式。Master和Slave需要工作在相同的模式下才能正常通訊,Master的MOSI如果在SCK上升沿launch數(shù)據(jù),Slave的MOSI需要在SCK的下降沿capture數(shù)據(jù),反之亦然。

當(dāng)CPHA=0時,Master需要在第一個SCK的邊沿出現(xiàn)前將數(shù)據(jù)在MOSI上準(zhǔn)備好。

5. 協(xié)議實現(xiàn)

Motorola定義5類寄存器:

SPI Control Register 1 (SPICR1)控制寄存器1,極性控制,數(shù)據(jù)長度控制

SPI Control Register 2 (SPICR2)控制寄存器2

SPI Baud Rate Register (SPIBR)波特率寄存器

SPI Status Register (SPISR)狀態(tài)寄存器

SPI Data Register (SPIDR)數(shù)據(jù)寄存器

6. SPI讀寫

SPI讀寫每筆傳輸交換一幀數(shù)據(jù),一幀數(shù)據(jù)的bit數(shù)據(jù)可以是8bit,16bit或者其他數(shù)量的bit。

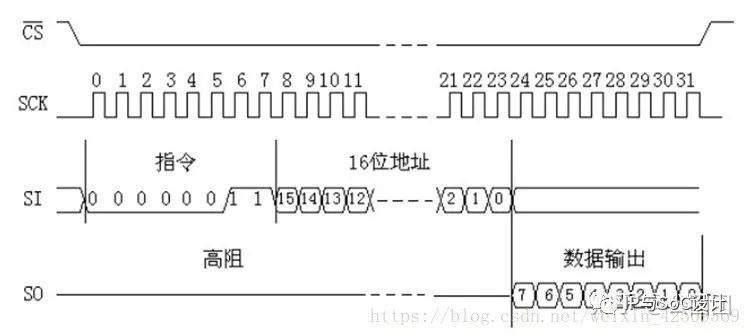

SPI讀:片選---讀指令---地址---數(shù)據(jù)讀出

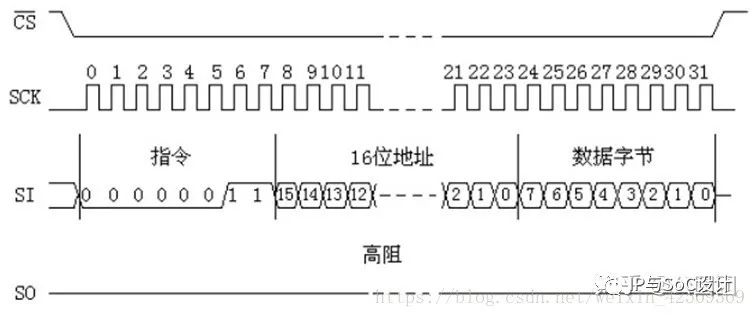

SPI寫:片選---寫指令---地址---數(shù)據(jù)寫入

7. DSPI和QSPI

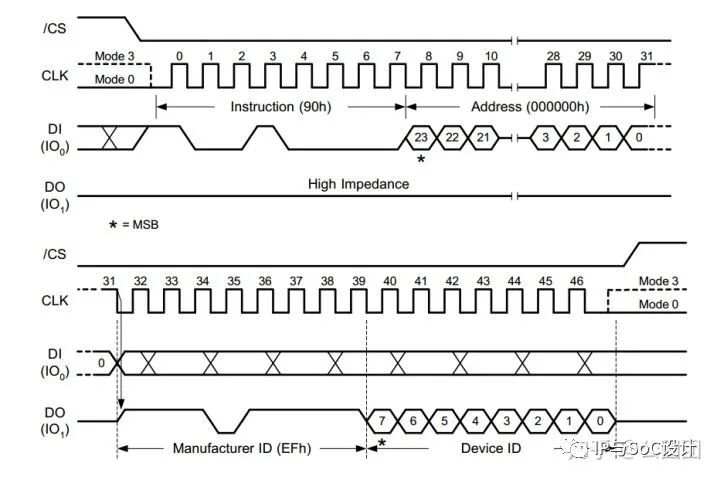

DSPI和QSPI主要用于存儲器接口,其幀格式由存儲器定義。歸納下來,QSPI的傳輸分為兩種類型,第一種類型是傳統(tǒng)的SPI的單線傳輸,第二種是QSPI的四線傳輸。

第一種類型傳輸常用于狀態(tài)和控制寄存器的讀寫,譬如讀ID。該傳輸過程采用MOSI和MISO進(jìn)行數(shù)據(jù)交換,一幀數(shù)據(jù)是46bit。此外,單線傳輸也支持?jǐn)?shù)據(jù)的讀寫。

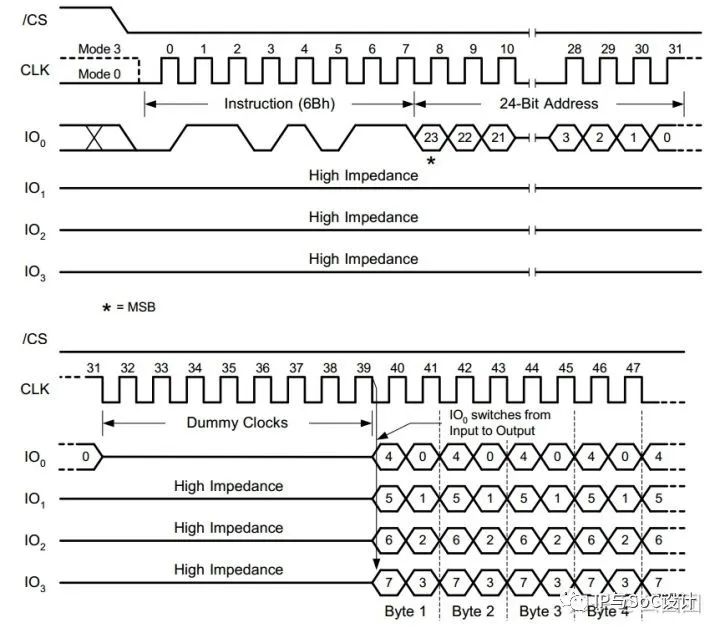

第二種類型的傳輸常用于數(shù)據(jù)的讀寫,譬如四線寫數(shù)據(jù)。該傳輸包含了兩個階段,第一個階段是命令和地址階段,第二個階段是數(shù)據(jù)傳輸階段。第一個階段,采用單線傳輸,通過MOSI向器件發(fā)送命令和地址。第二個階段,采用四線傳輸,通過四個IO向器件發(fā)送或者讀取數(shù)據(jù)。

此外,讀數(shù)據(jù)時在第一個階段和第二個階段中間會插入Dumy Clocks。

3

JTATG

1.名詞解釋

JTAG,全稱Joint Test Action Group,中文名稱聯(lián)合測試行動組。

2.歷史由來

1990年JTAG正式由IEEE的1149.1-1990號文檔標(biāo)準(zhǔn)化,在1994年,加入了補充文檔對邊界掃描描述語言(BSDL)進(jìn)行了說明。從那時開始,這個標(biāo)準(zhǔn)被全球的電子企業(yè)廣泛采用。邊界掃描幾乎成為了JTAG的同義詞。

3.應(yīng)用場景

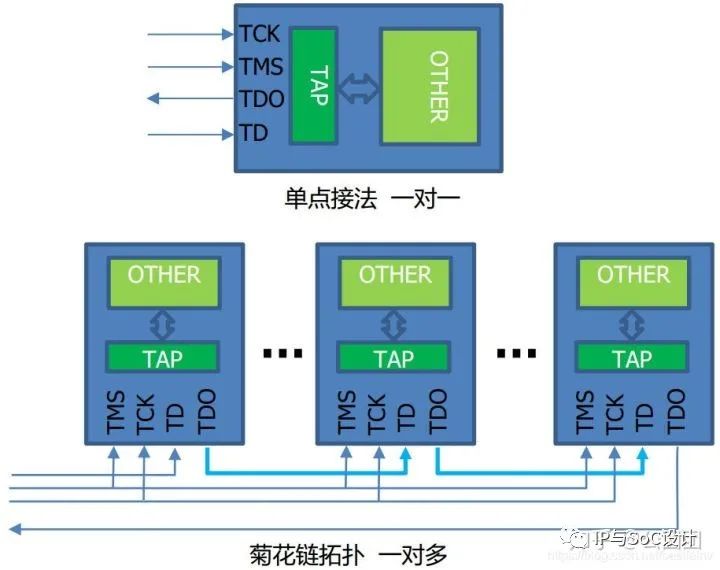

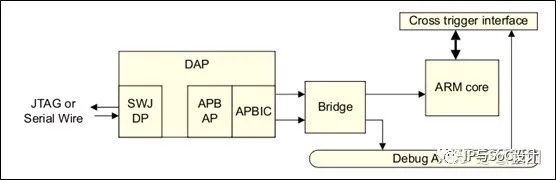

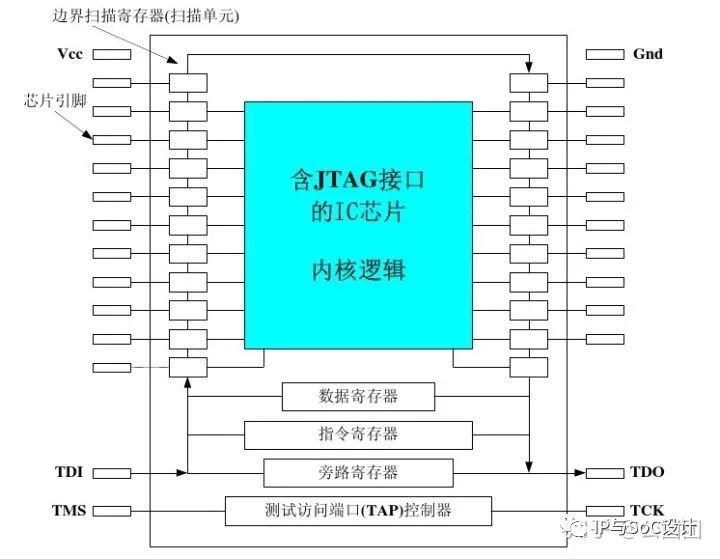

JTAG的基本原理是在器件內(nèi)部定義一個TAP(Test Access Port,測試訪問口)通過專用的JTAG測試工具對內(nèi)部節(jié)點進(jìn)行測試。當(dāng)前JTAG協(xié)議也用來對芯片進(jìn)行調(diào)試,JTAG通過器件內(nèi)部的DAP(Debug Access Port,調(diào)試訪問)訪問內(nèi)部總線。

JTAG最少使用四個信號,包括TCK,TRST,TMS,TDI和TDO,最高支持100MHz的串行數(shù)據(jù)傳輸。

-

串行

+關(guān)注

關(guān)注

0文章

237瀏覽量

34380 -

uart

+關(guān)注

關(guān)注

22文章

1271瀏覽量

103440 -

計算機芯片

+關(guān)注

關(guān)注

0文章

43瀏覽量

3657

發(fā)布評論請先 登錄

微機接口技術(shù)課件

WCDMA無線接口技術(shù)

基于IP核的SoC接口技術(shù)

談?wù)勎C原理與接口技術(shù)

人機交互接口技術(shù)簡析

微機接口技術(shù)嘗試

微機原理與接口技術(shù)

微機接口技術(shù)實用教程

MAVLink學(xué)習(xí)之路05_ MAVLink應(yīng)用編程接口分析

常見硬盤接口技術(shù)分析

SoC接口技術(shù)之低速接口分析(下)

評論