4.協(xié)議解析

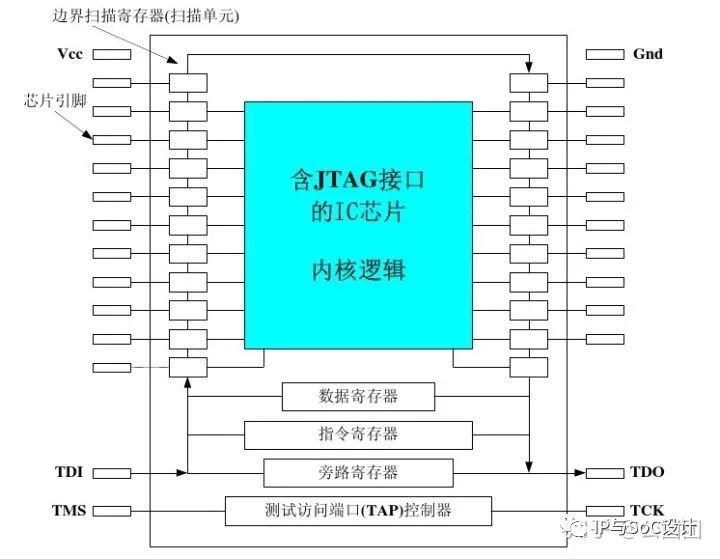

JTAG協(xié)議核心是三個寄存器和TAP狀態(tài)機。作為DEBUG的JTAG接口會在DAP中利用旁路寄存器將JTAG協(xié)議轉換為APB協(xié)議。作為DFT的JTAG接口會直接利用數(shù)據(jù)寄存器進行邊界掃描。

JTAG協(xié)議通過TMS信號控制TAP狀態(tài)機的轉換。

系統(tǒng)上電后,TAP Controller首先進入Test-LogicReset狀態(tài),然后依次進入Run-Test/Idle、Selcct-DR- Scan、Select-IR-Scan、Capture-IR、Shift-IR、Exitl-IR、Update-IR狀態(tài),最后回到Run- Tcst/Idle狀態(tài)。

在此過程中,狀態(tài)的轉移都是通過TCK信號進行驅動(上升沿),通過TMS信號對TAP的狀態(tài)進行選擇轉換的。

其中,在 Capture-IR狀態(tài)下,一個特定的邏輯序列被加載到指令寄存器中;在Shift-IR狀態(tài)下,可以將一條特定的指令送到指令寄存器中;在 Update—IR狀態(tài)下,剛才輸入到指令寄存器中的指令將用來更新指令寄存器。

最后,系統(tǒng)又回到Run—Test/Idle狀態(tài),指令生效,完成對指令 寄存器的訪問。當系統(tǒng)又返回到Run—Test/Idle狀態(tài)后,根據(jù)前面指令寄存器的內容選定所需要的數(shù)據(jù)寄存器,開始執(zhí)行對數(shù)據(jù)寄存器的工作。

其基本 原理與指令寄存器的訪問完全相同,依次為seIect—DR—Scan、Capture—DR、Shift—D、Exitl一DR、Update—DR, 最后回到Run-Tcst/Idle狀態(tài)。通過TDl和TDO,就可以將新的數(shù)據(jù)加載到數(shù)據(jù)寄存器中。經過一個周期后,就可以捕獲數(shù)據(jù)寄存器中的數(shù)據(jù),完成對與數(shù)據(jù)寄存器的每個寄存器單元相連的芯片引腳的數(shù)據(jù)更新,也完成了對數(shù)據(jù)寄存器的訪問。

5.SBW_JTAG

JTAG接口除了標準的4信號引腳外,TI還支持2信號引腳的SBW_JTAG。SBW_JTAG僅使用SBWTCK和SBWTDIO信號,常用于引腳受限芯片上。

4

1.名詞解釋

I2C總線全稱Integrated Circuit,中文名I方C總線。

2. 歷史由來

I2C 總線是由 Philips 公司開發(fā)的一種簡單、雙向二線制同步串行總線。

3.應用場景

I2C總線大量用于Host與外部設備的連接,簡化了系統(tǒng)布線。I2C是雙向二線制同步串行總線,每次可傳輸NByte數(shù)據(jù),支持100kbps/400kbps/3.4Mbps/5Mbps速率。I2C總線包含兩條信號線,串行數(shù)據(jù)SDA和串行時鐘SCL。I2C的一個總線上可以掛在多個主機和多個設備,每次數(shù)據(jù)傳輸都是由主機發(fā)起,且由主機提供時鐘。

4. 協(xié)議解析

I2C傳輸是以8bit為單元傳輸數(shù)據(jù)的,每個8bit單元數(shù)據(jù)后必須緊跟1bit回應數(shù)據(jù)。I2C的每筆傳輸包含四個階段:

(1)開始信號(S):SCL為高電平時,SDA高電平向低電平跳變,開始傳送數(shù)據(jù)。

(2)結束信號(P):SCL為高電平時,SDA由低電平向高電平跳變,結束傳送數(shù)據(jù)。

(3)響應信號(ACK):接收器在接收到8位數(shù)據(jù)后,在第9個時鐘周期,拉低SDA。

(4)數(shù)據(jù)信號(DAT): 必須為8bit,傳輸時先傳輸最高位(MSB),之后必須緊跟著ACK信號。

此外,每筆傳輸?shù)牡谝粋€8bit數(shù)據(jù)被用來作為,設備地址和訪問類型。

寫數(shù)據(jù)

若配置的方向傳輸位為“寫數(shù)據(jù)”方向,即第一幅圖的情況,廣播完地址,接收到應答信號后,主機開始正式向從機傳輸數(shù)據(jù)(DATA),數(shù)據(jù)包的大小為8 位,主機每發(fā)送完一個字節(jié)數(shù)據(jù),都要等待從機的應答信號(ACK),重復這個過程,可以向從機傳輸N 個數(shù)據(jù),這個N 沒有大小限制。當數(shù)據(jù)傳輸結束時,主機向從機發(fā)送一個停止傳輸信號(P),表示不再傳輸數(shù)據(jù)。

讀數(shù)據(jù)

若配置的方向傳輸位為“讀數(shù)據(jù)”方向,即第二幅圖的情況,廣播完地址,接收到應答信號后,從機開始向主機返回數(shù)據(jù)(DATA),數(shù)據(jù)包大小也為8 位,從機每發(fā)送完一個數(shù)據(jù),都會等待主機的應答信號(ACK),重復這個過程,可以返回N 個數(shù)據(jù),這個N 也沒有大小限制。當主機希望停止接收數(shù)據(jù)時,就向從機返回一個非應答信號(NACK),則從機自動停止數(shù)據(jù)傳輸。

讀和寫數(shù)據(jù)

除了基本的讀寫,I2C 通訊更常用的是復合格式,即第三幅圖的情況,該傳輸過程有兩次起始信號(S)。一般在第一次傳輸中,主機通過 SLAVE_ADDRESS 尋找到從設備后,發(fā)送一段“數(shù)據(jù)”,這段數(shù)據(jù)通常用于表示從設備內部的寄存器或存儲器地址(注意區(qū)分它與SLAVE_ADDRESS 的區(qū)別);在第二次的傳輸中,對該地址的內容進行讀或寫。也就是說,第一次通訊是告訴從機讀寫地址,第二次則是讀寫的實際內容。

以上通訊流程中包含的各個信號分解如下:

通訊的起始和停止信號

前文中提到的起始(S)和停止(P)信號是兩種特殊的狀態(tài),見圖 24-5。當 SCL 線是高電平時 SDA 線從高電平向低電平切換,這個情況表示通訊的起始。當 SCL 是高電平時 SDA線由低電平向高電平切換,表示通訊的停止。起始和停止信號一般由主機產生。

5

CAN

1.名詞解釋

CAN總線全稱Controller Area Network,中文名控制器局域網絡。

2.歷史由來

CAN總線由以研發(fā)和生產汽車電子產品著稱的德國BOSCH公司開發(fā)的,并最終成為國際標準(ISO 11898),是國際上應用最廣泛的現(xiàn)場總線之一。

3.應用場景

CAN總線采用差分信號線CAN_L和CAN_H進行通信,最高支持1Mbps的通信速率。CAN總線采用多主控(Multi-Master)線性拓撲結構,加入網絡節(jié)點的設備均可以向總線發(fā)送廣播消息,其他設備通過ID過濾掉不感興趣的消息。CAN總線按照幀為單位進行數(shù)據(jù)傳輸,數(shù)據(jù)幀支持1-8Byte數(shù)據(jù)傳輸。

4.協(xié)議解析

CAN總線基于多路載波偵聽+基于消息優(yōu)先級的沖突檢測和非破壞性的仲裁機制,所有節(jié)點必須都等到總線處于空閑狀態(tài)時才能往總線上發(fā)送消息,多個節(jié)點往總線上發(fā)送消息時具備最高優(yōu)先級的消息獲得總線。

通過ID仲裁,ID數(shù)值越小,報文優(yōu)先級越高。

CAN總線通過過采樣技術進行位同步,CAN控制器工作的最小時間單位(CAN時鐘周期)稱為時間份額,一個位包含多個CAN時鐘周期。

為了實現(xiàn)位同步,CAN協(xié)議把每一位的時序分解成下圖所示的四段。這四段的長度加起來即為一個CAN數(shù)據(jù)位的長度。一個完整的位由8-25個Tq組成。

當總線上出現(xiàn)幀起始信號(SOF,即隱性到顯性的邊沿)時,其他節(jié)點的控制器根據(jù)總線上的這個下降沿對自己的位時序進行調整,把該下降沿包含到SS段內。這樣根據(jù)起始幀來進行的同步稱為硬同步。因為硬同步時只是在有幀起始信號時起作用,無法確保后續(xù)一連串的位時序都是同步的,所以CAN引入了重新同步的方式。在檢測到總線上的時序與節(jié)點使用的時序有相位差時(即總線上的跳變沿不在節(jié)點時序的SS段范圍),通過延長PBS1段或縮短PBS2段來獲得同步,這樣的方式稱為重新同步。

CAN一共規(guī)定了5中類型的幀,幀也稱為報文。數(shù)據(jù)幀在CAN通信中最主要,也最復雜。數(shù)據(jù)幀以一個顯性位(邏輯0)開始,以7個連續(xù)的隱性位(邏輯1)結束。CAN總線的數(shù)據(jù)幀有標準格式(Standard Format)和擴展格式(Extended Format)的區(qū)分。

-

寄存器

+關注

關注

31文章

5336瀏覽量

120231 -

JTAG

+關注

關注

6文章

399瀏覽量

71673 -

狀態(tài)機

+關注

關注

2文章

492瀏覽量

27529 -

DEBUG

+關注

關注

3文章

93瀏覽量

19907

發(fā)布評論請先 登錄

相關推薦

微機接口技術課件

WCDMA無線接口技術

基于IP核的SoC接口技術

談談微機原理與接口技術

人機交互接口技術簡析

微機接口技術嘗試

微機原理與接口技術

微機接口技術實用教程

常見硬盤接口技術分析

SoC接口技術之低速接口分析(上)

SoC接口技術之低速接口分析(下)

SoC接口技術之低速接口分析(下)

評論