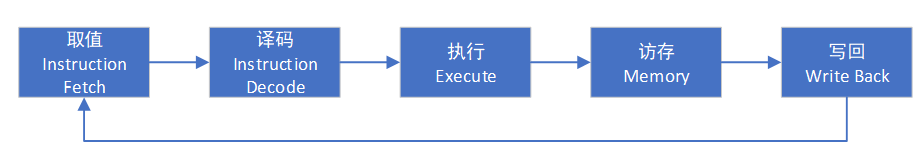

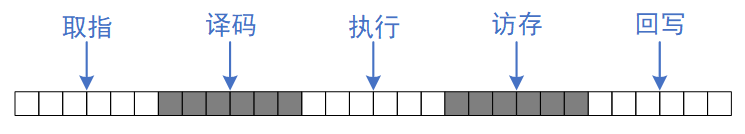

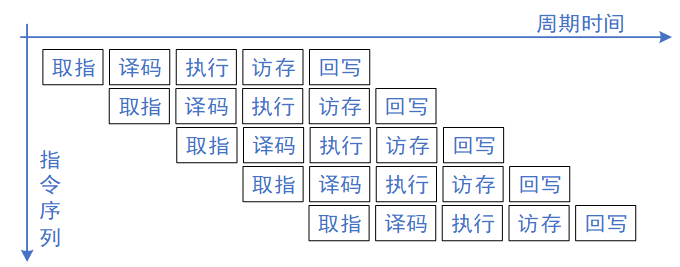

軟件在CPU上執行,采用一定的流水線執行指令,通常有取指(Instruction Fetch)、譯碼(Instruction Decode)、執行(Execute)、訪存(Memory)、寫回(Write Back)這幾步操作。如下圖所示,為5個階段的順序執行的處理器指令流,即CPU執行指令按照流水線,有一定的先后順序,單線程同一時刻只能計算出一個結果。

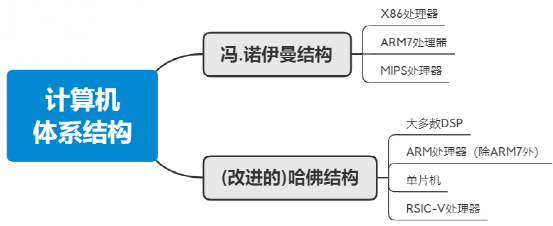

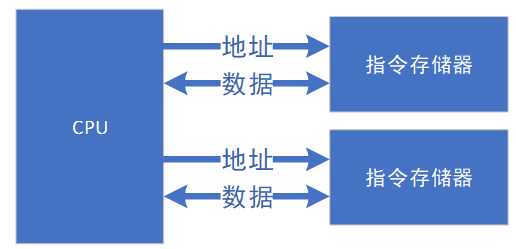

那么,我們再深入探討一下CPU的體系結構,不外乎下圖的幾種:馮.諾依曼體系結構、哈佛體系結構、改進的哈佛體系結構,這幾種結構有其各自的優勢,應用于不同的產品中,也有各自的優缺點,其中X86最典型的馮.諾依曼結構,廣泛應用于個人電腦、工作站、服務器等;而ARM是最典型的哈佛結構,廣泛應用于單片機、ARM芯片等終端芯片,如手機、平板等,終端設備等。關于具體的細分,詳見下方思維導圖。

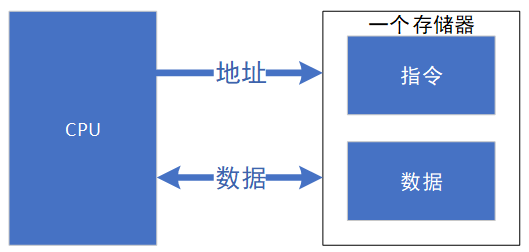

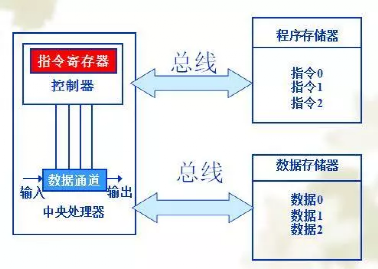

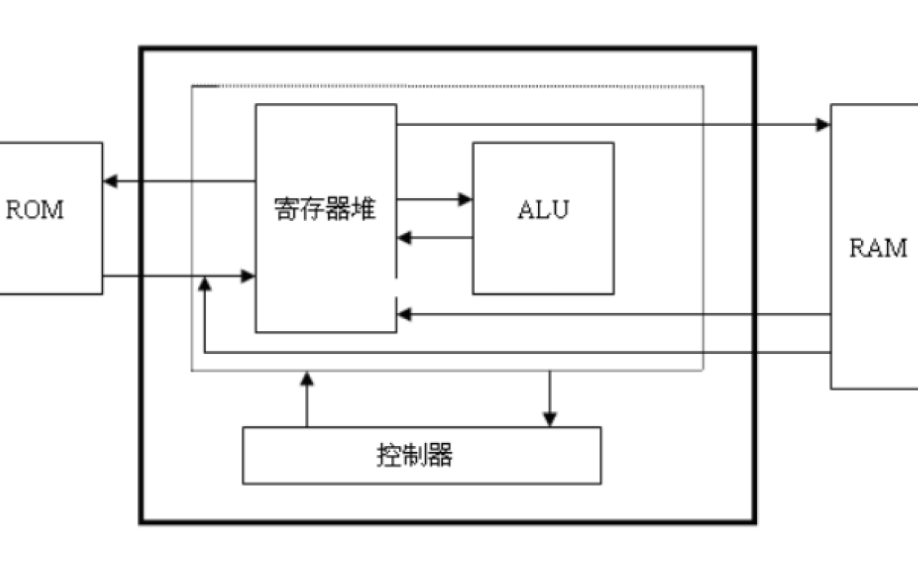

馮.諾依曼結構(von Eeumann Architecture),也稱普林斯頓結構,如下圖所示,是一種將程序指令和數據合并在一起的存儲器結構。該結構中指令和數據共用一條總線,通過分時復用的方式進行讀寫操作,結構相對簡單,總線面積較小,但缺點是效率低,無法同時取指令和數據,成為了執行的瓶頸。

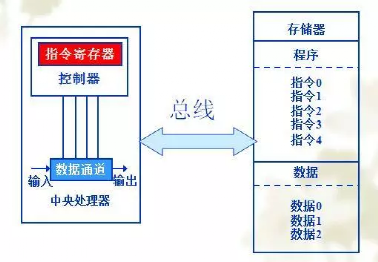

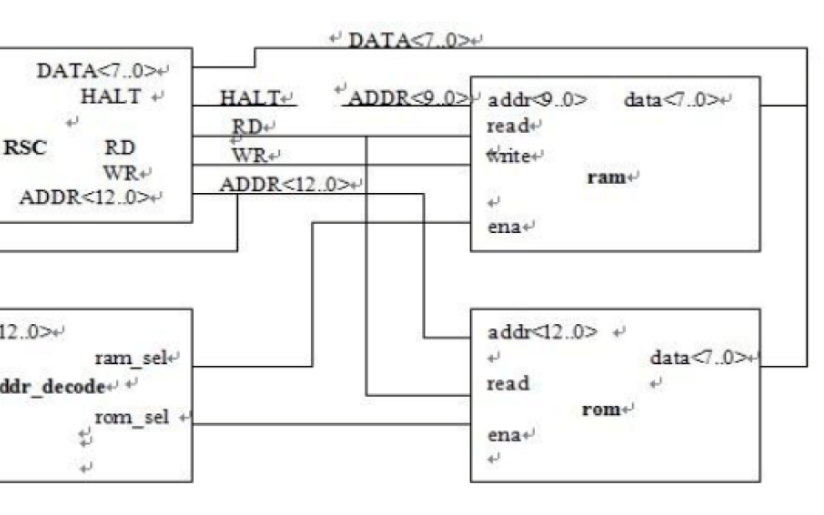

為了解決馮.諾依曼結構無法并行取指令和數據,提高計算的效率,在此基礎上提出了哈佛結構(Harvard Architecture),這是一種將程序指令和數據分開的存儲器結構,如今下圖所示。該結構由于程序的指令和數據存儲在兩個獨立的存儲器,各自有獨立的訪問總線,因此提供了更大的存儲器帶寬,減輕了程序運行時訪問內存的瓶頸。但相應的也需要獨立的存儲器,以及更大的總線面積,其中ARM就是典型的哈佛結構。

同樣采用流水線,相對于馮.諾依曼結構,哈佛結構的指令效率更高。哈佛結構在當前指令譯碼的時候,可以進行下一條指令的取指,然后在執行下一條指令的同時,又開始了第三條指令的取指。這一過程,通過指令預取,加快了原先5個步驟的流水線結構,提高了流水線的并行度。

實際上計算機體系結構發展到現在,馮.諾伊曼結構,和哈佛結構的界限已經沒有那么清晰。比如改進型的哈佛結構,指令和數據還是一起存儲在主存中,但CPU有額外的指令Cache和數據Cache(如下圖所示),在主存帶寬足夠允許的前提下,使得CPU可以同時去取指令和數據Cache,所以可以認為結構上對外是馮.諾伊曼結構,對內是哈佛結構,這就是改進型的哈佛結構。

由于本章僅在高層次上,對CPU架構設計帶來的加速進行基礎的描述,這塊就不再深入。那么,我們繼續探討,如何可以讓CPU流水線計算地更快。

1)采用更先進的工藝

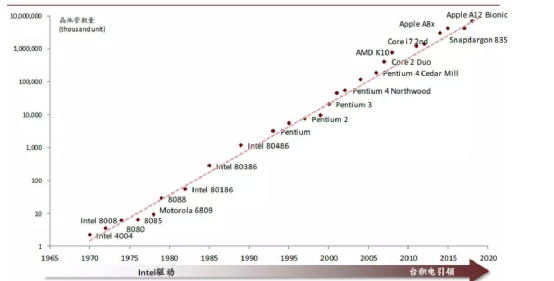

從28nm到5nm/3nm,更先進的工藝使得允許我們可以在更高的頻率下進行工作,當然也意味著更高的流片成本。典型的以28nm為例,A53可以跑到1.5GHz,而在16nm工藝下,A53可以跑到2.3GHz的主頻(以上數據僅供參考,跟具體優化有關)。

但摩爾定律的終結,意味著一味地通過工藝的升級來提高主頻,變得越來越困難,除了單純的提升工藝,增加核數量,我們還得從微架構上探索,如何跑的更快。

2)超級流水線處理器

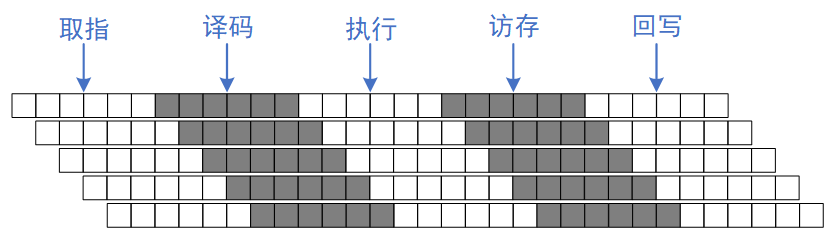

由于時鐘頻率受流水線中計算耗時最大的的,即我們的主頻需要滿足各階段的setup/hold time,如果將每一步計算拆分為更細的顆粒度,那么我們更容易滿足setup/hold time,因而可以跑在更高的主頻下——這就是超級流水線處理器/深流水線。

如下圖所謂,為細分后的超級流水線示意圖。

3)標量流水線處理器

用更細的計算顆粒,我們可以運行在更高的主頻,這是提高了流水的速率。

換個思路,大力出奇跡:如果我們擁有多條河流,那我們可以成倍的提高流水的效率,這就是標量流水線處理器,如下圖所示:

在上圖中,每條流水線執行仍然需要5個周期,但上下兩個流水線可以重疊執行。圖中用9個周期,完成了5條指令,但即當流水線滿載時,每個周期都可以完成一條指令,相比于單流水線,提高了5倍的效率。當然我們擁有了5條河流來提高速率,也是付出了面積的代價,即FPGA中常用的面積換速度的思維。

4)超標量流水線處理器

結合超級流水線,以及標量流水線的特性,也自然有了超級標量流水線結構的處理器,其流水結構如下圖所示:

超標量流水線處理器指令流

即采用了多條流水線的結構,增加了并行計算性能;同時通過流水線每一階段的顆粒度,提高了運行的主頻。當然,相對于兩個種優化的結構,超標量流水線結構也是以更大的面積為代價。目前市場上幾乎所有處理器,都是超標量流水處理器結構。

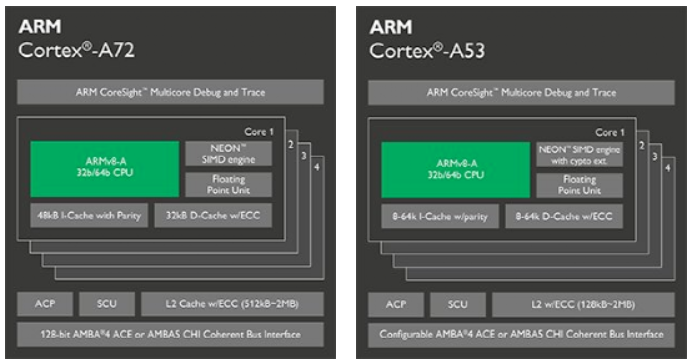

5)采用多核CPU結構

當在確定的工藝,以及一定的超標量流水線結構的處理器下,單核CPU的性能很難再實現質的飛躍,那么多核處理器的結構,再次通過面積換速度,成倍的提升了CPU的硬件性能。典型的以下圖為例,為***處理器中,4核A72 + 4核A53的大小核結構。多核處理器,在進行SOC設計時,給架構師提出了更高的挑戰;同時在軟件應用時,也對多核并行處理提出了更高的要求,如下圖所示,為AR72/A53的多核結構。

-

ARM

+關注

關注

134文章

9322瀏覽量

375538 -

存儲器

+關注

關注

38文章

7637瀏覽量

166585 -

cpu

+關注

關注

68文章

11051瀏覽量

216210 -

流水線

+關注

關注

0文章

124瀏覽量

26526 -

指令

+關注

關注

1文章

615瀏覽量

36287

原文標題:CPU是怎么實現加速的?

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【FPGA干貨分享六】基于FPGA協處理器的算法加速的實現

渦輪加速升壓(Turbo-boost)充電器可為CPU渦輪加速模式提供支持

渦輪加速升壓 (Turbo-boost) 充電器可為 CPU 渦輪加速模式提供支持

Javascript如何實現GPU加速?

使用FPGA實現CPU設計的畢業論文總結

如何使用FPGA實現八位RISC CPU的設計

為什么FPGA主頻比CPU慢,但卻可以用來幫CPU做加速

Intel Sapphire Rapids CPU,吹響反攻DPU的號角

音視頻解碼器硬件加速:實現更流暢的播放效果

評論