雙倍數據率 (DDR) 內存簡介

⊙DDR ⊙MEMORY

串行數據傳輸與并行數據傳輸相比具有重要優勢,在許多系統中,這些優勢足以證明添加串行化和反串行化的并行數據電路是合理的,以便它可以作為串行數據傳輸。然而,計算機內存是一個應用領域,其中并行數據傳輸仍然很普遍。由于它們可以同時讀取和寫入許多數字信號,因此并行接口速度很快,設計人員一直在尋找使它們更快的方法。

一種古老但仍然相關的技術可實現數據傳輸速率的大幅提高稱為雙泵,此功能可將內存系統轉變為雙倍數據速率 (DDR) 內存系統。“單泵”存儲系統采用歷史悠久的策略將數據從一個 IC 同步移動到另一個 IC。基本上,邏輯信號每個時鐘周期改變一次,并在時鐘的上升沿或下降沿由接收器采樣。在此方案中,字的傳輸速率不能超過時鐘頻率。

例如,如果時鐘以 133 MHz 運行,(理想情況下)每秒傳輸 1.33 億字。請注意,位傳輸速率取決于系統架構,因為不同的計算系統使用不同的字長——8 位、16 位等。雙泵系統可以在133 MHz達到 266 MT/s(每秒百萬次傳輸)的速度。

在本文中,我們將了解單數據速率接口和雙數據速率接口之間的差異、我們使用 DDR 的原因及其應用。

0****1

**### SDR 與 DDR

**

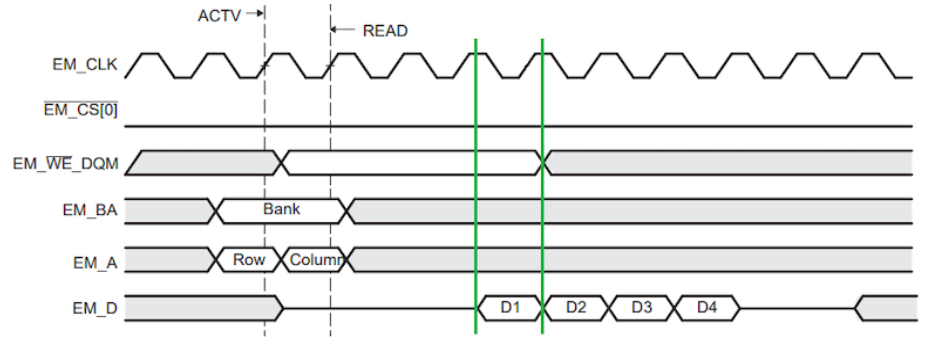

下面圖 1 中顯示的時序圖是單數據速率存儲器接口的示例。

首先,使用 EM_BA 信號選擇存儲體,并通過 EM_A 信號建立行和列地址。數據字 D1、D2、D3 和 D4 在 EM_D 引腳上輸出。注意一個數據字如何占據 EM_CLK 信號的整個周期。

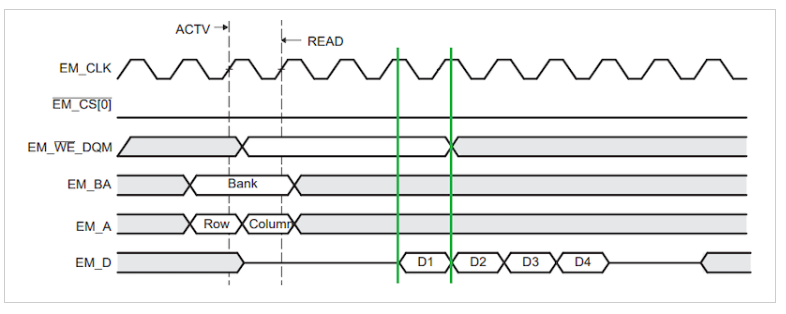

下一個時序圖2描繪了一個雙倍數據速率接口。

“DQ”線代表數據信號,陰影區域之間的無陰影 X 形區域表示從一個字到下一個字的轉換。可以看到每個字只需要一個完整時鐘周期的一半。請記住,該芯片使用差分時鐘,這就是時序圖具有 CK 信號和互補 CK# 信號的原因。

0****2

**為什么雙倍數據速率?

你可能想知道為什么工程師在本可以將時鐘頻率提高兩倍的情況下還要費心為 DDR 信號創建新邏輯。對這個決定的主要解釋包含在代表高速研發的兩個詞中:信號完整性。

高頻信號這里的“高頻”是相對于給定技術時代或應用場景的限制來理解的,它們是電路板設計人員非常驚愕的一個來源。這些信號的特征:

它們也更難使用測試設備進行表征和故障排除。例如,示波器的模擬和數字帶寬有限,隨著頻率的增加,它會在波形中引入更多失真。

因此,在嘗試實現更高的時鐘速率之前,從現有時鐘速率中提取盡可能多的吞吐量是有意義的。通過從單一數據速率接口轉向 DDR 接口,設計人員可以在不改變系統最大信號頻率的情況下顯著提高數據傳輸速率。即使數據信號的最大頻率增加了兩倍,所有這一切都可以實現,這個新的數據頻率不高于先前的時鐘頻率。

0****3

**DDR 內存應用

**

“雙泵”是一種通用功能,已用于各種并行數據傳輸接口。甚至高速數據轉換器也采用了這種技術。例如, 下圖所示的模數轉換器 (ADC) 時序圖中,一個樣本在一個完整時鐘周期所需的時間內被數字化,但數字輸出使用 DDR 時序,因為兩個數據位復用到每個輸出。

然而,DDR 并行傳輸仍然與計算系統中使用的 SDRAM(同步動態隨機存取存儲器)密切相關。幾十年來,工程師們一直在努力提高計算機移動和處理數字數據的速度,而 DDR 信號使他們能夠在保持當時可行的最大時鐘頻率的同時將吞吐量提高一倍。

1998 年發布的第一代 DDR SDRAM 支持高達 200 MHz 的時鐘頻率和高達 400 MT/s 的相應傳輸速率。然后是 DDR2、DDR3、DDR4,最后是我們目前使用的 DDR5。DDR5 的最大傳輸速率超過 7 GT/s。

-

數據傳輸

+關注

關注

9文章

1884瀏覽量

64576 -

DDR

+關注

關注

11文章

712瀏覽量

65326 -

串行數據

+關注

關注

0文章

52瀏覽量

16541

發布評論請先 登錄

相關推薦

用Cyclone FPGA實現雙倍數據率輸入輸出接口

JEDEC即將完成DDR4內存標準關鍵屬性

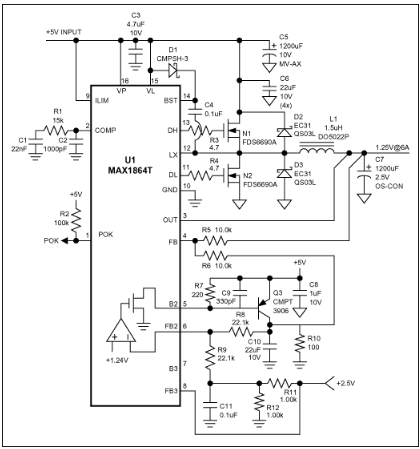

電源設計小貼士:DDR內存電源

DDR SDRAM是擁有著雙倍數據傳輸率的SDRAM

介紹一款灌電流和拉電流雙倍數據速率 (DDR) 終端穩壓器

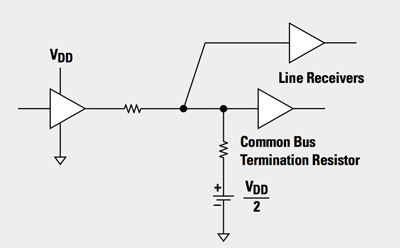

DDR內存終端電源

GDDR和DDR代表什么?GDDR和DDR內存有什么區別?

什么是DDR4內存模塊

一文讀懂DDR內存基礎知識

雙倍數據率 (DDR) 內存簡介

雙倍數據率 (DDR) 內存簡介

評論