在做STA Signoff時(shí),對(duì)于Setup來說選擇Slow Corner,也就是慢工藝(SS)、低壓(Low Voltage)、高溫(High Temperature);

對(duì)于Hold來說選擇Fast Corner,也就是快工藝(FF)、高壓(High Voltage)、低溫(Low Temperature)。

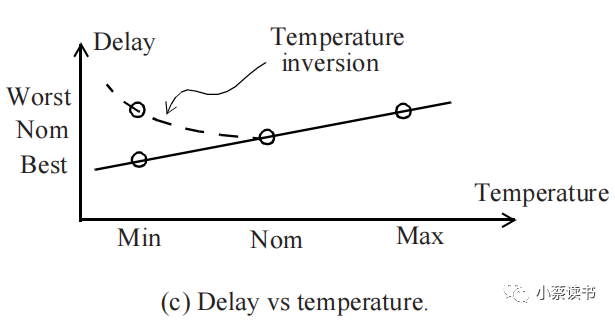

可是到了小尺寸工藝(65nm以下)發(fā)生一些變化,如下圖。

低溫相對(duì)于高溫延遲會(huì)變大,也就是出現(xiàn)了所謂的溫度反轉(zhuǎn)效應(yīng)(Temperature Inversion)。

Corner介紹

1.wc(worst-case): SS,VDD-%10,125C,一般delay最大;

2.wcl (worst-caselow-temperature):SS,VDD-%10,m40C,溫度反轉(zhuǎn)效應(yīng)下delay最大;

3.lt(low-temperature,也叫best case):FF,VDD+10%,m40C,一般delay最小;

4.ml(max-leakage):FF,VDD+10%,125C,溫度反轉(zhuǎn)效應(yīng)下delay最小。

溫度反轉(zhuǎn)效應(yīng)后果

導(dǎo)致STA signoff corner至少增加了一倍,也就是說run time最少增加一倍(對(duì)于大規(guī)模芯片真是一件麻煩事),需要fix的violation也有所增加。

溫度反轉(zhuǎn)效應(yīng)帶來了這么多工作量,它到底為什么會(huì)發(fā)生呢?

溫度反轉(zhuǎn)效應(yīng)原理

隨著溫度的升高,晶格的熱振動(dòng)會(huì)增加,增加了電子的散射(可以理解為電子的碰撞增加,不利于電子流動(dòng)),所以Metal的電阻會(huì)增加。在半導(dǎo)體中也有類似的效果,載流子(電子和空穴)的遷移率隨著溫度的升高而降低。

但是在半導(dǎo)體中,隨著MOS晶體管的電源電壓降低,發(fā)生了有趣的現(xiàn)象:在較低電壓下,MOS 器件的延遲隨溫度升高而降低,而不是增加。

畢竟普遍的看法是,隨著溫度的升高,遷移率會(huì)降低,因此人們會(huì)預(yù)期電流會(huì)降低,隨后延遲也會(huì)增加。這種效應(yīng)也稱為低電壓反向溫度依賴性。

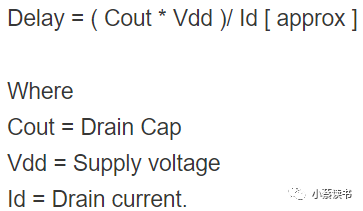

首先讓我們看看,在一個(gè)簡(jiǎn)化的模型中,MOS 晶體管的延遲取決于什么。

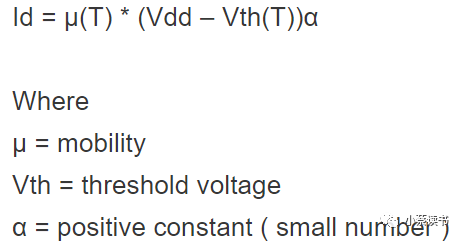

現(xiàn)在讓我們看看漏極電流取決于什么。

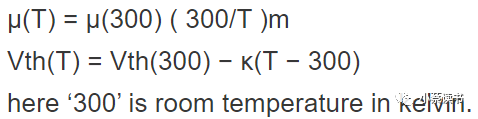

可以看到,Id 取決于遷移率 μ 和閾值電壓 Vth。讓我們檢查遷移率和閾值電壓對(duì)溫度的依賴性。

遷移率和閾值電壓均隨溫度升高而降低。但是遷移率的降低意味著更少的漏極電流和更慢的器件,而閾值電壓的降低意味著增加漏極電流和更快的器件。

最終的漏極電流取決于在給定的電壓和溫度對(duì)下哪個(gè)趨勢(shì)占主導(dǎo)地位。在高電壓下,遷移率決定了漏極電流,而在低電壓下,閾值電壓主導(dǎo)著漏極電流。

這就是為什么:在較高電壓下,器件延遲隨溫度增加而增加;在較低電壓下,器件延遲隨溫度增加降低。

審核編輯:劉清

-

MOS管

+關(guān)注

關(guān)注

108文章

2487瀏覽量

68858 -

晶體管

+關(guān)注

關(guān)注

77文章

9881瀏覽量

139828 -

STA

+關(guān)注

關(guān)注

0文章

52瀏覽量

19138 -

VDD

+關(guān)注

關(guān)注

1文章

315瀏覽量

34422

原文標(biāo)題:溫度越低延遲越小?看看什么是溫度反轉(zhuǎn)效應(yīng)

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

射頻設(shè)計(jì)中的互調(diào)失真到底是如何發(fā)生的呢?如何預(yù)防?

什么是串聯(lián)諧振,為什么會(huì)發(fā)生串聯(lián)諧振?

運(yùn)算放大器產(chǎn)品中的“典型值”到底是什么意思呢?它的變化范圍是多大呢?

Type-C接口它到底有哪些優(yōu)勢(shì)呢?

SMC、NVRAM、PRAM到底是什么呢?又如何重置呢?

為什么用Simulink生成stm32代碼會(huì)發(fā)生錯(cuò)誤呢

為什么用USART_SendData()發(fā)送數(shù)據(jù)會(huì)發(fā)生錯(cuò)誤呢

為什么手機(jī)電池會(huì)發(fā)生爆炸呢?那種電池沒有爆炸危險(xiǎn)

向從未有人到過的星球發(fā)送信號(hào)時(shí),會(huì)發(fā)生什么呢?

SVM與神經(jīng)網(wǎng)絡(luò)結(jié)合會(huì)發(fā)生什么?

【虹科Pico汽車示波器】數(shù)學(xué)通道的應(yīng)用(五)-反轉(zhuǎn)

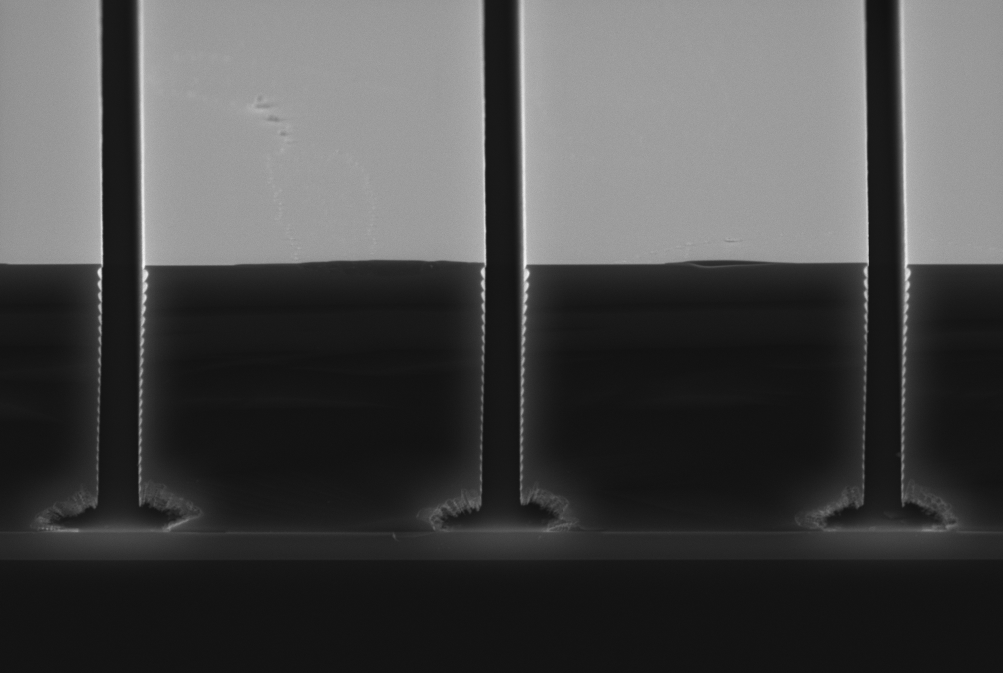

什么是凹槽效應(yīng)?什么原因引起的?怎么抑制這種異常效應(yīng)呢?

什么是干法刻蝕的凹槽效應(yīng)?凹槽效應(yīng)的形成機(jī)理和抑制方法

評(píng)論