將受控振蕩器所需的頻率調(diào)諧范圍分成離散頻帶是一種常用技術(shù)。擁有多個(gè)頻段的優(yōu)勢在于可以覆蓋較寬的調(diào)諧范圍,同時(shí)在每個(gè)頻段內(nèi)保持相對較低的壓控振蕩器 (VCO) 增益。低 VCO 增益有利于實(shí)現(xiàn)低 VCO 相位噪聲。要求頻段重疊。調(diào)諧波段隨數(shù)字波段控制信號而改變。

當(dāng)在鎖相環(huán) (PLL) 中使用具有離散調(diào)諧頻帶的振蕩器時(shí),必須在 PLL 進(jìn)入鎖相之前選擇所需的頻帶。這個(gè)必要的步驟有很多名稱(頻段校準(zhǔn)、自動(dòng)頻段選擇、頻段選擇等),但思路是一樣的:在允許 PLL 鎖定之前選擇正確的頻段。

校準(zhǔn)頻帶的一種直接方法是讓兩個(gè)計(jì)數(shù)器同步,一個(gè)用參考時(shí)鐘計(jì)時(shí),另一個(gè)用反饋時(shí)鐘計(jì)時(shí),反饋時(shí)鐘是 VCO 輸出的分頻版本。分頻發(fā)生在稱為多模分頻器 (MMD) 的模塊中。

計(jì)數(shù)器被強(qiáng)制同時(shí)啟動(dòng)并允許計(jì)數(shù)到預(yù)定值。達(dá)到該值的計(jì)數(shù)器被標(biāo)記為獲勝者;因此,該時(shí)鐘的頻率更高。

使用有關(guān)哪個(gè)計(jì)數(shù)器獲勝的信息,可以增加或減少 VCO 的頻帶控制以使頻率更接近。該算法在帶校準(zhǔn)塊 (BCAL) 中實(shí)現(xiàn)。無需等待包括整個(gè) PLL 和其他電路的昂貴的 ASIC 制造運(yùn)行,您可以實(shí)施頻段校準(zhǔn)算法并在 FPGA 上對其進(jìn)行測試。這篇文章告訴你如何。

VCO 頻帶校準(zhǔn) (BCAL)

在通信芯片中,頻率合成器是無處不在的功能塊。頻率合成器被寬泛地定義為產(chǎn)生與參考頻率成正比的輸出頻率的 PLL。比例常數(shù)是整數(shù)或?qū)崝?shù)的特定子集,具體取決于合成器的實(shí)現(xiàn)。

合成器在接收機(jī)前端的一種用途是創(chuàng)建本地振蕩器輸入到混頻器,混頻器將接收到的射頻 (RF) 信號下變頻為中頻。通道選擇是通過設(shè)置合成器的比例常數(shù)來實(shí)現(xiàn)的。一般來說,RF = Ndiv * REF,其中RF為輸出頻率,Ndiv為比例常數(shù),REF為參考頻率。

Ndiv 可以是整數(shù)比,N/R,其中 N 是 VCO 輸出的整數(shù)分頻值,R 是用于對參考振蕩器進(jìn)行分頻的另一個(gè)整數(shù)分頻比。如果需要更精細(xì)的頻率分辨率,可以將 N 值添加到 sigma-delta 調(diào)制代碼,該代碼抖動(dòng)分頻器函數(shù)并提供 REF/2^(# sigma-delta 累加器位) 的小數(shù)分辨率。

頻率合成器將固定頻率的晶體振蕩器乘以所需的頻率。PLL 充當(dāng)閉環(huán)負(fù)反饋系統(tǒng)來實(shí)現(xiàn)這種乘法。MMD 的工作是將 VCO 輸出的頻率除以整數(shù)值 N。

將該信號的相位與參考信號的相位進(jìn)行比較,對相位差進(jìn)行濾波以去除高頻分量。過濾后的信號用作 VCO 的電壓控制。如果 MMD 的輸出與參考之間存在任何相位差,VCO 上的控制電壓將進(jìn)行調(diào)整以校正該相位差。

對于手頭的應(yīng)用,合成器需要產(chǎn)生 3,000 至 4,000 MHz 的頻率。VCO 的連續(xù)調(diào)諧是通過改變作為并聯(lián)電感-電容 (LC) 諧振電路一部分的變?nèi)?/span>二極管兩端的偏置電壓來實(shí)現(xiàn)的。制造技術(shù)將控制電壓限制在大約 1.5 V 的變化范圍內(nèi)。很難制造一個(gè)變?nèi)荻O管,其電抗變化足以引起 1,000 MHz 的頻率變化,而控制電壓變化僅為 1.5 V。

此外,1,000 MHz/1.5 V 的大 VCO 增益會(huì)使 PLL 容易受到高相位噪聲的影響。由于這些原因,調(diào)諧范圍被分成離散的頻段。離散頻帶是通過將二進(jìn)制加權(quán)電容器添加到并聯(lián) LC 儲能電路來實(shí)現(xiàn)的。它們根據(jù)數(shù)字頻段設(shè)置打開或關(guān)閉。必須先設(shè)置頻帶,然后才能允許 PLL 以連續(xù)方式鎖定和跟蹤。

BCAL 電路作為第二個(gè)反饋環(huán)路運(yùn)行,通過其頻帶輸入控制 VCO。在波段校準(zhǔn)期間,VCO 控制電壓固定在一個(gè)方便的電壓,通常是其允許控制電壓范圍的中點(diǎn)。相位檢測器在波段校準(zhǔn)期間也被禁用。

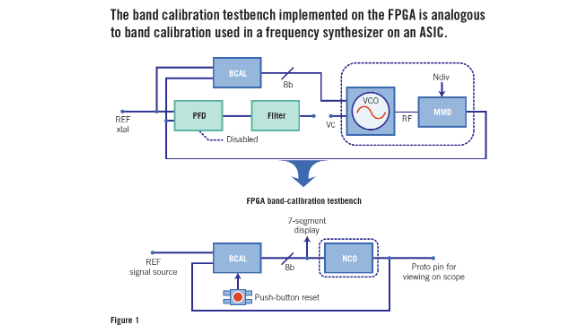

我的目標(biāo)是設(shè)計(jì)和測試頻段校準(zhǔn)算法,然后再將其與 RF 接收器 ASIC 上的 PLL 集成。為此,一個(gè)類似于 PLL 的系統(tǒng)在進(jìn)行頻帶校準(zhǔn)時(shí)完全由可以在 FPGA 上實(shí)現(xiàn)的電路構(gòu)建。由于 VCO 和 MMD 集總在一起充當(dāng)可編程振蕩器,輸出頻率在參考頻率附近,因此它們的功能可以通過數(shù)控振蕩器 (NCO) 建模,如圖 1所示。

為了使合成器具有低相位噪聲,晶體生成頻率參考。參考頻率通常為數(shù)十 MHz,遠(yuǎn)低于當(dāng)今 FPGA 上可實(shí)現(xiàn)的邏輯速度。BCAL算法本身可以用數(shù)字技術(shù)來描述和設(shè)計(jì)。

在簡單的情況下,它的輸入是兩個(gè)時(shí)鐘,即 NCO 的參考和輸出;它的輸出是 NCO 的頻帶信號。頻帶校準(zhǔn)、NCO 和外部應(yīng)用的參考信號的組合形成了一個(gè)帶負(fù)反饋的閉環(huán)系統(tǒng),類似于在其頻帶校準(zhǔn)模式下運(yùn)行的 PLL,所有這些都可以在 RTL 中編碼,然后在 FPGA 上進(jìn)行測試花錢制造 ASIC。

你需要什么

1. FPGA 及其編程軟件

2. Matlab/Simulink進(jìn)行算法開發(fā)和驗(yàn)證

3、產(chǎn)生參考時(shí)鐘的信號源,如10~15MHz

4.調(diào)試用示波器一臺

我使用Matlab/Simulink 進(jìn)入初始設(shè)計(jì)和testbench。Fixed-Point Toolbox 和 Simulink Fixed Point 對定點(diǎn)數(shù)的支持有助于使模型準(zhǔn)確反映 RTL 中的實(shí)現(xiàn)。RTL 代碼用 verilog 編寫,并在 Altera 的 Stratix II DSP 開發(fā)套件上運(yùn)行。

在 Altera 的 Quartus II 軟件中,F(xiàn)PGA 的所有功能都可以完成:設(shè)計(jì)輸入、功能仿真、時(shí)序仿真、綜合、適配、使用設(shè)計(jì)配置 FPGA 和調(diào)試。當(dāng)我實(shí)時(shí)測試波段校準(zhǔn)時(shí),我使用了信號源和示波器。

設(shè)計(jì)和原型制作過程 設(shè)計(jì)

和原型制作過程是以下熟悉步驟的迭代:1. 設(shè)計(jì)輸入;2.測試;3、調(diào)試;4. 轉(zhuǎn)至 2。此循環(huán)根據(jù)需要重復(fù)多次,直到達(dá)到所需的功能。

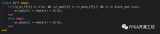

首先,我將 NCO 構(gòu)建為 Simulink 子系統(tǒng)。NCO Simulink 模型是從我在www.mindspring.com/~tcoonan/nco.v網(wǎng)站上找到的 NCO 的 verilog 逆向工程得到的。NCO 基于可編程模計(jì)數(shù)器。其輸出頻率等于Fs*(BAND+STEP)/MOD 其中STEP和MOD為固定值,BAND為8位頻帶信號。

NCO 的功能通過使用 Fs=11MHz 運(yùn)行瞬態(tài)仿真并掃描 0 至 255 的 BAND 值并計(jì)算終輸出頻率來驗(yàn)證。由此產(chǎn)生的輸出頻率與 BAND 或頻帶調(diào)諧曲線是單調(diào)的,但不是完全線性的。由于它是單調(diào)的,因此被認(rèn)為可以在 BCAL 的閉環(huán)測試設(shè)置中使用。

在確定 NCO 具有單調(diào)調(diào)諧曲線并且可以產(chǎn)生 10 到 14 MHz 范圍內(nèi)的頻率(大約是 PLL 的參考頻率)之后,我構(gòu)建了 BCAL 模型。BCAL 算法通過競爭兩個(gè)相同的 10 位計(jì)數(shù)器來工作。一個(gè)計(jì)數(shù)器由參考計(jì)時(shí);NCO 為對方計(jì)時(shí)。

由于它們都從 0 開始,個(gè)達(dá)到常量 HIT_VALUE 的計(jì)數(shù)器由較高的頻率計(jì)時(shí)。為了確定哪個(gè)計(jì)數(shù)器先到達(dá) HIT_VALUE,每個(gè)計(jì)數(shù)值不斷與 HIT_VALUE 進(jìn)行比較,并且兩個(gè)比較結(jié)果的異或用于將“1”輸入 D 觸發(fā)器。

當(dāng)兩個(gè)計(jì)數(shù)值都小于 HIT_VALUE 時(shí),比較器都輸出 0,XOR 結(jié)果為 0。在其中一個(gè)值超過 HIT_VALUE 的瞬間,XOR 輸出轉(zhuǎn)換為 1 并在 DFF 輸出上捕獲 1。此后的某個(gè)時(shí)間,另一個(gè)計(jì)數(shù)值將達(dá)到 HIT_VALUE,并且 XOR 結(jié)果返回 0。

另一個(gè)比較器用于將參考計(jì)數(shù)器與常量 RESET_VALUE 進(jìn)行比較,當(dāng)計(jì)數(shù)超過此值時(shí),兩個(gè)計(jì)數(shù)器都將重置為 0,比賽重新開始。如果 HIT_VALUE 為 230,則合理的 RESET_VALUE 為 240。同時(shí),有關(guān)哪個(gè)時(shí)鐘更快的信息位用作二進(jìn)制搜索塊的輸入。

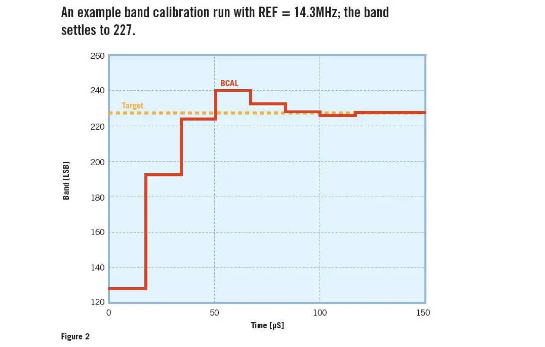

二進(jìn)制搜索塊保存當(dāng)前波段輸出值,并根據(jù)贏得比賽的時(shí)鐘確定下一個(gè)波段值。二進(jìn)制搜索塊從其當(dāng)前輸出中添加或減去適當(dāng)?shù)亩M(jìn)制加權(quán)值。對于 8 位頻段,初始頻段值為 128 的中間值,連續(xù)進(jìn)行七次比賽以填充從 MSB 到 LSB 的 8 位。圖 2顯示了 BCAL 算法的示例運(yùn)行。

在 Simulink 中根據(jù)邏輯門、比較器、寄存器、延遲和查找表構(gòu)建頻帶校準(zhǔn)算法后,將設(shè)計(jì)輸入到 Quartus II 軟件中。為了使調(diào)試更容易,Simulink 模型中的每條線都被命名。

在翻譯過程中,我在 Verilog 代碼中對信號使用了相同的名稱。如果信號源自 Simulink 模型中的寄存器(或觸發(fā)子系統(tǒng)中的延遲),我將其設(shè)為 Verilog 中的寄存器;否則信號是電線。因此,從 Simulink 原始子系統(tǒng)到 Verilog 的設(shè)計(jì)入口非常簡單。

以類似于在 Simulink 中完成的測試的方式,所有子模塊都在 Quartus II 中進(jìn)行了仿真和驗(yàn)證。在確認(rèn)子模塊的功能后,制作了整個(gè) BCAL 的測試原理圖。測試原理圖包括由 BCAL 頻帶輸出控制的 NCO。

為了完成循環(huán),NCO 輸出用作 BCAL 的時(shí)鐘輸入之一。BCAL 參考輸入通過其中一個(gè) FPGA 引腳連接到電路板上的 SMA 連接器,因此它可以使用外部信號源計(jì)時(shí)。

BCAL測試平臺綜合擬合,時(shí)序網(wǎng)表仿真。很明顯,設(shè)計(jì)中存在錯(cuò)誤,因?yàn)槟承╊l帶位進(jìn)入未定義狀態(tài),在 Quartus II 中顯示為“U”。

該錯(cuò)誤來自計(jì)數(shù)器值與 HIT_VALUE 的異步比較。在注冊這些比較結(jié)果并將異步數(shù)據(jù)路徑重新定時(shí)到參考時(shí)鐘之后,設(shè)計(jì)功能在仿真中是正常的。下一步是將設(shè)計(jì)加載到 FPGA 上并通過測量進(jìn)行驗(yàn)證。

通過以大約 100 kHz 的增量將信號源生成的參考頻率從 10 MHz 更改為 14 MHz 來進(jìn)行測試。測試設(shè)置如圖 3所示。在每個(gè)參考頻率,頻段校準(zhǔn)由與按鈕相關(guān)的重置啟動(dòng)。開關(guān)去抖動(dòng)本來可以使測試臺更干凈,但不是必需的。

開關(guān)彈跳引起的多次復(fù)位導(dǎo)致算法反復(fù)重新開始;當(dāng)開關(guān)停止彈動(dòng)時(shí),BCAL 正常工作。8 位波段值映射到 FPGA 板上的兩個(gè) 7 段顯示器,以十六進(jìn)制顯示終波段值。

BCAL 算法在 146 μs (= 7*230/11 MHz) 內(nèi)完成,因此人類觀察者只會(huì)看到終值。讀數(shù)便于與 Simulink 模型的理論值進(jìn)行比較。通過這種方式,BCAL 算法針對從其到頻帶值的 50 個(gè)可能頻率進(jìn)行了通過/失敗測試。

潛在的陷阱和技巧

這種特殊設(shè)計(jì)的挑戰(zhàn)之一是它的異步特性。NCO 時(shí)鐘的頻率在頻帶校準(zhǔn)期間發(fā)生變化,BCAL 中的一些邏輯元件取決于該時(shí)鐘邊沿的時(shí)序。同樣,其他邏輯元件與參考時(shí)鐘邊沿同步變化。

FPGA設(shè)計(jì)軟件不利于異步設(shè)計(jì)。進(jìn)行異步設(shè)計(jì)并非不可能,但如果您必須查看有關(guān)警告集合的文檔以確定您的代碼是否按預(yù)期進(jìn)行,請不要感到驚訝。由于參考頻率永遠(yuǎn)不會(huì)改變,因此修改了設(shè)計(jì)以使所有數(shù)據(jù)路徑與參考時(shí)鐘同步。

當(dāng)數(shù)據(jù)路徑需要跳轉(zhuǎn)時(shí)鐘域時(shí),它會(huì)使用級聯(lián)寄存器重新定時(shí),以限度地減少亞穩(wěn)態(tài)。同樣,另一個(gè)陷阱是沒有注冊組合比較器輸出。這些都是實(shí)際硬件中出現(xiàn)的問題示例,但可能不會(huì)出現(xiàn)在 Simulink 的理想模型中,除非您將它們顯式添加到您的模型中。

為了簡化 Simulink 模型到 RTL 的遷移,請嘗試使用在您選擇的 RTL 語言中作為原語的 Simulink 功能塊。例如,XOR、AND 和大于等邏輯函數(shù)直接從 Simulink 映射到 Verilog。Simulink 中的延遲或顯式 DFF 在 Verilog 中建模為寄存器。

我還建議為 Simulink 模型中的所有信號命名,并在 Verilog 代碼中使用相同的名稱。在 Simulink 中首先使用浮點(diǎn)數(shù)據(jù)類型構(gòu)建模型是可以的,但如果您將浮點(diǎn)設(shè)計(jì)遷移到定點(diǎn),它將簡化編碼過程并使設(shè)計(jì)更易于調(diào)試。

終結(jié)果

在 FPGA 上運(yùn)行 RTL 代碼并根據(jù)測量數(shù)據(jù)判斷設(shè)計(jì)功能正常并滿足規(guī)范后,就可以在 ASIC 上實(shí)現(xiàn)代碼了。邏輯綜合和布局是用 Cadence 的 Encounter 軟件完成的。作為的檢查,我模擬了生成的邏輯網(wǎng)表以及提取的帶有寄生電阻器和電容器的布局網(wǎng)表,以確保在 Encounter 的綜合和布局布線后功能仍然正常。

在這些模擬中,功能檢查正常。從那時(shí)起,包括頻率合成器的 RF 接收器 ASIC 被制造出來,芯片的測量顯示頻率合成器在其可能的輸出頻率范圍內(nèi)鎖相。這意味著波段校準(zhǔn)功能正常。因此,設(shè)計(jì)團(tuán)隊(duì)可以專注于從 ASIC 的模擬部分中獲得更好的性能。

在將設(shè)計(jì)提交到 ASIC 之前,在 FPGA 上對設(shè)計(jì)進(jìn)行原型設(shè)計(jì)的過程不僅有助于驗(yàn)證目的,而且對于它為算法實(shí)驗(yàn)提供的可能性也很有用。如果算法的上下文可以在 FPGA 上復(fù)制,就像它出現(xiàn)在 ASIC 上一樣,則可以嘗試任意數(shù)量的算法實(shí)現(xiàn),并在面積效率、電流消耗或速度方面進(jìn)行比較。快樂的原型制作!

精彩推薦 至芯科技-FPGA就業(yè)培訓(xùn)來襲!你的選擇開啟你的高薪之路!3月28號北京中心開課、歡迎咨詢! 使用數(shù)字電源模塊為 FPGA 供電 FPGA設(shè)計(jì)工程師努力的方向?數(shù)字IC設(shè)計(jì)師常見面試題!掃碼加微信邀請您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個(gè)在看你最好看

原文標(biāo)題:如何使用 FPGA 測試 PLL 頻帶校準(zhǔn)算法

文章出處:【微信公眾號:FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603050

原文標(biāo)題:如何使用 FPGA 測試 PLL 頻帶校準(zhǔn)算法

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

膜厚測試儀的使用方法 膜厚測試儀的校準(zhǔn)步驟

絕緣電阻測試儀的校準(zhǔn)方法 絕緣電阻測試儀的工作原理

DL-T 1153-2012繼電保護(hù)測試儀校準(zhǔn)規(guī)范

密封測試儀的校準(zhǔn)和維護(hù):你做對了嗎

PLL1705/PLL1706雙通道PLL多時(shí)鐘發(fā)生器數(shù)據(jù)表

FPGA能實(shí)現(xiàn)什么樣的算法?

上海和晟 HS-TH-3500 炭黑含量測試儀校準(zhǔn)證書

基于FPGA的常見的圖像算法模塊總結(jié)

FPGA的時(shí)鐘電路結(jié)構(gòu)原理

FPGA片內(nèi)PLL電磁抗擾度的熱應(yīng)力效應(yīng)研究與測試分析

fpga驗(yàn)證和測試的區(qū)別

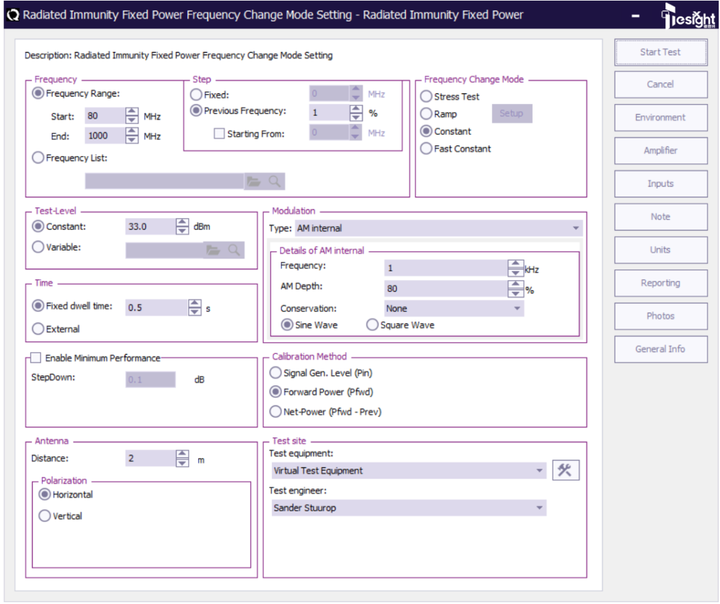

如何使用EMC測試軟件執(zhí)行輻射抗擾度測試?(二)測試、校準(zhǔn)方法及調(diào)制

如何使用 FPGA 測試 PLL 頻帶校準(zhǔn)算法

如何使用 FPGA 測試 PLL 頻帶校準(zhǔn)算法

評論