一個簡單的8位處理器完整設計過程及verilog代碼,適合入門學習參考,并含有作者個人寫的指令執(zhí)行過程。

1. CPU定義

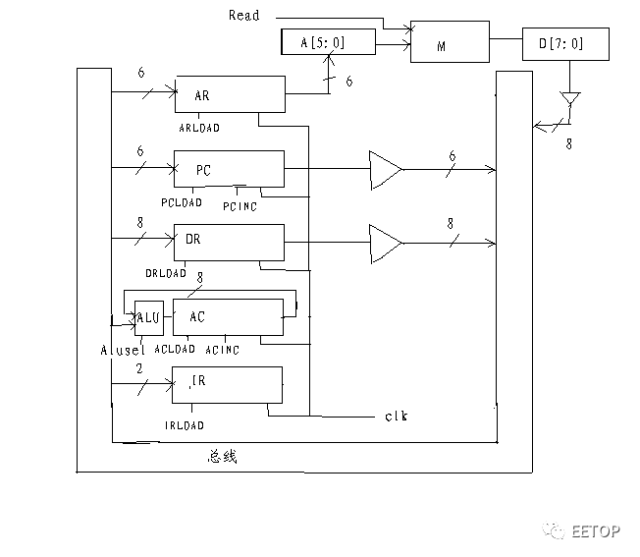

我們按照應用的需求來定義計算機,本文介紹一個非常簡單的CPU的設計,它僅僅用來教學使用的。我們規(guī)定它可以存取的存儲器為64byte,其中1byte=8bits。所以這個CPU就有6位的地址線A[5:0],和8位的數據線D[7:0]。

我們僅定義一個通用寄存器AC(8bits寄存器),它僅僅執(zhí)行4條指令如下:

| Instruction | Instruction Code | Operation |

| ADD | 00AAAAAA | AC<—AC+M[AAAAAA] |

| AND | 01AAAAAA | AC<—AC^M[AAAAAA] |

| JMP | 10AAAAAA | GOTO AAAAAA |

| INC | 11XXXXXX | AC<—AC+1 |

除了寄存器AC外,我們還需要以下幾個寄存器:

地址寄存器A[5:0],保存6位地址。

程序計數器PC[5:0],保存下一條指令的地址。

數據寄存器D[7:0],接受指令和存儲器來的數據。

指令寄存器IR[1:0],存儲指令操作碼。

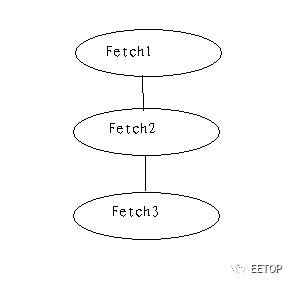

2.取指設計

在處理器執(zhí)行指令之前,必須從存儲器取出指令。其中取指執(zhí)行以下操作:

1〉通過地址端口A[5:0]從地址到存儲器

2〉等待存儲器準備好數據后,讀入數據。

由于地址端口數據A[5:0]是從地址寄存器中讀出的,所以取指第一個執(zhí)行的狀態(tài)是

Fetch1: AR<—PC

接下來cpu發(fā)出read信號,并把數據從存儲器M中讀入數據寄存器DR中。同時pc加一。

Fetch2: DR<—M,PC<—PC+1

接下來把DR[7:6]送IR,把DR[5:0]送AR

Fetch3: IR<—DR[7:6],AR<—DR[5:0]

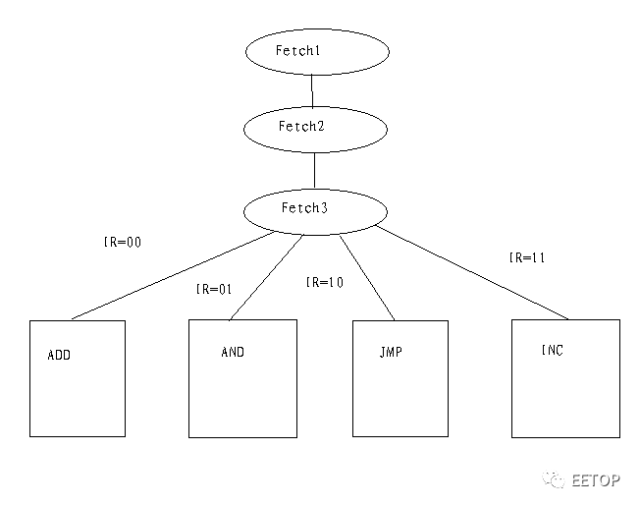

3.指令譯碼

Cpu在取指后進行譯碼一邊知道執(zhí)行什么指令,對于本文中的CPU來說只有4條指令也就是只有4個執(zhí)行例程,狀態(tài)圖如下:

4.指令執(zhí)行

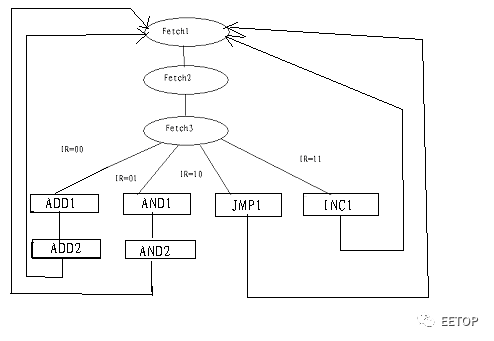

對譯碼中調用的4個例程我們分別討論:

4.1 ADD指令

ADD指令需要CPU做以下兩件事情:

1〉從存儲器取一個操作數

2〉把這個操作數加到AC上,并把結果存到AC

所以需要以下操作:

ADD1:DR<—M

ADD2:AC<—AC+DR

4.2 AND指令

AND指令執(zhí)行過程和ADD相似,需要以下操作:

AND1:DR<—M

AND2:AC<—AC^DR

4.3 JMP指令

JMP指令把CPU要跳轉的指令地址送PC,執(zhí)行以下操作

JMP1: PC<—DR[5:0]

4.4INC指令

INC指令執(zhí)行AC+1操作

INC1: AC<—AC+1

總的狀態(tài)圖如下:

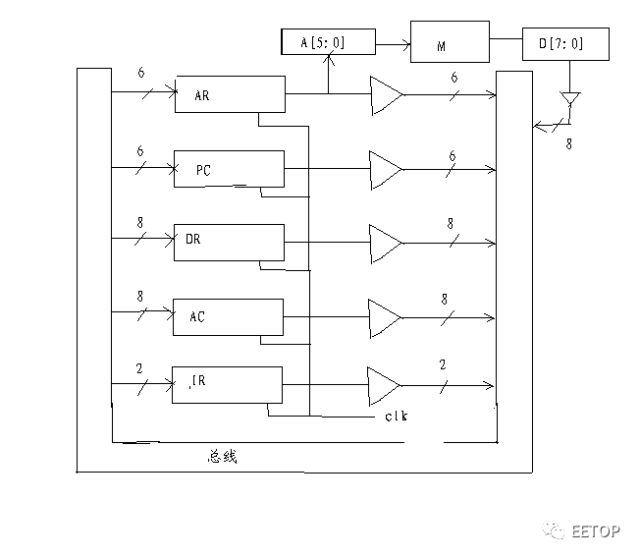

5 建立數據路徑

這一步我們來實現狀態(tài)圖和相應的寄存器傳輸。首先看下面的狀態(tài)及對應的寄存器傳輸:

Fetch1: AR<—PC

Fetch2: DR<—M,PC<—PC+1

Fetch3: IR<—DR[7:6],AR<—DR[5:0]

ADD1:DR<—M

ADD2:AC<—AC+DR

AND1:DR<—M

AND2:AC<—AC^DR

JMP1: PC<—DR[5:0]

INC1: AC<—AC+1

為了設計數據路徑,我們可以采用兩種辦法:

1〉創(chuàng)造直接的兩個要傳輸組件之間的直接路徑

2〉在CPU內部創(chuàng)造總線來傳輸不同組件之間的數據

首先我們回顧一下可能發(fā)生的數據傳輸,以便確定各個組件的功能。特別的我們要注意把數據載入組件的各個操作。首先我們按照他們改變了那個寄存器的數據來重組這些操作。得到如下的結果:

AR:AR<—PC;AR<—DR[5:0]

PC:PC<—PC+1;PC<—DR[5:0]

DR:DR<—M

IR:IR<—DR[7:6]

AC:AC<—AC+DR;

AC<—AC^DR;

AC<—AC+1

現在我們來看每個操作來決定每個組件執(zhí)行什么樣的功能,AR,DR,IR三個組件經常從其他的組件載入數據(從總線),所以只需要執(zhí)行一個并行輸入的操作。PC和AC能夠載入數據同時也能夠自動加一操作。

下一步我們把這些組件連接到總線上來,如圖所示:

如上圖所示,各個組件與總線之間通過三態(tài)連接,防止出現總線競爭。AR寄存器送出存儲器的地址,DR寄存器用于暫存存數起來的數據。到現在為止我們還沒有討論有關的控制信號,我們現在只是保證了所有的數據傳輸能夠產生,我們將在后面章節(jié)來使這些數據傳輸正確的產生---控制邏輯。

現在我們來看以下者寫數據傳輸中有沒有不必要的傳輸:

1〉 AR僅僅提供數據給存儲器,所以他不需要連接到總線上。

2〉 IR不通過總線提供數據給任何組件,所以他可以直接輸出到控制單元(后面章節(jié))。

3〉 AC不提供數據到任何的組件,可以不連接到總線上。

4〉總線是8bit寬度的,但是有些傳輸是6bit或者2bit的,我們必須制定寄存器的那幾位送到總線的那幾位。

5〉 AC要可以載入AC和DR的和或者邏輯與的值,數據路徑中還需要進行運算的ALU。

由此我們做以下工作:

1〉去掉AR,IR, AC與總線的連接。

2〉我們約定寄存器連接是從總線的低位開始的。AR,PC連接到Bus[5:0],由于IR是接受DR[7:6]的,所以可以連接到總線的Bus[7:6]。

3〉我們設定,AC作為ALU的一個輸入,另一個輸入來自總線Bus。

下面我們檢查是否有爭用總線的情況,幸運的是這里沒有。修改后的CPU內部組織圖如下:

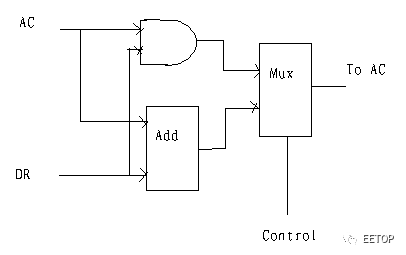

6. ALU設計

這個CPU的ALU執(zhí)行的功能就是兩個操作數相加、邏輯與。這里不作詳細介紹。電路如如下:

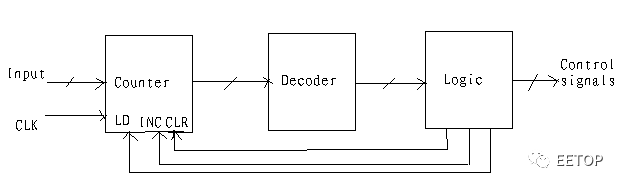

7. 控制單元

現在我們來考慮如何產生數據路徑所需的控制信號,有兩種方法:硬布線邏輯和為程序控制。這里我們用硬布線邏輯來實現。

這個簡單的CPU需要的控制邏輯由三個部件組成:

1〉計數器:用于保存現在的狀態(tài)

2〉譯碼器:生成各個狀態(tài)的控制信號

3〉其他的組合邏輯來產生控制信號

一個通用的控制單元原理圖如下:

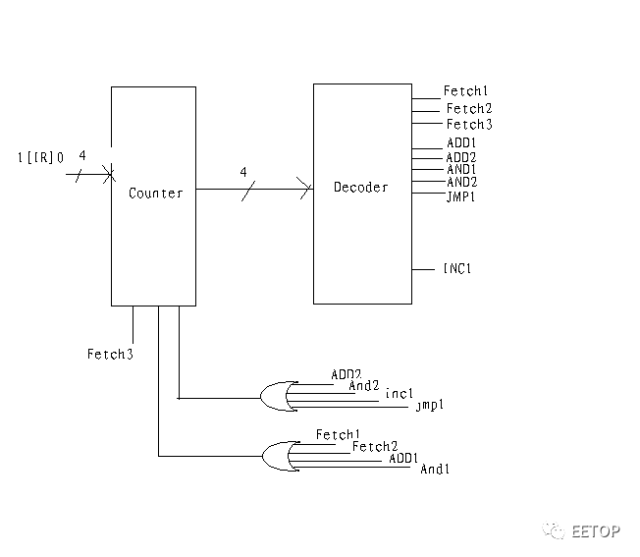

對于這個CPU來說,一共有9個狀態(tài)。所以需要一個4bit的計數器和一個4-16的譯碼器。接下來的工作就是按照前面的狀態(tài)轉換圖來對狀態(tài)進行賦值。

首先考慮如何的對譯碼輸出狀態(tài)進行賦值才能達到最佳狀態(tài)。我們按照以下規(guī)則:

1〉給Fetch1賦計數器的0值,并用計數器的清零端來達到這個狀態(tài)。由這個CPU的狀態(tài)圖可以看出,除了Fetch1狀態(tài)外的狀態(tài)都只能由一個狀態(tài)轉化而來,Fetch1需要從4個分支而來,這4個分支就可以發(fā)出清零信號(CLR)來轉移到Fetch1。

2〉把連續(xù)的狀態(tài)賦連續(xù)的計數器值,這樣就可以用計數器的INC輸入來達到狀態(tài)的轉移。

3〉給每個例程的開始狀態(tài)賦值時,要基于指令的操作碼和這個例程的最大狀態(tài)數。這樣就可以用操作碼來生成計數器的LD信號達到正確的狀態(tài)轉移。首先,在Fetch3狀態(tài)發(fā)出LD信號,然后要把正確的例程地址放到計數器的輸入端。對這個CPU來說,我們考慮以地址1 [IR] 0作為計數器的預置輸入。則得到狀態(tài)編碼如下:

| Instruction | State | IR | counter |

| Fetch | Fetch1 | 0000 | |

| Fetch2 | 0001 | ||

| Fetch3 | 0010 | ||

| ADD | ADD1 | 00 | 1000 |

| ADD2 | 00 | 1001 | |

| AND | AND1 | 01 | 1010 |

| AND2 | 01 | 1011 | |

| INC | INC1 | 10 | 1100 |

| JMP | JMP1 | 11 | 1110 |

如上表所示,下面我們需要設計產生計數器的LD、INC、CLR等信號,總的控制單元的邏輯如下圖:

下面我們用這些譯碼信號來產生數據路徑控制所必需的AR、PC、DR、IR、M和ALU的控制信號。首先考慮寄存器AR,他在Fetch1狀態(tài)取PC的值,并在Fetch3狀態(tài)取DR[5:0]的值,所以我們得到ARLOAD=Fetch1 or Fetch3。以此類推我們可以得到如下結果:

PCLOAD=JMP1

PCINC=Fetch2

DRLOAD=Fetch1or ADD1 or AND1

ACLOAD=ADD2 or AND2

IRLOAD=Fetch3

對于ALU的控制信號ALUSEL是用來控制ALU做邏輯或者算數運算的,所以有:

ALUSEL=AND2

對于片內總線的控制較為復雜,我們先來看DR,對于DR他只在Fetch3、AND2 、ADD2和JMP1狀態(tài)占用總線進行相信的數據傳輸,所以有:

DRBUS=Fetch3 or AND2 or ADD2 or JMP1

其他類似有:

MEMBUS=Fetch2or ADD1 or AND1

PCBUS=Fetch1

最后,控制單元需要產生存儲器的讀信號(READ),它發(fā)生在Fetch2、ADD1、AND1三個狀態(tài):

READ=Fetch2or ADD1 or AND1

這樣我們得到了總的控制邏輯,完成了整個CPU的設計。

8.設計驗證

我們執(zhí)行如下指令進行設計驗證,

0:ADD4

1:AND5

2:INC

3:JMP0

4:27H

5:39H

指令執(zhí)行過程如下(初始化所有寄存器為全零態(tài)):

| Instruction | State | Active Signals | Operations | Next State |

| ADD 4 | Fetch1 | PCBUS、ARLOAD | AR<—0 | Fetch2 |

| Fetch2 |

READ、MEMBUS DRLOAD、PCINC |

DR<—04H PC<—PC+1 |

Fetch3 | |

| Fetch3 |

DRBUS、ARLOAD IRLOAD |

IR<—00 AR<—04H |

ADD1 | |

| ADD1 |

READ、MEMBUS DRLOAD |

DR<—27H | ADD2 | |

| ADD2 | DRBUS、ACLOAD | AC<—0+27H | Fetch1 | |

| AND 5 | Fetch1 | |||

| Fetch2 | ||||

| Fetch3 | ||||

| ADD1 | ||||

| ADD2 | ||||

| INC | Fetch1 | |||

| Fetch2 | ||||

| Fetch3 | ||||

| INC1 | ||||

| JMP 0 | Fetch1 | |||

| Fetch2 | ||||

| Fetch3 | ||||

| JMP1 |

審核編輯:湯梓紅

-

處理器

+關注

關注

68文章

19882瀏覽量

234933 -

寄存器

+關注

關注

31文章

5433瀏覽量

124318 -

Verilog

+關注

關注

29文章

1367瀏覽量

112214 -

指令

+關注

關注

1文章

616瀏覽量

36418 -

代碼

+關注

關注

30文章

4899瀏覽量

70636

原文標題:一個簡單的8位處理器完整設計過程及verilog代碼

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

新戰(zhàn)局,解析64位處理器以及未來發(fā)展趨勢

32位嵌入式處理器與8位處理器應用開發(fā)的區(qū)別

詳細解析32位嵌入式處理器與8位處理器應用開發(fā)的不同之處

32位處理器可以裝64位系統嗎 32位處理器能否裝64位系統分析

32位處理器的開發(fā)與8位處理器的開發(fā)有哪些明顯的不同?

Intel 32位處理器 ,Intel 32位處理器結構原理

Intel 64位處理器,Intel 64位處理器結構原理

AMD 32位處理器,AMD 32位處理器有哪些系列?

“硬件軟件化”,32位處理器的開發(fā)與8位處理器的開發(fā)資料下載

到底64位處理器和32位處理器有什么區(qū)別呢?資料下載

評論