寄存器傳輸級(RTL)開發者經常并不清楚自己的芯片設計方案將會對功耗、性能和面積(PPA)產生怎樣的影響。要是能早早掌握這些信息,情況會怎樣呢?RTL設計的開發方式會因此發生怎樣的變化?這會對產品的價值帶來什么樣的影響?

一般來說,很多RTL開發者對物理實現過程知之甚少。他們一旦開發出模塊,完成后就將模塊交給實現團隊進行整合。但對于設計的PPA目標而言,很可能有另一套更優的算法或架構方案。而等到物理實現開發者發現這些影響時,往往已經來不及再對RTL進行有意義的變更。此外,實現報告幾乎不能為RTL開發者提供如何突破PPA瓶頸的指導。

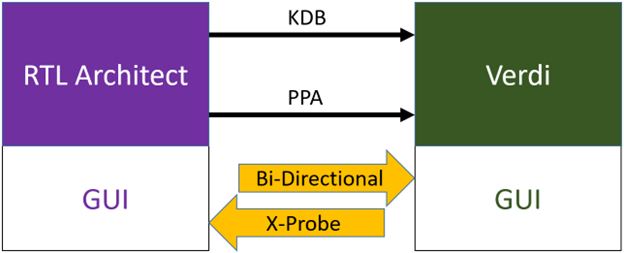

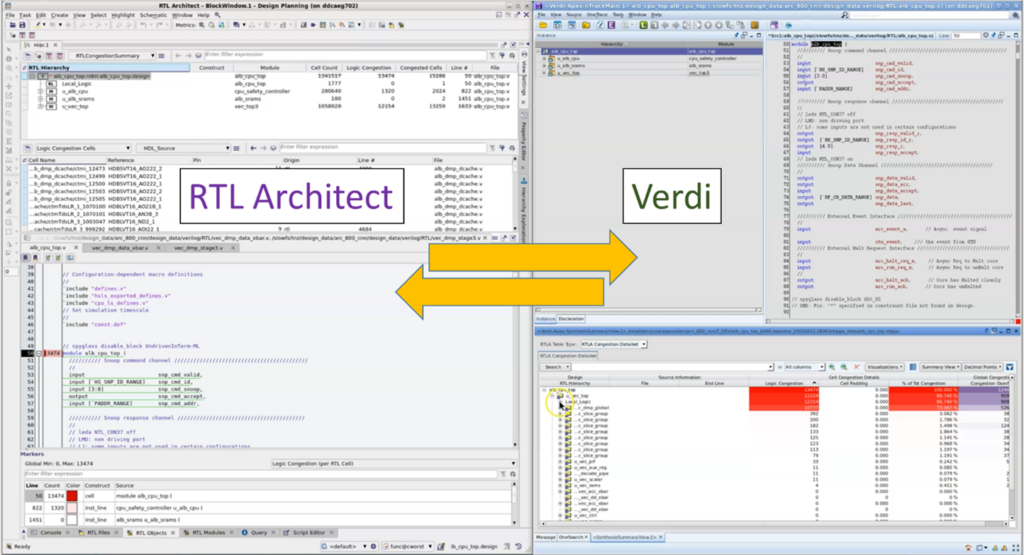

現在,有一種方法可以讓RTL開發者在熟悉的環境中調試相關問題,并在芯片設計的早期階段做出有效的變更。新思科技RTL Architect物理感知RTL分析、探索和優化系統與其市場領先的Verdi自動調試系統相集成,在一個大多數RTL開發者都非常熟悉的環境中提供了這些洞見。本文將進一步介紹這種工具集成給開發者帶來了怎樣的全新“超能力”。

PPA不必等RTL設計完成再考慮????????

RTL開發者總是以驗證為中心,他們多數都擁有前端RTL和驗證方面的專業知識,但很少有人懂得后端綜合和布局布線。RTL開發者往往專注于構建功能RTL,對其進行仿真,從而確保代碼按預期運行。他們向來認為完整綜合屬于后端問題。PPA和代碼問題的解決通常都會放到設計流程的后期。直到現在,RTL開發者還沒有一種工具或方法可以將PPA反饋并整合進自己的RTL設計工具包。

如果沒有辦法探索和了解塊級RTL對分區、子芯片或芯片等更高層級的影響,也就無法通過簡單的方式來快速執行增量式RTL綜合。因此,只有等到數星期乃至數月后,當RTL被移交給物理芯片設計團隊進行實現時,問題才可能被發現。到那時,往往很難通過改變設計來改善PPA,變更設計會破壞測試、時序和功耗約束。所以,改善PPA的工作只好交給后端團隊。但是,等到布局布線階段再來改善PPA,不僅會導致PPA增益變小,還會讓運行時間變長。對于先進節點,由于必須遵守大量的代工規則,移動單元和線路會更加困難,因此要想在實現過程中提升PPA,挑戰性也會更大。

另一種常見的情況是在RTL綜合時保留較大的裕量。這時,在RTL設計進入布局布線階段后,后端開發者必須解決裕量過大的問題,并采用優化技術來達到其PPA要求。另外,芯片設計流程越到后面,任何變更所能產生的影響也就越小。因此,這種方法并不能對設計產生有意義的影響,也不能讓開發者以恰當的方式靈活地定位他們的產品。

物理優化RTL,收斂速度高達5倍

PPA表現更佳

RTL Architect與Verdi平臺的集成,讓RTL開發者能夠盡早地解決問題,而不必等到實現團隊去發現。這將對PPA產生更大的影響,同時縮短實現所需時間。

RTL Architect是業界首個集成了簽核技術的物理感知RTL分析、探索和優化系統。該解決方案采用一個快速、多維實現預測引擎來預測PPA和RTL變化的擁塞影響。集成Verdi系統后,RTL開發者可以在熟悉的環境中解決PPA瓶頸問題。RTL Architect會在后臺進行預測性綜合和實現,并提供相關報告,因此RTL開發者不需要具備物理設計方面的背景,就能獲得所需結果。

具體的工作流程如下:

- RTL Architect執行快速、預測性綜合和實現。

- RTL用戶啟動Verdi調試環境,然后從RTL Architect讀取RTL和PPA數據。

- Verdi系統顯示一個支持排序/篩選的高級表格,如基于時序的最差模塊、最差功耗和最嚴重擁塞。該表按層次和結構/線路匯總了時序、功耗和擁塞的指標數據。因此,RTL開發者可以輕松查看一些信息,比如某個特定case語句的功耗,或者某個特定塊引起的總擁塞情況。

- 熟悉Verdi環境的RTL開發者可以看到其RTL的各種PPA指標,并根據這個眾所周知的設置進行修改。

- 完成RTL代碼修改后,RTL開發者可以再次使用RTL Architect來分析時序、功耗和擁塞情況。

總的來說,這兩個解決方案的集成在綜合/實現開發者和RTL開發團隊之間搭建了一個極好的溝通橋梁。PPA數據庫可以輕松實現共享,以便向RTL開發者提供各種實現質量指標。

▲RTL Architect與Verdi的雙向鏈路

除了提升PPA表現外,RTL Architect與Verdi環境的集成還能夠減少RTL的移交量,與傳統的綜合和后端芯片設計流程相比,開發進度加快了3到5倍。統一的GUI工作臺為各團隊提供了層次結構、布局、單元和RTL代碼的多層次視圖。無論RTL開發者是要定位時序瓶頸,發現功耗問題,識別邏輯或布局造成的擁塞,還是要優化平面圖,他們都可以在自己熟悉的Verdi環境中完成。

要想進一步了解該解決方案,請掃描以下二維碼注冊,觀看完整演示。

隨著半導體領域的競爭持續升溫,RTL開發者再也不能忽視其設計方案對PPA的影響。RTL Architect與Verdi環境的集成提供了一種簡單的方法,讓開發者可以更早地發現PPA問題,進而解決這些問題,提高產品整體性能并加快RTL收斂。

-

新思科技

+關注

關注

5文章

796瀏覽量

50334

原文標題:RTLA+Verdi:打造開發者全新超能力,提前“看到”PPA表現

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

開發者洞察 | 小德智能:用涂鴉GenAI能力打造智能寵物創新應用

云端AI開發者工具怎么用

HarmonyOS NEXT應用元服務開發Intents Kit(意圖框架服務)事件推薦開發者測試

蘋果發布Apple Intelligence開發者測試版

宣布 RISE RISC-V 開發者表彰試點計劃:賦能開發者拓展 RISC-V 影響力

ADI發布嵌入式軟件開發環境CodeFusion Studio?和開發者門戶,助力簡化和加速智能邊緣開發

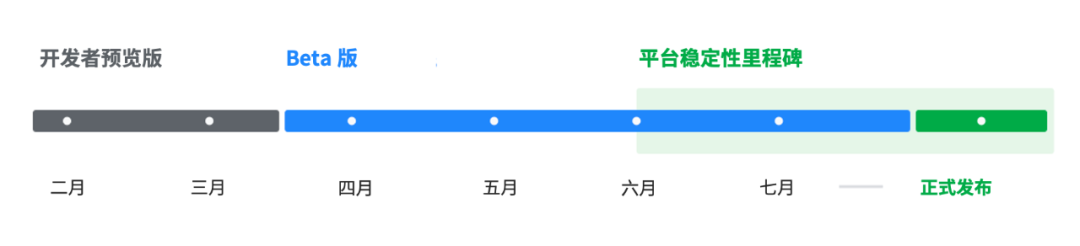

KaihongOS 4.1.2開發者預覽版正式上線,誠邀開發者免費試用!

KaihongOS 4.1.2開發者預覽版正式上線,誠邀開發者免費試用!

開發者空間實踐指導:基于 3 大 PaaS 主流服務輕松實現文字轉換語音

涂鴉智能借助亞馬遜云科技全面擁抱生成式AI打造智慧解決方案 提升開發者效率

愛立信旗下Vonage與AT&T合作,通過API為開發者提供更豐富的網絡能力

華為宣布HarmonyOS NEXT鴻蒙星河版開發者預覽面向開發者開放申請

RTLA+Verdi:打造開發者全新超能力,提前“看到”PPA表現

RTLA+Verdi:打造開發者全新超能力,提前“看到”PPA表現

評論