如今,PCI Express、HDMI 和 USB 等鏈接無處不在。但是在20年前不是這樣的。

在過去的 20 年里,串行鏈路應用的數量呈爆炸式增長。本文試圖解釋為什么串行鏈路(以及支持它們的 SerDes)變得如此流行。它將嘗試解釋使串行鏈路無處不在的一些底層技術,以及為什么 20 年過去了情況并非如此。

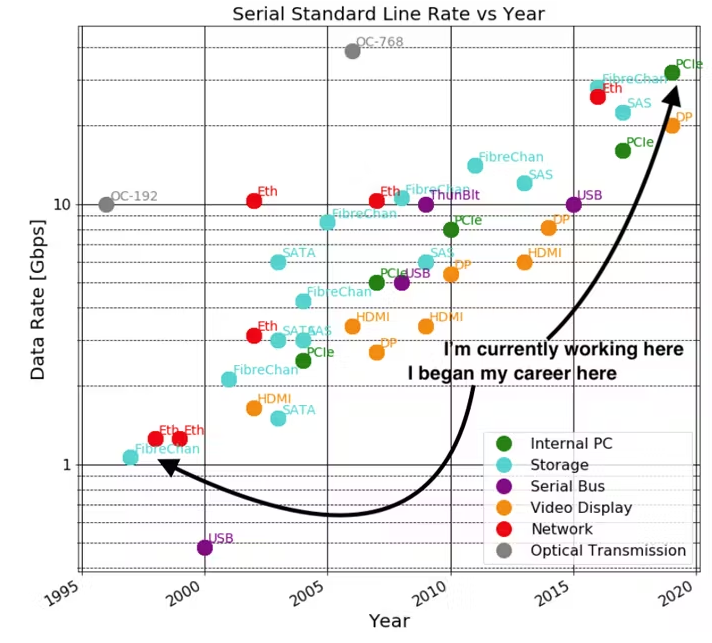

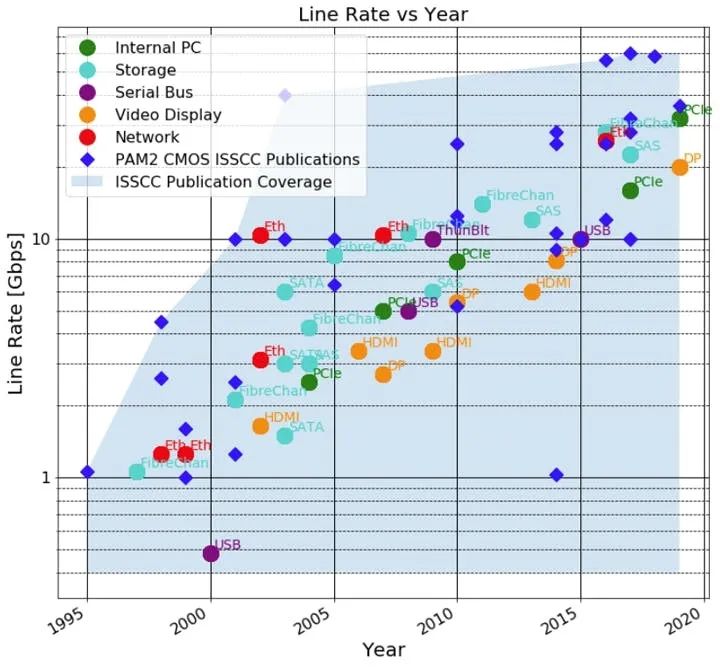

在本文中,將展示一些筆者所研究過的SerDes 的示例,并使用這些示例來幫助解釋設計和技術社區在過去二十年中取得的進步(圖 1 )。

圖1:SerDes在過去20年的轉變

起源與演變

SerDes 具有通過光纖和同軸鏈路進行通信的背景。原因很明顯,因為串行發送字節而不是并行發送字節限制了電纜的數量!對于一根或幾根電纜,最大化電纜的吞吐量是最重要的。SerDes 面積和功率是次要考慮因素。

在 20 世紀 80 年代中期,串行鏈路的數據速率在很大程度上是由電信要求 (SONET) 驅動的。在此期間,按照今天的標準(51.84 Mb/s、155.52Mb/s),對 OC-1 和 OC-3 的要求并不高。OC-24 需要高于 1 Gb/s (1244.16 Mb/s) 的線路速率,這在 1990 年左右得到了雙極(bipolar )和砷化鎵 (GaAs) 工藝中最先進電路的支持。

到了1990 年代后期,恰逢 SerDes 歷史上的一個重要時刻:OC-24 (2488.32 Mb/s) 可用,人們計劃以大約 10Gb/s 的速度使用 OC-192。幾年后(2000 年代初),通過 10 Gb/s 線路速率的 10 Gb 以太網成為現實(與 XAUI 相反,其中四個通道用于 10 Gb/s 聚合)。

另一個重要的發展開始了——SerDes 越來越多地用于 PCB 和背板上的“芯片到芯片”通信,以取代并行鏈路。這一發展將使 SerDes 從一個重要的長距離通信電路變成一個關鍵的 SoC 組件。也許最重要的例子是 PCIe,它于 2002 年左右以 2.5Gbps 的速度推出,并在 2000 年代中期流行起來。

各種串行數據標準的推出和 SerDes 的研究狀況如圖 1所示。他們包括:

光傳輸:OC-192、OC-768、SONET

PC內部:PCIe 1-5

串行總線:USB、Thunderbolt

視頻顯示:DisplayPort、HDMI

網絡:SGMII、1-Gb 以太網、10-Gb 以太網、25/100-Gb 以太網

正如預期的那樣,線路速率一直在以指數速度增長。跨類別可以看到相同的效果,光傳輸領先于其他類別。該圖僅包含 NRZ (PAM2) 標準。PAM4 標準正在以大約 50 Gb/s 的線路速率出現。

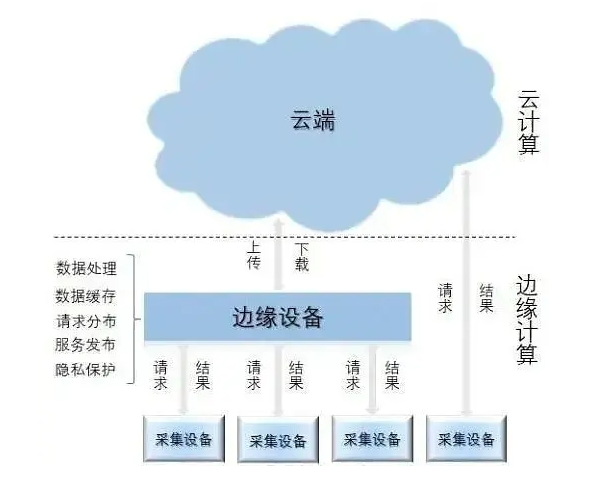

為了解支持 SerDes 發展的電路級創新,我使用 IEEE 的 Xplore 數字圖書館查詢了截止到2020年的國際固態電路會議 (ISSCC) 出版物,生成了涵蓋“時鐘和數據恢復”和“SerDes”的 ISSCC 出版物列表。然后將數據集分解為:

工藝類型:CMOS與非CMOS(雙極、biCMOS、HBT等)

工藝尺寸:65 nm、4 0 nm、7 nm等

信令:PAM2、PAM4

機構出版:工業、學術

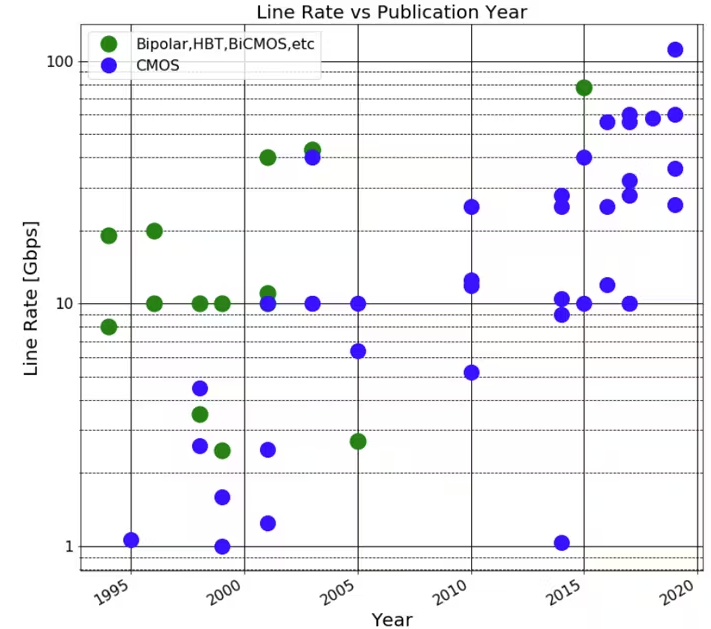

使用該數據集,根據出版年份繪制線率(圖 2)。據估計,這些電路的設計大約比出版提前了一年。然而,這些出版物的工業應用可能落后于該出版物數年。

圖2:線率是根據出版年份繪制

該圖顯示雙極、biCMOS 和 HBT 技術在 2005 年之前被廣泛發布,但在 2005 年之后很少發布。這些 2005 年之前的出版物描述了驅動光網絡應用的技術,其中線路速率和功率/形狀因數/整合是次要的考慮因素。

對于 PC、存儲、視頻顯示和網絡等容量大得多的 SerDes 應用,關鍵不僅僅是線路速率。重要的因素變成了成本、功耗、外形尺寸以及與大型數字內核的集成。

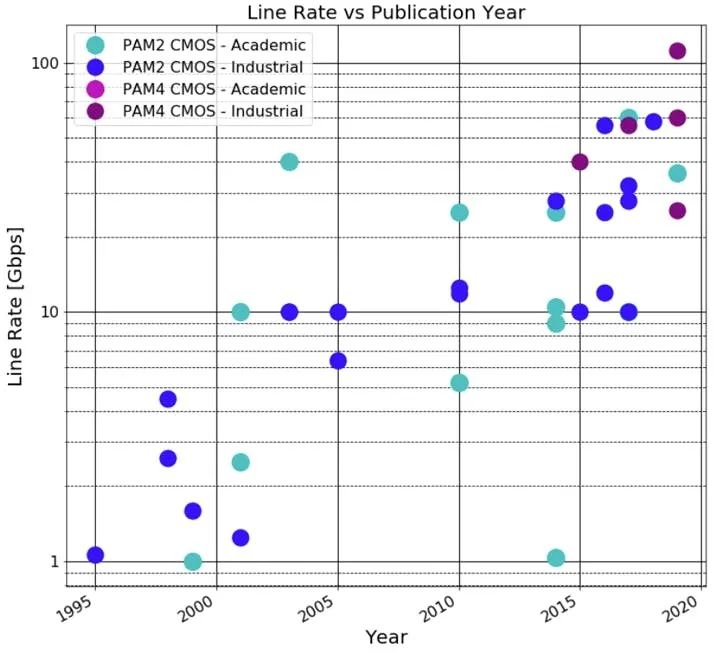

圖3中的圖表是通過統計ISSCC在 NRZ/PAM2 與 PAM4 信號方面的數據而排列。需要注意的一件事是,高于 28 Gb/s 線路比率的出版物趨向于 PAM4,而低于 28 Gb/s 的出版物幾乎沒有 PAM4。這與串行數據標準的預期未來方向非常吻合。

圖3:此圖是根據ISSCC的數據生成,涵蓋NRZ/PAM2與PAM4信令等

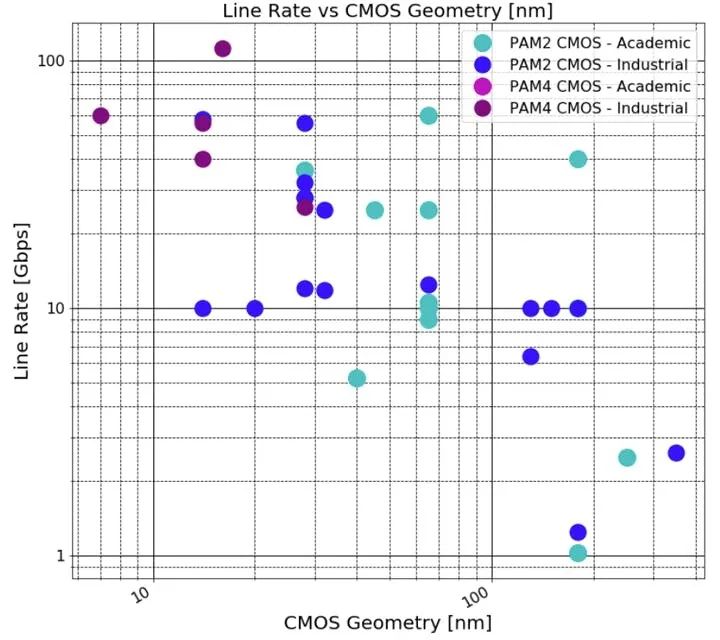

圖4顯示了線路速率與所用 CMOS 工藝尺寸的關系。可以看出 CMOS 工藝尺寸和線路速率之間的相關性。例如,在 90 nm 以下,大多數出版物都大于 10 Gb/s。此外,由于需要超越 NRZ/PAM2 SerDes 的高集成度(ADC、DSP)以及 CMOS 技術的高帶寬要求,因此 PAM4 系統在 28 nm 以上并不普遍開發或發布。

圖4:線路比率與CMOS尺寸的關系

在這些學術機構的出版物中明顯缺乏 PAM4 的相關文章。這部分歸因于我們使用的搜索條件。不過我們必須強調,有與 PAM4 組件相關的論文,但很少有學術界完成完整的 PAM4 收發器。對此的一種可能解釋是 PAM4 系統(ADC、DAC、DSP、PLL、CDR 等)非常復雜。另一種可能的解釋是 7 nm 和 14/16 nm 等先進 CMOS 工藝尺寸的成本和獲取成本。

結合串行鏈路出版物和串行數據速率標準的數據集,得出圖 5中的曲線圖。可以看出,ISSCC 的高級 CMOS 電路設計出版物在從網絡到顯示器的大容量串行數據標準方面領先了數年。PAM2 CMOS 研究使 PCIe1 到 PCIe5(32 Gb/s)、28-Gb/s 以太網線路速率等成為可能。

圖5,將串行鏈路出版物的數據集和串行數據速率標準組合起來創建的圖片

SerDes的優點

一、引腳數和通道優勢

SerDes 最明顯的優點是減少了引腳數和電纜/通道數。對于早期的 SerDes,這意味著可以通過同軸電纜或光纖發送數據字節。

對于現代 SerDes,另一個優勢是能夠通過一對差分信號引腳而不是 8、16、32 或 N 個數據引腳和一個時鐘引腳發送數據字節。由于更小的封裝和更密集的 PCB,序列化的這一方面可以節省成本。具體的優勢取決于裸片成本、封裝成本、PCB 成本、PCB 擁塞和其他因素。

二、距離優勢

在過去的十年中,SerDes 跨 PCB 和背板進行遠距離傳輸的能力幫助它們進入了許多新的領域。

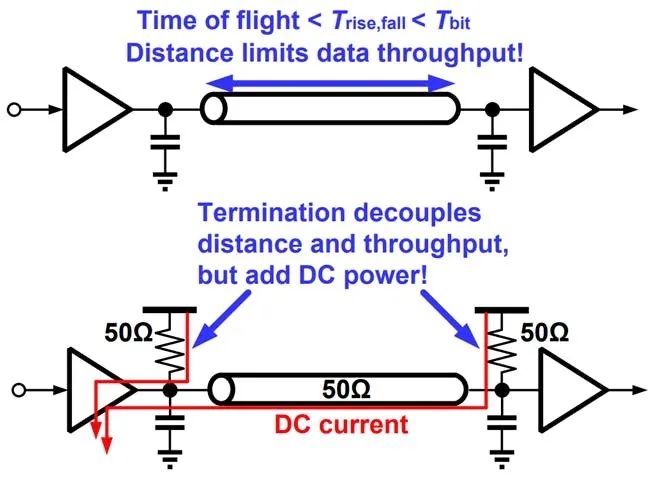

從基本的微波設計中,我們知道當飛行時間小于上升/下降時間時,傳輸線看起來像一個“集總元件”。對于帶有 GPIO 的并行接口,上升/下降時間通常不少于幾納秒。這將典型 PCB 上并行未端接口可以運行的距離設置為約 30 厘米。終止并行總線會增加覆蓋范圍;但與此同時,它會增加大量功率并使功率效率急劇下降(圖 6)。

圖6:雖然端接并行總線增加了覆蓋范圍,但電源效率急劇下降

SerDes 接口通常通過兩端(TX、RX)端接的受控阻抗傳輸線進行傳輸。這允許比特被快速傳輸而不用擔心反射。當然,要快速試下串行傳輸,會涉及很多額外的復雜性——例如串行器、解串器、TX PLL、RX CDR、前饋均衡、接收均衡等。

三、功耗優勢

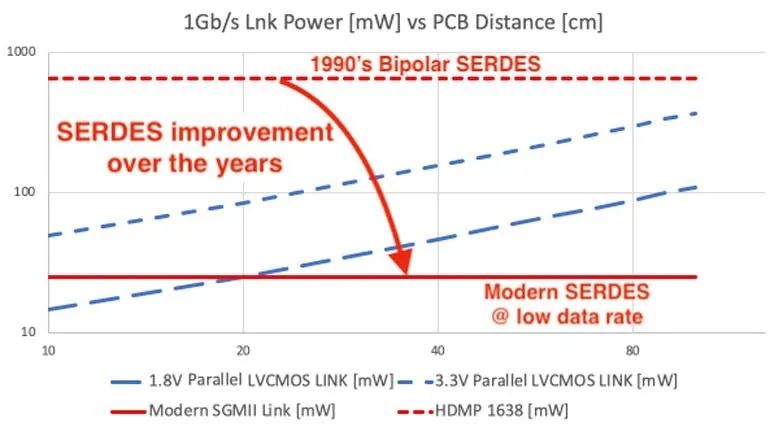

直到近年,SerDes 才擁有好于串行數據總線的功率優勢。理想的并行總線消耗的功率是用于對 TX 和 RX 電容以及走線電容進行充電和放電的功率。當考慮 10、20 或 100 厘米的距離時,走線電容(trace capacitance)在 FR4 上可能很重要。

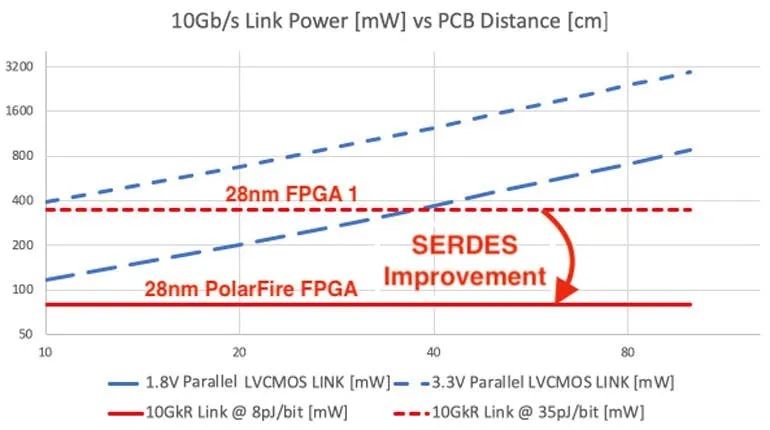

根據第一法則( first principles),我們知道 LVCMOS 鏈路的功率是 ~C*V^2*f。在數據的情況下,頻率是總比特率乘以轉換密度的二分之一。轉換的總數和功率與一階所需的通道數無關——通道越多,每條通道的轉換越少。對于 1-Gb/s 鏈路,10 cm 到 1 m 可能需要 8-16 條通道。對于 10-Gb/s 鏈路,1 m 可能需要非常不切實際的 120 條通道!

圖 7顯示了不同電壓的并行 LVCMOS 鏈路的功率與 SerDes 從 1990 年代到現在消耗的功率。可以看出,現代 SerDes 具有更長距離的功率優勢,但功率優勢尚不明確。

圖7,將不同電壓的并聯LVCMOS鏈路的功率與1990年代和今天的SerDes消耗的功率進行對比

SerDes 真正在功率方面大放異彩的地方是在更高數據速率的時候。圖 8顯示了不同電壓的并行 LVCMOS 鏈路的功率與 2010 年代中后期各種生產的 28 納米 SerDes 消耗的功率的關系。可以看出,現代 SerDes 幾乎在所有距離上都保持著功率優勢。對于功率優化的 SerDes,功率優勢在所有距離上都非常明顯。

圖8,不同電壓的并聯LVCMOS鏈路的功率與2010年代中后期各種28納米SerDes的功耗比較

隨著工藝技術的進步,SerDes 的功率優勢當然會繼續增長。

SerDes 挑戰

如上一節所述,SerDes 在功耗、引腳數和范圍方面具有引人注目的優勢。SerDes 的缺點是與 SerDes 相關的復雜性和成本。

一、復雜

至少,對于低數據速率,需要良好的 TX PLL、RX CDR、TX 驅動器和 RX 前端。其中每一個都是復雜的模擬子系統。設計這些塊和整個 SerDes 系統需要一個熟練的模擬/混合信號設計人員團隊來完成。這些模塊(連同復雜的數字控制)包括:

1、良好的 TX PLL:需要此模塊從典型的 25 至 100 MHz 參考時鐘產生典型的數千兆赫茲時鐘,并具有非常低(~1 ps 或更好)的長期抖動。

2、良好的 RX CDR:此塊是一個復雜的控制環路,用于追蹤輸入數據的平均相位,盡管鏈路上存在任何噪聲、失真或串擾。這通常使用復雜的相位旋轉器或 CDR 驅動的 PLL 來完成。

3、TX 線路驅動器:此模塊將串行化數據轉換為典型的 50 Ω 差分信號,通常帶有前導(precursor)和后光標(post-cursor)強調。

4、RX 均衡器:此塊嘗試使用連續時間均衡器或 DFE 或兩者來均衡高速通道效果。通常需要自動增益控制 (AGC) 電路來促進均衡。RX 均衡器通常包括作為狀態機邏輯或軟件的自動校準例程。

5、高速串行器和解串器邏輯

上面列出的所有模塊都需要經驗豐富的設計團隊花費大量的設計時間(。隨著數據速率的提高 (Gb/s) 和對效率的要求提高 (pJ/bit),這會增加 SerDes 的復雜性和成本。隨著可靠性要求的提高,必須運行和分析越來越多的老化和電遷移仿真,進一步推高了成本。

幸運的是,SerDes 已作為 IP 塊得到廣泛應用。因此,系統公司可以從領先的 IP 設計提供商那里獲得經過驗證的設計許可。通過這種方式,復雜性由專門的設計團隊處理,研發成本可以跨多個芯片、項目甚至行業分擔,有助于降低成本。

二、費用

SerDes 的主要費用來自設計(許多芯片設計師花了很多年)和驗證,但芯片面積和 PCB 面積等次要考慮因素也很重要。

PMA 級別的 SerDes 驗證通常由設計團隊或設計團隊的子集處理。在系統級別,驗證可能非常復雜,尤其是對于 PCIe 等標準。

對于復雜的串行標準,需要測試平臺(System Verilog 中的典型)從物理層(包括 PMA 和 PCS)、數據鏈路層、事務層和設備級別驗證系統。涵蓋這些級別的驗證通常檢查協議、模式、協商、錯誤注入和恢復等。驗證通常也需要許多人月,并且通常涉及第三方驗證 IP (VIP)。

在裸片上,SerDes 可能比并行接口更便宜或更昂貴。根據工藝節點的不同,SerDes 每條通道可能消耗大約 0.15 至 0.5 mm 2。并行接口可以比這小得多,但需要更多的 I/O。因此,根據芯片是 I/O 受限還是引腳受限,SerDes 可能會導致比并行接口更多或更少的裸片成本。

在封裝和 PCB 級別,SerDes 允許減少引腳和走線數量。因此,它們應該會導致更小、成本更低的封裝和 PCB 設計。然而,由于高速受控阻抗(例如 50 Ω)跡線的復雜性,使用 SerDes 的封裝和 PCB 的設計可能更加困難,因此比使用較慢的并行接口的 PCB 更昂貴。

寫在最后:SerDes緣何成為關鍵 IP?

我們已經看到,接口 IP 類別在過去 20 年中的增長率令人難以置信,我們預計該類別至少在未來 10 年內會產生持續的高 IP 收入來源。但是如果我們深入研究各種成功的協議,如 PCI Express、以太網或 USB,我們可以發現物理 (PHY) 部分的一個共同功能,即串行器/解串器 (SerDes) 功能。

1998 年,電信應用中使用的高級互連基于 622 MHz LVDS I/O。電信芯片制造商正在構建集成 256 個以 622 MHz 運行的 LVDS I/O 的巨大芯片,以支持網絡結構。今天,先進的 PAM4 SerDes 以 112 Gbps 的速度運行;通過單一連接支持 100G 以太網。二十年來,SerDes 技術效率躍升了 180 倍!

如果我們與 CPU 技術進行快速比較。1998年Intel發布了Pentium II Dixon處理器,頻率為300 MHz。2018 年,英特爾酷睿 i3 以 4 GHz 運行。在 20 年的時間里,CPU 頻率增長了 15 倍。最為對比,如上所述, SerDes 速度增長了 180 倍。

SerDes 現在不僅用于電信,還用于連接芯片和系統的更多應用。2000 年代末,智能手機集成了 USB3、SATA 和 HDMI 接口,而電信和 PC/服務器則集成了 PCIe 和以太網。這些趨勢導致接口 IP 市場成為一個規模龐大的 IP 類別,當時增長超過 2 億美元。與四五倍大的 CPU 類別相比,它很小。但是,自 2010 年以來,接口類別同比至少增長了 15%。與所有其他半導體 IP 類別(如 CPU、GPU、DSP、庫等)相比,它是增長最快的類別。原因與每年增長的連接設備數量直接相關,每個設備交換更多數據(更多電影和圖片等等),而連接是通信鏈的開始。

在 2010 年的那個十年間,全球社區幾乎完全連接在一起。隨著連接速率和數據中心數量在過去十年中迅速增加,以太網成為這種連接的支柱。如果我們使用 SerDes 速率作為指標,2010 年為 10 Gbps,2013 年為 28 Gbps,2016 年為 56 Gbps(允許分別支持 10G、25G 和 50G 以太網)和 2019 年為 112 Gbps。

然后,在 2017 年,機器學習和神經網絡等新興數據密集型計算應用開始出現爆炸式高速連接需求,增加了對高帶寬連接不斷增長的需求。同時,由于 CMOS 技術向高級 FinFET 的發展,模擬混合信號架構從一開始就成為 SerDes 設計的標準,變得極難管理并且對工藝、電壓和溫度變化更加敏感. 在現代FinFET納米 技術中,考慮到晶體管的微小尺寸,構建晶體管涉及堆疊單個電子。因此,構建能夠承受壓力環境變化的精密模擬電路極其困難。

但 7nm 等先進技術的積極意義在于,您可以按平方毫米集成數量驚人的晶體管(密度為每平方毫米 1 億個晶體管),因此現在可以利用數字信號處理開發新的基于數字的架構(DSP) 來完成物理層的絕大部分工作。與過去模擬混合信號方法使用的不歸零(NRZ 或 PAM2)相比,基于 DSP 的架構支持使用更高階的脈沖幅度調制 (PAM) 調制方案。PAM 4 使通道的數據吞吐量翻倍,而無需增加通道本身的帶寬。

例如,具有 28 GHz 帶寬的信道使用 NRZ 信令可以支持最大 56 Gbps 的數據吞吐量。通過使用 PAM-4 DSP 技術,這個相同的 28 GHz 帶寬通道現在可以支持 112 Gbps 的數據速率!當您考慮到模擬 SerDes 架構由于物理原因限制在最大 56 Gbps 的速率(可能更少...... .PAM-6 或 PAM-8)。

使用基于 DSP 的 SerDes 不僅是在 FinFET 技術中構建穩健接口所必需的,而且也是將數據速率加倍以達到 56 Gbps 以上的唯一方法,例如。使用 PAM-4 時為 112 Gbps,使用 PAM-8 時為 200 Gbps。

從市場的發展看來,Chiplet正在洶涌而至,從今年下半年開始,大多數先進的 SoC 也將采用 3nm 設計。這將使像 SerDes 這樣的高端 IP 的集成風險太大,導致將此功能外化到在更成熟的節點(如 7 或 5nm)中設計的Chiplet中。如果接口 IP 供應商將成為這場革命的主要參與者,那么解決臺積電和三星等最先進節點并制造主要 SoC 的硅晶圓代工廠將發揮關鍵作用。

我們不認為他們會設計小芯片,但他們可以決定支持 IP 供應商并推動他們設計小芯片以與 3nm SoC 一起使用,就像他們今天在支持高級 IP 供應商將其高端 SerDes 作為 7nm 和 5nm 硬 IP 進行營銷時所做的那樣。

毫無疑問,SerDes未來擁有很多的機會。

審核編輯 :李倩

-

神經網絡

+關注

關注

42文章

4771瀏覽量

100719 -

機器學習

+關注

關注

66文章

8407瀏覽量

132567 -

SerDes

+關注

關注

6文章

198瀏覽量

34906

原文標題:越來越重要的SerDes

文章出處:【微信號:IC學習,微信公眾號:IC學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

NXP公司電動汽車牽引逆變器解決方案

睡眠監測傳感器越來越重要,你怎么看?

我們的城市為什么越來越熱?

SolidWorks教育版在教學上的重要作用

嵌入式會越來越卷嗎?

IC datasheet為什么越來越薄了?

【行業科普】5個應用趨勢說明為什么“云-邊協同”越來越重要!

三防平板丨平板終端丨三防平板電腦丨建筑工地應用

越來越重要的SerDes

越來越重要的SerDes

評論