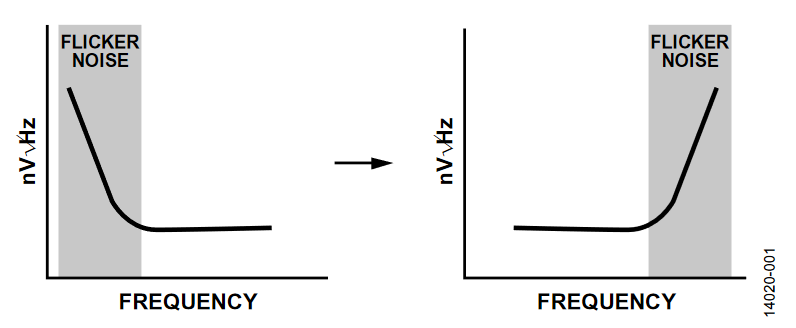

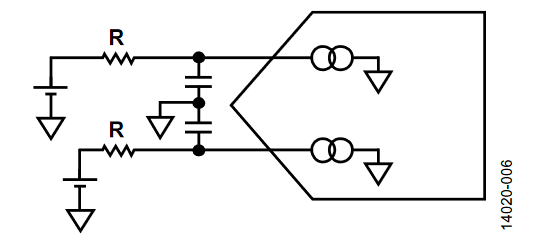

典型DPD應用模數轉換器(ADC)中集成的緩沖器和放大器通常是斬波型。有關這種斬波實現的例子,可參見AD7124-8 和AD7779數據手冊。需要這種斬波技術來最大程度地降低放大器的失調和閃爍噪聲(1/f ),因為與其他工藝(如雙極性工藝)相比,CMOS晶體管噪聲高,難以匹配。通過斬波,放大器的1/f和失調轉換到較高頻率,如圖1所示。

圖1. 閃爍噪聲(1/f )與斬波

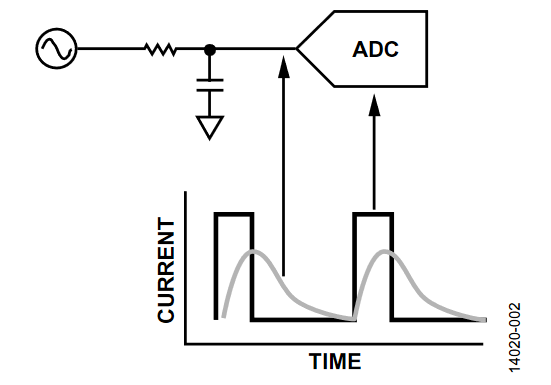

在斬波轉換過程中,開關的電荷注入會引起電流尖峰,進而使施加于ADC輸入端的電壓產生方向不定(流入和/或流出)的下降或尖峰。壓降與連接到ADC輸入段的傳感器的輸出阻抗成比例。

平均電流值一般而言,數據手冊不會提供電流峰值,因為它難以測量,而且不會增加任何有意義的信息。該信息之所以無意義,是因為緩沖器的斬波頻率高于ADC的輸入信號帶寬。因此,輸入引腳上添加的低通濾波器(用來消除高于奈奎斯特頻率的頻率或信號音,或用來降低耦合噪聲)會對峰值電流進行平均,如圖2所示。

圖2. 輸入電流與時間的關系

用電流表測量輸入電流,一端連接到VDD/2,另一端連接到ADC的模擬輸入引腳。

如果電流表連接到其中一個電壓軌,由于輸入電壓裕量的關系,測得的電流可能高于數據手冊中的規格值。

輸入電流與輸入阻抗的關系

輸入阻抗規格對精確計算直流誤差沒有幫助,因為與ADC內部輸入阻抗引起的負載效應相比,輸入偏置電流是最主要的貢獻因素。

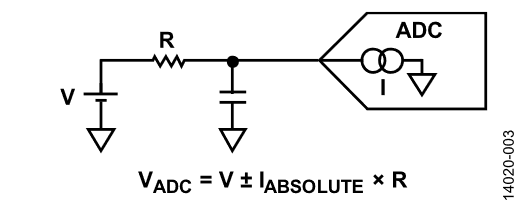

有兩個規格與輸入偏置電流相關:絕對電流和差分電流。絕對值(IABSOLUTE)是在任意模擬輸入引腳測得的輸入電流。差分輸入電流(IDIFFERENTIAL)是在模擬輸入引腳對之間測得的電流差。這僅適用于差分輸入ADC。

如何計算直流誤差輸入電流產生一個失調電壓(VOFFSET),后者與連接到輸入引腳的阻抗直接相關。

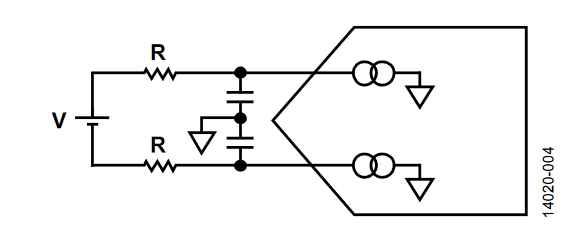

如圖3所示,產生的失調電壓一般為:

圖3. 漏電流引起的壓降

如果用運算放大器等低阻抗源驅動模擬輸入引腳,誤差將不很明顯。

ADC測得的誤差取決于施加的輸入信號類型,例如是真差分輸入信號還是偽差分/單端輸入信號。

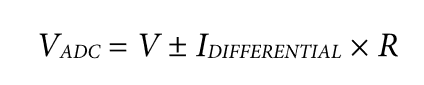

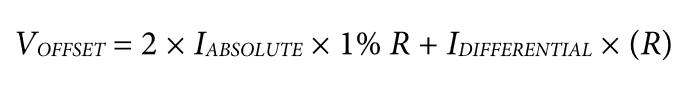

對于真差分輸入信號,假設輸入電阻(R)完全匹配,那么ADC測得的誤差將是由模擬輸入引腳對之間的差分輸入電流引起,如下式所示:

其中,VADC為ADC輸入電壓。

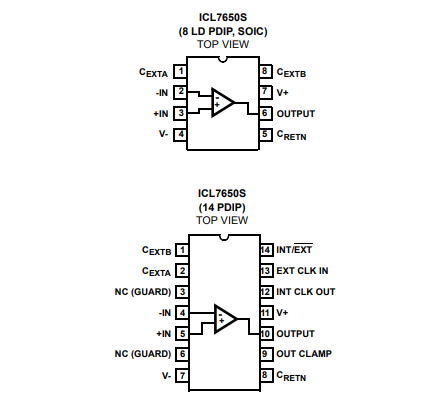

圖4. 差分輸入ADC

如果電阻不是完全匹配,則在差分輸入電流貢獻之外,電阻不匹配也會產生一個誤差。

一般而言,假設電阻容差為1%,那么最差情況下的失調電壓定義如下:

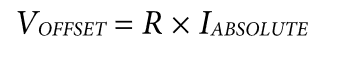

對于偽差分/單端輸入信號,有兩種情況:

-

一個模擬輸入連接到低阻抗源(參見圖5)。誤差定義為:

圖5. 偽差分/單端ADC

-

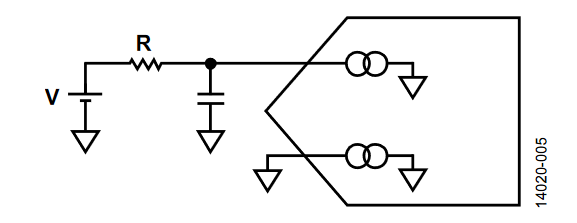

兩個輸入均連接到高阻抗源(參見圖6)。誤差與使用真差分信號的情況相同。

圖6. 偽差分ADC

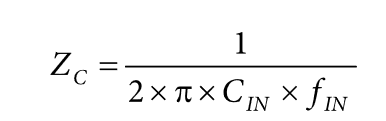

交流誤差交流分量與輸入阻抗規格直接相關。輸入阻抗可以是阻性或容性。若輸入阻抗為容性,則給定頻率下的阻抗計算如下:

其中:

Zc為輸入阻抗。

CIN為數據手冊給出的輸入電容。

fIN為輸入頻率。

舉個例子,假設有8 pF電容和1 kHz輸入帶寬,則最小輸入阻抗約為20 MΩ。

誤差最小化為使低通濾波器中電阻不匹配引起的誤差最小,最好使用小電阻和大電容,因為電阻產生的失調和約翰遜噪聲較低。

原文標題:如何計算集成斬波放大器的ADC失調誤差和輸入阻抗?

文章出處:【微信公眾號:亞德諾半導體】歡迎添加關注!文章轉載請注明出處。

-

亞德諾

+關注

關注

6文章

4680瀏覽量

16333

原文標題:如何計算集成斬波放大器的ADC失調誤差和輸入阻抗?

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

評論