背景

假設一種場景,在調試環境的時候,運行到15min的時候,環境出現bug,需要去debug。也許錯誤的第一現場并不是15min的時候,可能在14min30s-15min之間,那么如果正向執行就需要14min30s以上。所以這個時候如果能夠直接反向運行到14min30s,就可以節省很多時間。就像jojo的奇妙冒險中吉良吉影的招式,敗者食塵一樣,逆轉時間

編譯選項

要實現這個功能,依賴于VCS和VERDI的聯合調試,所以在編譯的時候需要使用下面的指令

vcs-full64-sverilog-ntb_optsuvm-1.2-lca-kdb-debug_access+reverse

除了常規的選項以外,-kdb選項是用于生成kdb數據庫,支持verdi的聯合調試,而lca是kdb的依賴選項。

最后的-debug_access+reverse則是最關鍵的開關,需要加上這個選項才是實現反向運行。

編譯完成以后,進行仿真的時候,需要使用./simv -verdi,啟動仿真。這樣就能夠直接調用verdi進行聯合仿真。

測試代碼

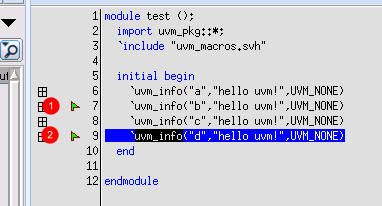

本次的測試代碼就是簡單的4行打印。

moduletest(); importuvm_pkg::*; `include"uvm_macros.svh" initialbegin `uvm_info("a","hellouvm!",UVM_NONE) `uvm_info("b","hellouvm!",UVM_NONE) `uvm_info("c","hellouvm!",UVM_NONE) `uvm_info("d","hellouvm!",UVM_NONE) end endmodule

reverse

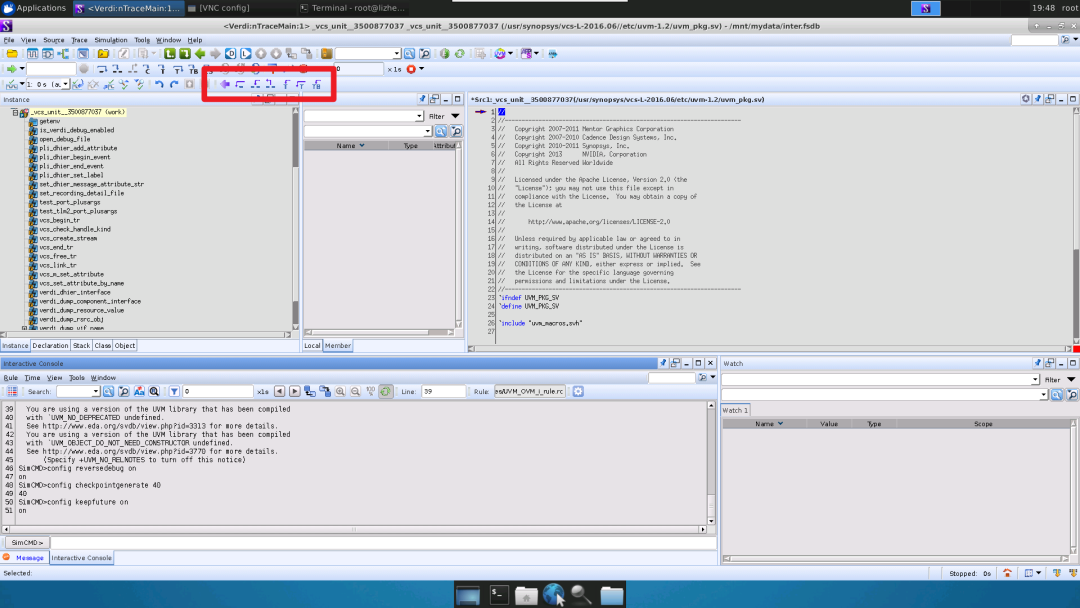

啟動verdi之后,注意圖中紅色框框中的一排按鈕,這就是reverse功能的按鈕。從圖標形狀來開,和聯合仿真的正向交互式仿真是一致,功能上他們其實也是對偶的。

reverse按鈕

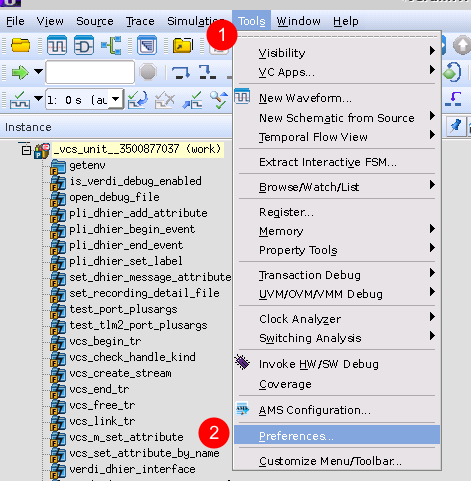

如果你開起了reverse選項,但是仍然沒有出現這一排按鈕,那么就需要在tools下的perferences中,開啟reverse按鈕。

perferences

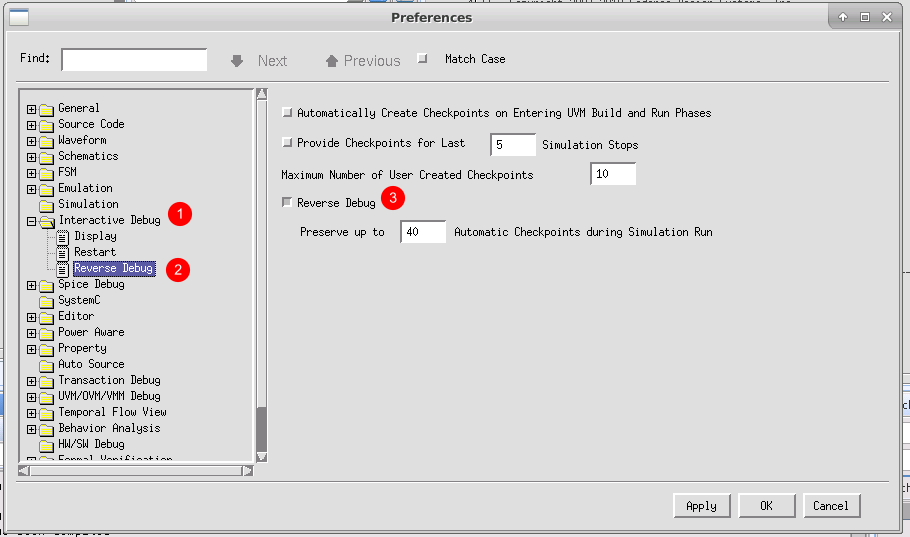

在perferences中的interactive debug下,找到reverse debug

reverse

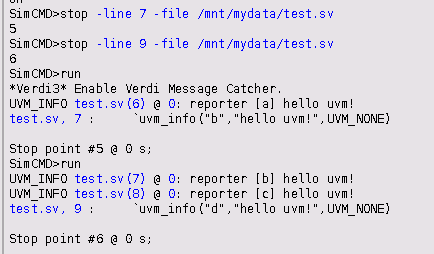

接下來可以在代碼中設置兩個斷點進行測試。直接單擊代碼左側即可甚至斷點。和C的單步調試是一樣的,直接run就能在斷點處停止。

設置斷點

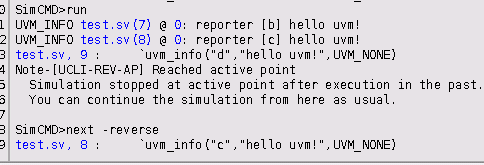

我們跑到第九行的斷點,可以看到中間在七行停止了一次,最后在第九行停下來,6 7 8行的信息都已經打印出來了。

前向運行

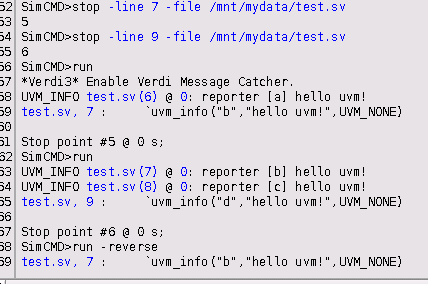

那么如果我們需要回到第七行,就可以直接進行點擊下圖中的run reverse按鈕。

run reverse

然后就能夠回到上一個斷點處

當然也可以,點擊旁邊的next reverse按鈕進行反向單步運行

反向單步

就能夠從第九行回到第八行

其他按鈕和這兩個類似,但是正向調試的反向版本。

本次分享了VCS+VERDI的reverse反向運行功能,可以將整個仿真反向運行,從而減少正向仿真的時間消耗。

當然,這必須在VCS+VERDI的聯合調試下才可以,如果是VCS單獨仿真,dump波形,再使用VERDI離線調試就不能使用。而聯合仿真也會大幅度降低運行速度,所以推薦在早期debug驗證環境的時候使用。

審核編輯:劉清

-

VCS

+關注

關注

0文章

79瀏覽量

9602 -

Verdi

+關注

關注

0文章

22瀏覽量

8775

原文標題:聯合仿真VCS+VERDI+Reverse,你會嗎?

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

請教VCS和verdi怎么聯合使用

怎樣去使用Makefile+VCS+Verdi做個簡單的Test Bench?

求大佬分享VCS/Verdi 2014或者2018版本的安裝包

VCS仿真卡住,為什么無法生成verdi波形文件呢?

在Linux上用vcs+verdi對demo_nice進行仿真沒有成功的原因?

vcs和verdi的調試及聯合仿真案例

利用vcs+verdi仿真工具蜂鳥E200系列處理器仿真分析

全網最實用的Verdi教程1

全網最實用的Verdi教程2

全網最實用的Verdi教程3

Verdi環境配置、生成波形的方法

VCS+VERDI的reverse反向運行功能

VCS+VERDI的reverse反向運行功能

評論